# Oxide-confined VCSELs fabricated with a simple self-aligned process flow

Ludovic Marigo-Lombart, Stéphane Calvez, Alexandre Arnoult, Hugo Thienpont, Krassimir Panajotov, Guilhem Almuneau

#### ▶ To cite this version:

Ludovic Marigo-Lombart, Stéphane Calvez, Alexandre Arnoult, Hugo Thienpont, Krassimir Panajotov, et al.. Oxide-confined VCSELs fabricated with a simple self-aligned process flow. Semiconductor Science and Technology, 2017, 32 (12), pp.125004. 10.1088/1361-6641/aa90ae. hal-01614784

### HAL Id: hal-01614784 https://laas.hal.science/hal-01614784v1

Submitted on 11 Oct 2017

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Oxide-confined VCSELs fabricated with a simple self-aligned process flow

L. Marigo-Lombart<sup>1,2</sup>, S. Calvez<sup>1</sup>, A. Arnoult<sup>1</sup>, H. Thienpont<sup>2</sup>, K. Panajotov<sup>2</sup> and G. Almuneau<sup>1</sup>

#### lmarigol@laas.fr

**Abstract :.** We propose a simplified and easier fabrication process flow for the manufacturing of AlOx-confined VCSELs based on combining the oxidation step with a self-aligned process, allowing the mesa etching and two successive lift-off steps based on a single lithography step. The electro-optical confinement achieved by standard lateral oxidation enables a low threshold and a single mode behaviour for the VCSEL. This simplified process can largely improve VCSEL manufacturing by reducing the processing time and costs compared to the standard VCSEL process.

Keywords: VCSEL, Self-aligned, oxidation

#### **Introduction:**

Vertical-cavity surface-emitting lasers (VCSEL) have become the preferred light sources in many photonic systems, enabling short-link interconnections [1] but also in other emerging mass-market applications like sensing and detection [2]. The large production volume of VCSELs would benefit from a simplification of the manufacturing process flow that may largely increase the cost-effectiveness.

Indeed, compared to the LED and LDs, the VCSEL fabrication process flow requires a large number of elementary steps defined by successive inter-aligned photolithography levels. A precision in the micron range is required to ensure the lateral alignment between the optical waveguide and the electrical injection. For these reasons, one of the most important concerns for the VCSEL manufacturers is to improve the production throughput by lowering the fabrication time and cost per wafer.

The development of a self-aligned process is of great interest as already demonstrated for the fabrication of high performance HBT transistors or ridge lasers [3,4]. To that extent, Al-Omari [5] used a top metallic contact deposited over a photoresist layer as a hard mask to dry-etch the VCSEL mesa. Chua [6] developed a pseudo-planar approach by opening via holes down to the AlAs layer to carry out the lateral oxidation. This process has subsequently been improved by Strzelecka [7] to increase the device density. Recently, we have shown that air-post VCSELs could be created using an innovative self-aligned process, which combined several masking and lift-off steps defined by a single lithographic step [8].

In this paper, we extend this work and propose a new process flow to fabricate, in a very simple and straightforward way, the widely-used oxide-confined VCSELs. The demonstrated process drastically simplifies the oxide-confined VCSEL fabrication by reducing the total number of lithographic alignment steps from four or more to only one alignment, with the additional advantage of relieving the required tolerances. This process flow, most suitable for 3D imaging and sensing applications, can also be easily implemented for the fabrication of other optoelectronic devices such as modulators, ridge waveguide lasers, detectors, solar cells or any process combining dry etch, passivation and metallization.

#### **Fabrication:**

The studied 980 nm VCSEL structure was grown by molecular beam epitaxy (MBE) with a Riber 412 reactor on a GaAs Si-doped substrate. It is composed of a 30.5 period  $Al_{0.9}Ga_{0.1}As/GaAs$  bottom N-doped Bragg reflector (DBR), a  $\lambda$ -thick active region consisting of 3 InGaAs/GaAs quantum wells surrounded by  $Al_{0.2}Ga_{0.8}As$  cladding layers, a 30 nm  $Al_{0.98}Ga_{0.02}As$  layer located in the first top-DBR period which will embed the oxide confined aperture, a 19.5 periods P-doped DBR and a GaAs top heavily P-doped contact layer.

<sup>&</sup>lt;sup>1</sup> LAAS-CNRS, Université de Toulouse, CNRS, Toulouse, France

<sup>&</sup>lt;sup>2</sup> Department of Applied Physics and Photonics (TW-TONA), Vrije Universiteit Brussel, Pleinlaan 2, B-1050 Brussels, Belgium

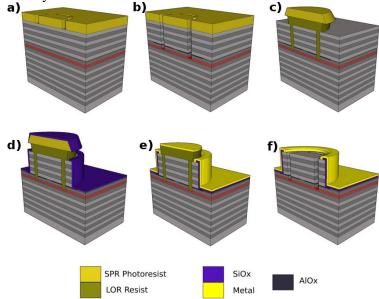

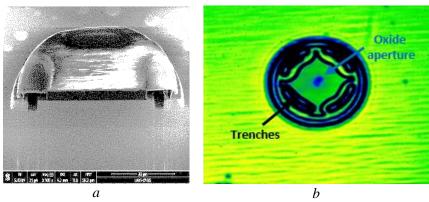

The fabrication process is schematically shown in Figure 1. The first step is to etch four 3- $\mu$ m-wide 37 $\mu$ m-diameter curved trenches of 26.5  $\mu$ m length to open an access to the buried Al<sub>0.98</sub>Ga<sub>0.02</sub>As layer, which, upon wet thermal oxidation, will lead to the definition of the lateral confinement aperture. To do so, a 2.3  $\mu$ m-thick SPR700 photoresist mask is applied in a first photolithography step (a), followed by the inductively coupled plasma etching (ICP-RIE) with a Cl<sub>2</sub>/N<sub>2</sub> gas mixture of the top DBR and active region (b). Then, the selective oxidation (c) of the Al<sub>0.98</sub>Ga<sub>0.02</sub>As layer is realized in a dedicated oven (AET Technologies) under N<sub>2</sub>/H<sub>2</sub>/H<sub>2</sub>O gas moisture at 410°C, reaching a 28- $\mu$ m size of the oxidized region after 70 minutes. The resulting oxide aperture is observed by near-infrared microscopy and is shown in Figure 2 b).

It exhibits an asymmetric shape of 4  $\mu m$  by 7  $\mu m$ , resulting from a non-uniformity of the etching step across the different trenches.

After this first sequence, a double-layer stack of LOR 30B light-insensitive resist and SPR700 positive resist is spin-coated. Then, the only non-critical mask alignment of our method is performed on a MJB3 mask aligner (c). A circular mesa wider than the already etched patterns is then etched under the previous ICP-RIE conditions to obtain steeply inclined sidewalls, which ensure the continuity of the following passivating and metallic depositions. After etching, a 300 nm SiO $_{\rm x}$  passivation layer is coated by Inductively-Coupled Plasma-Enhanced Deposition at  $100^{\circ}{\rm C}$  (d). In order to promote the subsequent lift-off of the metal layer on top of the mesa, the LOR recess is slightly widened thanks to a short dip of 10 seconds in the resist developer that leads to a 2.5  $\mu$ m recess. This recess can be proportionally extended with longer development time.

Then, the SPR700 cap resist and the above-mentioned  $SiO_x$  layers are selectively lifted off in acetone. Afterwards, a 50 nm Ti/ 200 nm Au contact is deposited by e-beam evaporation above the remaining LOR layer (still with inverted edge profiles) and the unprotected GaAs surfaces (e). The LOR resist is finally removed in a dimethylsulfoxyde (DMSO) solution heated at 80°C, resulting in the final metal lift-off (f). Figure 2 a) shows a scanning electron microscopy cross-section view of the final device.

The contact pad width is currently 2.5  $\mu$ m, which might be sufficient for low resistance access considering the high doping level of the GaAs cap layer.

Thanks to this method we have fabricated oxide-confined VCSELs by combining the required lateral oxide confinement, mesa etch, sidewall passivation and top contact metallization steps using only two photolithography steps, and this without any critical alignment. Indeed, the mask alignment illustrated in the third scheme presented in Figure 1 does not require an accurate lateral positioning, since the external lateral oxidation extent, of several tens of micrometres, enables to place the outer mesa edge anywhere on this oxide layer.

**Figure 1:** Process flow of the self-aligned VCSEL process including the following steps: via-trench etch (b), lateral selective oxidation (c), isolation mesa etch and SiO<sub>x</sub> passivation (d) and top-contact metallization (e).

**Figure 2**: Self-aligned oxide-confined VCSEL at different processing stages a) Focus Ion Beam cross-view of the VCSEL after the  $SiO_x$  passivation b) Top view of the final device with the oxide aperture visible.

#### **Results and discussion:**

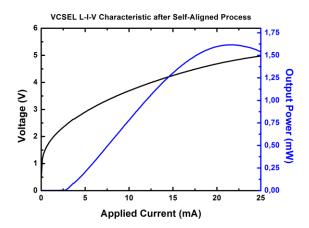

The fabricated oxide-confined VCSELs were electrically characterized in continuous wave at room temperature on a Karl Suss PA200 probe station under forward bias. The emitted power was measured with a large area PIN-25DP Si photodiode. Figure 3 shows the Light-Current-Voltage characteristics of the VCSEL device illustrated in Figure 2 b). A threshold current of 3 mA is obtained and a maximum optical power at rollover is 1.6 mW. These performances are equivalent to the standardly processed oxide-aperture VCSELs. With this same vertical structure, laser performances are very similar whether a standard VCSEL process or our self-aligned process is applied.

Figure 3: L-I-V curve of our self-aligned device.

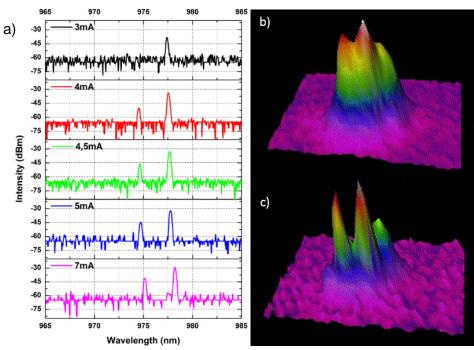

The VCSEL devices were also optically characterized to extract the spectral properties of the output beam, in particular to check their modal content. An optical spectrum analyzer was used (ANDO AQ-6315-A) with a wavelength resolution of 0.1 nm. The laser spontaneous emission was also imaged below the laser threshold which enables to confirm the previously-measured (see Figure 2 b) ) oxide aperture size and shape.

**Figure 4 :** a) spectral characteristics of the fabricated VCSEL for various injection currents (3, 4, 4.5, 5 and 7mA). On the right, modes images b) at 3 mA (nearly single mode) with an OD1 filter (transmission=10%) and c) above the threshold at 7 mA (multi mode) with an OD3 filter (transmission=0.1%).

In Figure 4, the spectrum of the output signal of the same VCSEL is presented at different levels of injection current. The laser appears to be single-mode only just above threshold, since a second lateral mode appears at 4 mA. This second mode is certainly due to the largely asymmetric oxide shape mentioned above. As it can be seen on the modes images the second mode appears along the long axis of the oxide aperture. The mode profile image above threshold (Fig. 4-c), taken with a pump current of 7 mA with an OD3 attenuation filter, has actually an absolute amplitude enhanced by a factor 100 compared to the one taken under 3 mA (Fig. 4-b).

Therefore, this multimode behaviour is not an inherent property of the auto-aligned process, but originates from a slightly-not-uniform etch of the oxidation access trenches which, in turn, has led to an asymmetric oxidation from the four etched trenches.

This process has been done on a very standard and basic vertical VCSEL structure. In particular, the electrical and the optical characteristics of this epitaxial VCSEL structure have not been optimized. Improvements of the electrical and optical performances can be demonstrated with more elaborated vertical VCSEL structures, by using for example multiple oxide layers and optimized doping profiles in the top mirror to improve current injection and optical lateral confinement.

#### **Conclusion:**

We have proposed and demonstrated an innovative technological process to fabricate oxide-confined VCSELs, based on carefully sequenced set of self-aligned technological steps including a mesa etching, a surface passivation, and a top annular contact metallization. We have successfully applied this process flow to oxide-confined VCSELs which are very largely deployed in many different applications. We have shown that our self-aligned process presents a much easier fabrication flow, and hence largely simplify the device manufacturing, without any penalty on the final performances of the laser. Finally, this self-aligned process can also be adapted to other optoelectronic components as modulators, detectors, or solar cells, to mention a few.

#### **Acknowledgements:**

The authors gratefully acknowledge the technological support of RENATECH (French Network of Technology Platforms) within the LAAS-CNRS technological center, and the financial support by the Methusalem foundation, Belgium.

#### References

- 1. Giovane, L. M., Wang, J., Murty, M. R., Harren, A. L., Chang, H. H., Wang, C., ... & Taslim, S. J. "Volume manufacturable high speed 850nm VCSEL for 100G ethernet and beyond". In Optical Fiber Communications Conference and Exhibition (OFC), March 2016 (pp. 1-3). IEEE.

- 2. Grabherr, M. "New applications boost VCSEL quantities: recent developments at Philips". In SPIE OPTO March 2015 (pp. 938102-938102). International Society for Optics and Photonics.

- 3. Krauss, T. F., Delarue, R. M., Laybourn, P. J., Vogele, B., & Stanley, C. R. "Efficient semiconductor ring lasers made by a simple self-aligned fabrication process" IEEE Journal of Selected Topics in Quantum Electronics, 1995, 1(2), pp. 757-761, doi 10.1109/2944.401268

- 4. Chang, M. C., Asbeck, P. M., Wang, K. C., Sullivan, G. J., Sheng, N. H., Higgins, J. A., & Miller, D. L. "AlGaAs/GaAs heterojunction bipolar transistors fabricated using a self-aligned dual-lift-off process" IEEE electron device letters, 1987, 8(7), pp. 303-305, doi 10.1109/EDL.1987.26639

- 5. Al-Omari, A., and Lear, K. L., "VCSELs With a Self-Aligned Contact and Copper-Plated Heatsink", IEEE Photonics Technology Letters, 2005, 17, (9), pp. 1767-1769, doi 10.1109/LPT.2005.851938

- 6. Chua, C. L., Thornton, R. L., and Treat D. W., "Planar Laterally Oxided Vertical-Cavity Lasers for Low-Threshold High-Density Top-Surface-Emitting Arrays", Photonics Technology Letters, 1997, 9 (8), pp. 1060-1062

- 7. Strzelecka, E. M., Morgan, R.A., Liu, Y., Walterson, B., Skogen, J., Kalweit, E., Bounak, S., Changhvongsak, H., Marta, T., Skogman, D., Nohava, J., Gieske, J., Lehman, J., and Hibss-Brenner, M. K. "VCSEL based modules for optical interconnects", Proc. SPIE Vol. 3627, 1999

- 8. Marigo-Lombart, L., Arnoult, A., Mazenq, L., Dubreuil, P., Reig, B., Mauran, N., Thienpont, H., Panajotov, K., and Almuneau, G. "Single lithography-step self-aligned fabrication process for Vertical-Cavity Surface-Emitting Lasers" Materials Science in Semiconductor Processing, 2017, 61, pp. 35-38. http://doi.org/10.1016/j.mssp.2016.12.026