# RÉALISATION DE MURS P + TRAVERSANTS POUR DES FONCTIONS DE PUISSANCE INTÉGRÉES

Éric Imbernon, Emmanuel Scheid, Françoise Rossel, Marie Breil, H Carrière, Pascal Dubreuil, Bernard Rousset, Patrick Austin, Jean Louis Sanchez

# ▶ To cite this version:

Éric Imbernon, Emmanuel Scheid, Françoise Rossel, Marie Breil, H Carrière, et al.. RÉALISATION DE MURS P + TRAVERSANTS POUR DES FONCTIONS DE PUISSANCE INTÉGRÉES. Seminario Annual de Automatica, Electronica Industrial e Instrumentacion. Electronique de Puissance du Futur (SAAEI-EPF'04), Sep 2004, Toulouse, France. 4p. hal-01867595

# HAL Id: hal-01867595 https://laas.hal.science/hal-01867595

Submitted on 4 Sep 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# RÉALISATION DE MURS P<sup>+</sup> TRAVERSANTS POUR DES FONCTIONS DE PUISSANCE INTÉGRÉES E. Imbernon, E. Scheid, F. Rossel, M. Breil, H. Carrière, P. Dubreuil, B. Rousset, P. Austin, J-L. Sanchez

LAAS-CNRS, 7, Avenue du Colonel Roche, 31077 Toulouse cedex 4, France

E-mail: imbernon@laas.fr

### **RÉSUMÉ**

Les murs traversants P<sup>+</sup> peuvent être considérés comme des régions clés dans les architectures 3D pour de nouvelles fonctions de puissances intégrées bidirectionnelles en tension et en courant. Dans la première partie, nous démontrons la faisabilité de la fabrication de ces murs P<sup>+</sup> qui combinent la réalisation de tranchées profondes dans le silicium par gravure ionique réactive et le remplissage de celles-ci par du polysilicium fortement dopé bore.

#### 1. INTRODUCTION

Les composants semi-conducteurs de puissance occupent une place de plus en plus importante dans les équipements domestiques pour la commande ou la conversion de l'énergie électrique. Une application souvent rencontrée pour ces composants est le contrôle de l'énergie transférée à une charge à partir d'une source AC. Pour ce type d'applications, la fonction interrupteur doit avoir une caractéristique bidirectionnelle en courant et en tension :

- les gammes de tension et de courant (600 V, 10 A) nécessitent une architecture verticale,

- la tenue en tension symétrique nécessite des terminaisons de jonctions spécifiques,

- la bidirectionalité en courant nécessite des architectures d'interrupteurs permettant leur commande pour des tensions anodes-cathodes positives ou négatives.

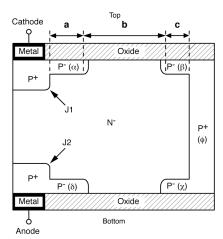

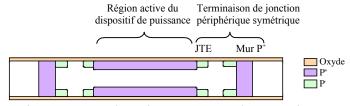

Fig. 1 : Coupe schématique d'une structure symétrique en tension.

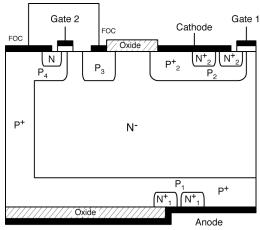

Dans ce contexte, plusieurs architectures basées sur des murs P<sup>+</sup> traversants la plaque de silicium ont été proposées. Nous présentons dans ce papier deux exemples (Figs 1 et 2) qui illustrent l'intérêt des murs traversants P<sup>+</sup>. Le premier exemple concerne une structure périphérique permettant d'obtenir une tenue en tension symétrique (Fig. 1) [1]. Le second correspond à un dispositif MOS-thyristor bidirectionnel (Fig. 2). Dans cette structure, le mur P<sup>+</sup> permet, d'une part, d'obtenir une tenue en tension et une conduction du courant symétrique et, d'autre part, d'obtenir une commande de grille du dispositif pour des tensions anode-cathode positives ou négatives en utilisant une grille située sur la face avant.

Fig. 2 : Coupe schématique d'un dispositif MOS-thyristor bidirectionnel en tension et en courant.

Traditionnellement, ces murs sont réalisés par double diffusion d'atomes dopants de type P sur les faces avant et arrière de la plaquette. Cette technique conduit à occuper une grande surface de silicium et provoque des défauts et des contraintes sur la plaquette. La thermomigration d'aluminium est également une solution alternative réalisée en fin de procédé technologique à une température de 1350 °C [3], mais qui n'est aujourd'hui pas encore compatible avec les filières technologiques MOS/bipolaire. Pour essayer de palier à ces inconvénients, nous avons développé une solution technologique combinant la gravure ionique réactive du silicium et le dépôt de silicium polycristallin dopé bore compatible avec une filière technologique MOS/bipolaire permettant de fabriquer de nouvelles fonctions de

puissance intégrées basées sur les interactions électriques 3D dans le volume du silicium.

#### 2. RÉALISATION DES MURS P<sup>+</sup>

#### 2.1 Réalisation des tranchées profondes

L'objectif principal de ce travail concerne la réalisation de murs continus P<sup>+</sup> localisés à la périphérie de la zone active du composant de puissance. La solution technologique adoptée pour matérialiser les murs P<sup>+</sup> combine la gravure ionique réactive du silicium et le dépôt de polysilicium dopé bore. La première étape de ce processus de fabrication consiste à réaliser des tranchées traversantes suivant un motif discontinu afin de maintenir une bonne résistance mécanique.

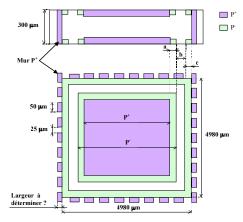

La largeur de ces motifs sur le masque est de 4  $\mu$ m afin d'obtenir en final une largeur compatible avec l'épaisseur des dépôts de polysilicium. La longueur des tranchées est de 50  $\mu$ m et la distance entre tranchées est de 25  $\mu$ m (Fig. 3).

Avant de réaliser la gravure de 300  $\mu m$  de silicium par RIE (Reactive Ion Etching), l'oxyde de masquage doit être protégé par une résine spécifique (PLP 100) de 16  $\mu m$  d'épaisseur. Après la photolithographie de la résine, une gravure par RIE de l'oxyde est réalisé en utilisant trois gaz  $CF_4 + SF_6 + O_2$  pendant une heure.

Fig. 3 : Coupe schématique et topologie de la structure de test

Ensuite la gravure du silicium est réalisé dans un réacteur de gravure par plasma Multiplex ICP (Inductively Coupled Plasma) de la société STS. Le procédé de gravure profonde à flancs droits utilisé est un processus Bosch basé sur une technologie de gravure ionique réactive profonde (DRIE) du silicium. Cette technique est issue d'un brevet dans lequel la chimie de gravure est composé de deux plasmas différents et séquentiels de quelques secondes chacun. Le premier plasma est un plasma de passivation utilisant du C<sub>4</sub>F<sub>8</sub> et le second un plasma de gravure isotrope utilisant du SF<sub>6</sub>. L'association de ces

deux plasmas permet de créer un dépôt permanent sur les flancs des tranchées puis de graver le silicium afin d'obtenir au final une tranchée à flancs droits [4].

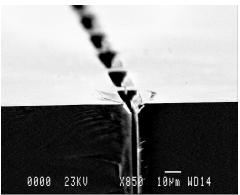

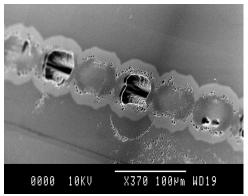

Des tranchées traversantes de 300 µm ont été réalisées à travers la plaquette de silicium suivant un motif en pointillé (Fig. 4). Ce procédé permet d'obtenir un haut degré d'anisotropie et des vitesses de gravure comprises entre 3 et 5 µm.mm<sup>-1</sup> sont atteints.

Fig. 4 : Photo MEB des pointillés formés par les tranchées de 50 μm de long espacées de 25 μm.

Fig. 5 : Face avant de la plaquette après gravure.

Fig. 6 : Face arrière de la plaquette après gravure.

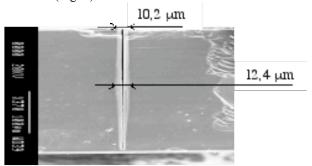

Les figures 5 et 6 montrent respectivement la face avant et arrière de la plaquette après la gravure. Il est à noter que pour une tranchée de largeur 4 µm sur masque, la largeur

finale de la tranchée est comprise entre 10 et  $12~\mu m$  à cause des effets de surgravure.

## 2.2 Remplissage des tranchées profondes

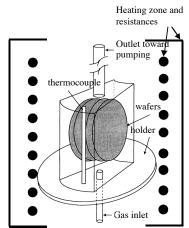

La seconde étape consiste à remplir ces tranchées profondes avec du polysilicium fortement dopé bore. Le dépôt du polysilicium dopé in situ est réalisé dans un four LPCVD (Low Pressure Chemical Vapor Deposition) non conventionnel, appelé réacteur secteur, spécialement destiné à la croissance de couches épaisses [5, 6]. Ce réacteur, dont le principe est schématisé sur la figure 7, utilise une source de silane (SiH<sub>4</sub>) et de bore (BCl<sub>3</sub>) dilué dans de l'azote (N<sub>2</sub>). Il apparaît que la réduction de la température de travail associée à une augmentation de la vitesse de dépôt conduit à une forte réduction du niveau de la contrainte, qui est une problématique connu des dépôts de polysilicium dopé bore dans des fours LPCVD conventionnels. Ainsi, avec une température de dépôt de 490 °C dans le réacteur secteur, et une pression de dépôt résultante totale de 532 Pa, avec une cinétique de dépôt supérieure à 33 nm/min, nous avons obtenus des films épais avec une contrainte inférieure à 50 MPa et une résistivité de 1.5 mΩ.cm. (Dans ces conditions, la contrainte est trop faible pour être facilement mesurable, et seule une valeur minimale de 50 MPa peut être déterminée).

Fig. 7: Schéma du réacteur secteur.

La photo prise au MEB (Fig. 8) montre clairement que la tranchée est complètement remplie de polysilicium, après le dépôt d'une couche épaisse de polysilicium (6 μm).

La concentration d'atomes de bore du polysilicium déposé est suffisamment élevé pour jouer le rôle de source dopante [7]. Après avoir éliminé le silicium polycristallin par gravure sur les deux faces, une étape de redistribution permet aux atomes dopants de bore contenues dans le polysilicium de diffuser dans le volume de silicium. Cette étape de redistribution (20 heures à 1150 °C) permet d'obtenir une diffusion latérale de 12 µm et de matérialiser ainsi une région de type P continue, comme on peut le

vérifier sur la photographie obtenue avec le MEB après révélation (Fig. 9).

Fig. 8 : Photographie MEB de la coupe d'une tranchée de 300 µm de profondeur remplie de polysilicium.

Fig. 9 : Photographie MEB des tranchées vues de dessus après remplissage et diffusion de bore.

## 3. APPLICATION À LA RÉALISATION D'UNE TERMINAISON DE JONCTION PÉRIPHÉRIQUE SYMÉTRIQUE

#### 3.1 Structure

Pour valider cette réalisation technologique, nous avons réalisé une terminaison de jonction périphérique, permettant d'obtenir une tenue en tension symétrique, basée sur l'utilisation des murs P<sup>+</sup> (Fig. 1).

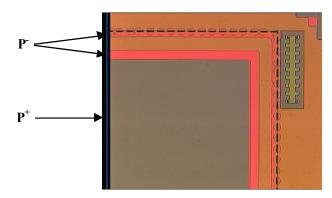

Le principe de cette terminaison de jonction est basé sur l'étalement des lignes équipotentielles dans le substrat à travers un mur traversant P<sup>+</sup> [1]. Après la réalisation du mur P<sup>+</sup> décrit précedemment, des régions P<sup>-</sup> et P sont crées (Figs 10 et 11).

Fig. 10 : Coupe schématique représentant la zone active au milieu de la puce et la terminaison de jonction périphérique.

Fig. 11: Vue de dessus des régions P et P.

Les régions P sont utilisées comme terminaisons de jonctions (comme pour les terminaisons de type JTE classiques), tandis que les régions P correspondent au caisson P du composant de puissance.

#### 3.3 Résultats électriques expérimentaux

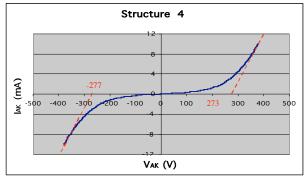

Une tension positive (0 à 500 V), puis une tension négative (0 à -500 V) sont appliqués successivement sur la cathode, l'anode étant à la masse.

Fig. 12 : Caractéristique expérimentale  $I_A(V_{AK})$  illustrant la tenue en tension symétrique.

La figure 12 montre la tenue en tension symétrique du composant test réalisé avec la terminaison de jonction spécifique. La structure possède une tension de claquage positive de 273 volts, et la tension de claquage négative est de -277 volts. Ce résultat confirme que le mur P<sup>+</sup> entourant le composant de puissance est entièrement continu.

#### **CONCLUSION**

Une solution technologique innovante pour réaliser des murs traversants P<sup>+</sup> est présentée dans ce papier. Ces murs P<sup>+</sup> représentent une région clé dans les architectures 3D des nouveaux dispositifs de puissances intégrés bidirectionnels en courant et en tension, permettant le développement de nouvelles fonctionnalités. Ces murs P<sup>+</sup>

peuvent être utilisés comme terminaisons de jonctions périphériques, mais aussi pour la commande de grille d'interrupteurs pour des tensions anodes-cathodes positives ou négatives, en utilisant simplement une grille sur la face avant de la plaquette afin de supprimer les contraintes de mise en boîtier due à la présence de grilles MOS sur la face arrière.

La solution technologique est basée sur la gravure de tranchées à travers la plaque de silicium, puis sur le remplissage de ces tranchées avec du polysilicium fortement dopé bore, jouant le rôle de source dopante de type P. Après une étape de diffusion, les atomes dopants de bore diffusent dans le volume du silicium et permettent de créer un mur P<sup>+</sup> vertical continu le long des pointillés définis sur le masque.

Cette solution technologique, totalement compatible avec des technologies MOS/bipolaires, permet ainsi la fabrication de nouvelles fonctions de puissance intégrées, et peut offrir un bon degré de fiabilité pour les applications industrielles.

#### REFERENCES

- [1] O. Causse, P.Austin, J-L Sanchez, G. Bonnet, "Achievement of a new planar peripheral structure supporting a symetrical blocking voltage", EPE 2001, September 2001, Gratz

- [2] A. Bourennane, M. Breil, J-L Sanchez, J. Jalade, "New MOS gated triac structures for specific mains applications" *EPE- PEMC*, September 2002 Dubrovnik (Croatia)

- [3] J-M. Dilhac, L. Cornibert, B. Morillon, S. Roux, C. Gannibal, "Industrial relevance of deep junctions produced by rapid thermal processing for power integrated devices", *International Symposium on Power Semiconductor Devices and Ics (ISPSD'99)*, *Toronto*, 1999, pp. 327-240.

- [4] J-B. Bardwaj, H. Ashras, A. Mc Quarrie, "Dry Silicon etching for MEMs", Symposium on Microstructures and Microfabricated at the Annual Meeting of the Electrochemical Society, Montreal, Quebec, Canada, May 4-9, 1997.

- [5] H. Vergnes, E. Scheid, P. Duverneuil, J.P. Couderc: Proceedings of the 10<sup>th</sup> European Conference on CVD, Journal de Physique IV, 5 (1995) p C5-997.

- [6] E. Scheid, L. Furgal, H. Vergnes: Proceedings of the 12<sup>th</sup> European Conference on CVD, Journal de Physique IV, 9 (1999) p.8-885.

- [7] J-L. Sanchez, E. Scheid, P. Austin, M. Breil, H. Carrière, P. Dubreuil, E. Imbernon, F. Rossel, B. Rousset, "Realization of vertical P+ wall through-wafer, SPIE International Symposium on Micromachining and Microfabrication Process Technology IX, San Jose (USA), 27-29 Janvier 2004, Vol.5342, pp.119-127.