## DC Gate Leakage Current Model Accounting for Trapping Effects in AlGaN/GaN HEMTs

Raul Perez Rodriguez, Benito González, Javier Garcia, Gaëtan Toulon, Frédéric Morancho, Antonio Núñez

### ▶ To cite this version:

Raul Perez Rodriguez, Benito González, Javier Garcia, Gaëtan Toulon, Frédéric Morancho, et al.. DC Gate Leakage Current Model Accounting for Trapping Effects in AlGaN/GaN HEMTs. Electronics, 2018, 7 (10), pp.210. 10.3390/electronics7100210 . hal-01955666

## HAL Id: hal-01955666 https://laas.hal.science/hal-01955666

Submitted on 14 Dec 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Article

# DC Gate Leakage Current Model Accounting for Trapping Effects in AlGaN/GaN HEMTs

Raúl Rodríguez <sup>1</sup>, Benito González <sup>1</sup>, Javier García <sup>1</sup>, Gaetan Toulon <sup>2</sup>, Frédéric Morancho <sup>3</sup> and Antonio Núñez <sup>1</sup>

- <sup>1</sup> IUMA, ULPGC, Campus Universitario de Tafira S/N, E-35017 Las Palmas de G.C., Spain; rrodriguez@iuma.ulpgc.es (R.R.); jgarcia@iuma.ulpgc.es (J.G.); nunez@iuma.ulpgc.es (A.N.)

- <sup>2</sup> Exagan, 51 rue de l'Innovation, 31670 Labège, France; gtoulon@laas.fr

- 3 LAAS-CNRS, Université de Toulouse, CNRS, UPS, 31400 Toulouse, France; morancho@laas.fr

- \* Correspondence: benito@iuma.ulpgc.es; Tel.: +34-928-452-875

Received: 13 July 2018; Accepted: 19 September 2018; Published: 21 September 2018

**Abstract:** A DC leakage current model accounting for trapping effects under the gate of AlGaN/GaN HEMTs on silicon has been developed. Based on TCAD numerical simulations (with Sentaurus Device), non-local tunneling under the Schottky gate is necessary to reproduce the measured transfer characteristics in a subthreshold regime. Once the trap concentration and distribution are determined in the device, the resulting gate leakage current is modeled making use of Verilog-A, for typical operation regimes.

**Keywords:** AlGaN/GaN HEMT; gate leakage current; traps; numerical simulation; modeling

#### 1. Introduction

AlGaN/GaN devices grown on silicon substrates are the main candidates for power applications in the next generation of power converters [1–3]. Therefore, an accurate modeling of the AlGaN/GaN HEMT is essential in the design of circuits for both high power and radio frequency applications. On the other hand, simplification is mandatory when dealing with compact modeling for circuit simulation purposes. Thus, this paper is devoted to obtaining a simple analytical expression for the DC current of AlGaN/GaN HEMTs and, at the same time, accurately supporting the underlying physics.

Although GaN HEMTs are promising, the presence of traps during crystal growth and epitaxial processing implies not desired aspects such as leakage current and current collapse, among others [4]. A deeper understanding of trapping effects is essential for the electrical functionality and correct modeling of these devices, in order to achieve accurate circuit designs [5–7]. In fact, the etching process for Schottky gates together with electrical stress during normal device operation may provoke traps in barriers.

It is well known that there are four major mechanisms for gate leakage currents. Fowler-Nordheim (FN) [8] and Thermionic-Emission (TE) [9] are one-step tunneling processes taking place near the Fermi level and at higher energy levels, respectively. These high-energy mechanisms through the entire energy barrier can be accounted for more easily. Poole–Frenkel emission (PF) [10] is an emission transport through a continuum of trap states, which is sensitive to the temperature and the electric field and, therefore, difficult to identify at low bias in the subthreshold region. Finally, in Trap Assisted Tunneling (TAT) emission [11] most of tunneling takes place through a two-step tunneling via a mid-band state-layer of scattered traps within the AlGaN barrier layer [12].

Hopping through high-density surface electronic states in AlGaN is only significant for very short gate to drain distances, when its corresponding current approaches the more significant vertical

Electronics **2018**, 7, 210 2 of 10

tunneling component of the leakage current [13]. This surface component can be easily controlled through proper passivation. Therefore, we focus our work on vertical leakage through traps.

In this work, the HEMT description is presented in Section 2. Section 3 is devoted to an evaluation of trap concentration and distribution, through numerical simulation. The model to account for the resulting gate leakage current is developed in Section 4, whose transfer characteristics are compared with those measured. Finally, conclusions are presented in Section 5.

#### 2. Device Description

The long channel device under study is a normally-on HEMT on silicon (from a normally-off AlGaN/GaN HEMT using fluorine implantation below the channel [14]), based on the AlGaN/GaN system, 1000  $\mu$ m wide, with the technological processing carried out at LAAS.

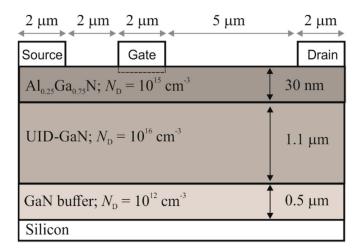

The device geometry and material composition are drawn in Figure 1. Corresponding donor doping concentrations,  $N_{\rm D}$ , are also indicated. Notice that below the AlGaN barrier and GaN channel, 30 nm and 1.1  $\mu$ m deep, respectively, a practically undoped GaN buffer (with similar electrothermal performance) substitutes the transition layers for simulation purposes.

**Figure 1.** Simulated AlGaN/GaN HEMT. Below the gate, the donor trap layer is indicated with dashed lines.

Finally, it is known that the etching process in GaN-based devices during a Schottky gate contact formation, can lead to defective adhesion properties at the metal/semiconductor interface, originating traps under the gate and, therefore, a leakage current increment [15,16]. Thus, making use of deep-level transient spectroscopy (DLTS), N-vacancies (surface donors) were demonstrated to be formed under the gate in [15].

Additional trapping under the gate can be caused by electrical stress [17,18], which is present in the (across the barrier) gate edge region of the HEMT under study. Under electrical stress, the elastic energy in the high-field region increases on top of this. If the elastic energy exceeds a critical value, crystallographic defects are formed [19].

Thus, a trap concentration under the gate of the transistor investigated is considered, as indicated in Figure 1 with dashed lines.

#### 3. Numerical Simulation

Numerical simulations have been performed with a Sentaurus Device (from Synopsys) [20]. The transistor DC response, at room temperature, is analyzed solving the Poisson and drift-diffusion equations, together with the heat equation as in [21], polarization charges [22], and the rest of physical parameters from [14]. A gate Schottky diode (i.e., thermionic emission, TE) with Poole–Frenkel (PF) is considered for all operating regimes [23].

Electronics 2018, 7, 210 3 of 10

Traps on the top of the AlGaN barrier, with a donor sheet density of  $2.3 \times 10^{13}$  cm<sup>-2</sup> and an activation energy from the center of the band gap of 0.4 eV have been incorporated, as well as acceptor traps in the GaN buffer, with a concentration of  $10^{17}$  cm<sup>-3</sup> and an activation energy from the valence band maximum of 0.368 eV [5].

In order to set the threshold voltage, no fitting for the polarization charge is needed (opposite to [14]) when traps under the gate are determined [19], as they (in volume) can modify the Fermi level position in the energy band diagram, or (when superficial) produce a straight-on threshold voltage displacement [24].

Regarding the device description, a layer of donor traps, 2 nm deep, just below the gate terminal, with an activation energy from the conduction band minimum of 0.2 eV, and capture cross-section of  $10^{-15}$  cm<sup>-2</sup>, is firstly assumed (according to [19]).

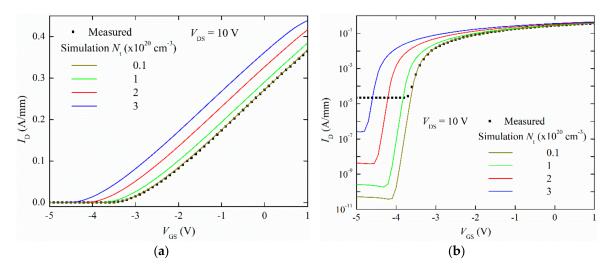

Then, for any trap concentration,  $N_{\rm t}$ , ranging from  $10^{19}~{\rm cm}^{-3}$  to  $3\times 10^{20}~{\rm cm}^{-3}$ , transconductance  $(\partial I_{\rm D}/\partial V_{\rm GS})$  in strong inversion regime is numerically reproduced, as Figure 2a shows, where measured (with symbols) and simulated (with lines) transfer characteristics are represented in linear scale. Notice that, for a trap concentration of  $10^{19}~{\rm cm}^{-3}$ , the measured transfer characteristics above threshold voltage are well predicted, additionally.

**Figure 2.** Measured (symbols) and simulated (lines) transfer characteristics for the AlGaN/GaN HEMT, for different traps concentration, with drain current in (a) linear scale and (b) logarithmic scale;  $V_{\rm DS} = 10 \text{ V}$ .

However, when drain current of transfer characteristics is represented in logarithmic scale, Figure 2b, the existence in subthreshold regime of a constant leakage current,  $I_{\rm off}$ , of 22.5  $\mu$ A does show up, which is not being numerically reproduced.

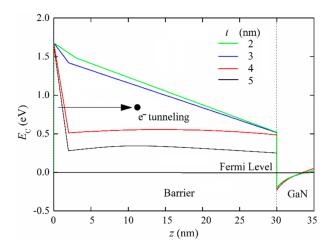

To solve the problem of the adjustment of this gate leakage current behavior, without deteriorating the transfer characteristics in conduction regime (with gate-to-source voltage,  $V_{\rm GS}$ , above threshold voltage), non-local tunneling incorporating FN emission through the gate is activated in simulations [19,23], with the donor layer thickness for traps, t, being varied from 2 nm to 5 nm. Figure 3 shows the resulting conduction band energy minimum profile below the gate ( $E_{\rm C}$ , with colored lines), in depth (z). Notice how the transversal electric field ( $|\partial E_{\rm C}/\partial z|$ ) under the gate drastically increases with the thickness of the trap layer, deriving a higher leakage current by tunneling.

Electronics 2018, 7, 210 4 of 10

**Figure 3.** Conduction band energy minimum vs. depth under the gate, when varying the thickness of the donor traps layer beneath the gate: t = 2, 3, 4, and 5 nm.

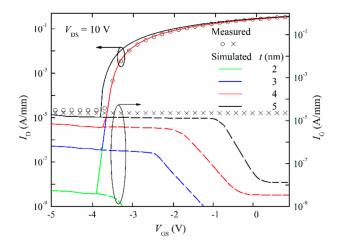

This effect is observed in Figure 4, where transfer characteristics (left axis) and corresponding gate current (right axis) are represented. Note that, in an off-state regime, gate and drain measured currents (with symbols) coincide, demonstrating that all leakage current through the gate is collected by the drain terminal. Numerical simulation data (with lines) show that the subthreshold current increases with the trap layer thickness, and, for a value of 4 nm, the difference between measured and simulated subthreshold current is reduced in more than five orders of magnitude, with a correct prediction in strong inversion regime being maintained. Higher values (e.g., t = 5 nm) are not suitable because transfer characteristics deteriorate, since the threshold voltage suffers a considerable reduction not observed in measurements.

**Figure 4.** Measured (circles) and simulated (solid lines) transfer characteristics in logarithmic scale (left axis), and corresponding measured (crosses) and simulated (dashed lines) gate current (right axis).

It can be noticed that had TAT emission been considered, instead of FN emission, similar results would be obtained. However, with FN emission, there is no necessity of introducing TAT at room temperature, opposite to [25], in order to model drain current continuity.

#### 4. Modeling

Most existing compact models for HEMT are based on a two-dimensional electron gas (2-DEG) precise description at the AlGaN-GaN heterojunction. Charge and current models tend to end up being complex and unattractive for circuit design, due to the evaluation of the Fermi level (i.e., the

Electronics 2018, 7, 210 5 of 10

charge in the channel) when considering the existence of several energy levels in the corresponding 2-DEG quantum well.

However, assuming a triangular quantum well potential with the contribution of the first energy level being the one taken into account, with most of the 2-DEG concentration, a simple relationship between the applied voltage and the 2-DEG concentration, n, can be established [26]:

$$n = DV_{\rm TH} \ln \left[ \exp \left( \frac{E_F - E_0}{V_{\rm TH}} \right) + 1 \right] \approx \frac{\varepsilon}{qd} (V_{\rm G} - V_{\rm T} - E_{\rm F})$$

(1)

where D represents the density of states,  $V_{TH}$  is the thermal voltage,  $E_F$  is the Fermi level,  $E_0$  the position of the first energy level in the quantum well,  $\varepsilon$  is the AlGaN barrier dielectric permittivity, d the barrier thickness, q the absolute charge of an electron and  $V_T$  is the transistor threshold voltage.

In addition, this gives, as a result, an analytical and simple model for the drain-to-source current,  $I_{\rm D}$ , through the GaN channel, maintaining the accuracy and covering all operating regimes for long channel devices, which is given by [26]:

$$I_{\rm D} = -\frac{q\mu W}{L} \left[ \frac{qd}{2\varepsilon} \left( n_{\rm D}^2 - n_{\rm S}^2 \right) + \frac{2}{5} \gamma_0 \left( n_{\rm D}^{\frac{5}{3}} - n_{\rm S}^{\frac{5}{3}} \right) + V_{\rm TH}(n_{\rm D} - n_{\rm S}) \right]$$

(2)

where  $n_{\rm S}$  and  $n_{\rm D}$  are the 2-DEG concentration at the source and drain terminals, respectively,  $\mu$  is the electron mobility in the channel (evaluated as in [26]), W is the gate width (1000 μm), L the channel length (2  $\mu$ m), and  $\gamma_0$  is a fitting parameter. This model is suitable for different geometries and substrate materials, with the self-heating effects being incorporated through a device thermal resistance,  $R_{\text{TH}}$ , as in [27], where the device temperature increment,  $\Delta T$ , respecting room temperature, is evaluated as the product  $R_{\mathrm{TH}}I_{\mathrm{D}}V_{\mathrm{DS}}$ . Compact model parameters used in this work are summarized in Table 1. For the thermal resistance, a realistic value of 52 K/W is assumed (30 K/W in [28], as the sum of the silicon substrate resistance, 17.4 K/W [23], and that for the semi-insulating transition layers of the GaN buffer-AlN, pGaN, etc., 0.5 μm thick in [29]).

Unit **Parameter** Value d nm  $V_{\mathrm{T}}$ -3.8Vcm<sup>4/3</sup>  $2.12 \times 10^{-12}$  $\gamma_0$ K/W

52

$R_{TH}$

Table 1. Compact model parameters.

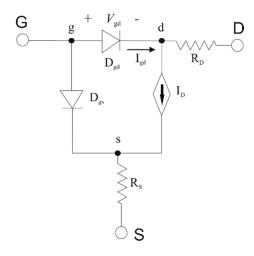

The large signal scheme of the compact model, which is implemented in the electrical simulator ADS (from Keysight) employing the industry modeling language for analog circuits and devices Verilog-A, is presented in Figure 5, where the Schottky gate is modeled through diodes  $D_{gd}$  and  $D_{gs}$ , from gate-to-drain and gate-to-source intrinsic nodes, respectively.

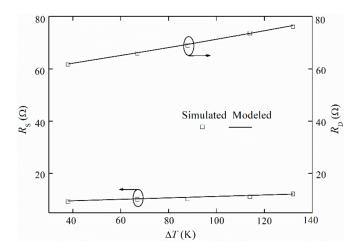

Parasitic resistances in source and drain terminals,  $R_{\rm S}$  and  $R_{\rm D}$  (temperature-dependent), which are decisive for the DC performance evaluation of HEMTs, are incorporated with data extracted from simulations. Both of them, particularly  $R_D$ , are higher as the device temperature increment rises, as Figure 6 shows (squares). A second-order polynomial is enough to fit this dependence (solid lines), that is  $R_{S/D} \approx a + b\Delta T + c\Delta T^2$ ; fitting parameters, a, b and c, are indicated in Table 2.

Electronics **2018**, 7, 210 6 of 10

Figure 5. HEMT large signal equivalent circuit.

**Figure 6.** Numerical (symbols) and modeled (lines)  $R_S$  (left axis) and  $R_D$  (right axis) against device temperature increment.

**Table 2.** Fitting parameters for  $R_S$  and  $R_D$ .

|                                   | R <sub>S</sub> | $R_{\mathrm{D}}$    |

|-----------------------------------|----------------|---------------------|

| a (Ω)                             | 8.1            | 56.4                |

| $b\left(\Omega/\mathrm{K}\right)$ | 0.03           | 0.13                |

| $c(\Omega/K^2)$                   | -              | $1.4 	imes 10^{-4}$ |

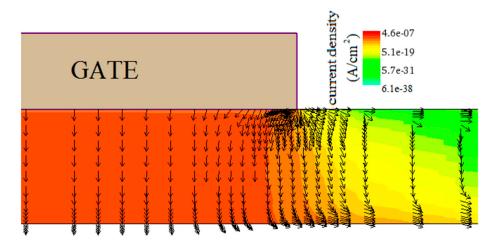

The gate leakage current could flow from gate to drain terminals through the top surface of the AlGaN barrier or, vertically, crossing the barrier through the GaN channel [19]. Numerical simulations with TE, PF and FN emissions show that the second case is taking place in the HEMT under study, as Figure 7 indicates for reverse-biased gate ( $V_{\rm GS} = -5~{\rm V}$  and  $V_{\rm DS} = 10~{\rm V}$ ), with the current density flowing through the barrier, under the gate, by the drain side.

Electronics **2018**, 7, 210 7 of 10

**Figure 7.** Current density flow through the barrier;  $V_{GS} = -5 \text{ V}$  and  $V_{DS} = 10 \text{ V}$ .

Gate leakage current has been already modeled analytically in a surface potential-based compact model [30], with TAT emission having been introduced in order to keep current continuity. However, for simplicity, it is proposed to introduce the gate leakage current into the compact model by a single and non-ideal continuous expression for the current of the gate-to-drain diode, which is given by:

$$I_{gd} = W \times L \left[ j_{s} \times \left( exp \left( \frac{V_{gd}}{m \times V_{TH}} \right) - 1 \right) - j_{off} \right]$$

(3)

where  $j_{\text{off}}$  corresponds to the gate leakage current density in subthreshold regime by PF and FN emissions,  $j_s$  is the reverse saturation TE current density, and m is the non-ideality parameter for Schottky gates in AlGaN/GaN based HEMTs [30], which could be properly set when forward gate-to-drain current is available (which is not the case for typical operation regimes).

For typical operation regimes of the HEMT (off, linear and saturation regimes), when the Schottky gate is reverse-biased, the absolute value of the current density of the drain-to-gate diode,  $j_{\rm gd}$ , can be approximated by

$$j_{\rm gd} = j_{\rm s} + j_{\rm off} \tag{4}$$

condition for which measurements were collected. Then, equaling  $j_{\rm gd}$  (4) to the total measured reverse density current of the Schottky gate and attending that, from numerical simulations, the TE term represents 0.026% of the total reverse density current, 112  $\mu$ A·cm<sup>-2</sup> and 29 nA·cm<sup>-2</sup> are obtained, respectively, for  $j_{\rm off}$  and  $j_{\rm s}$ .

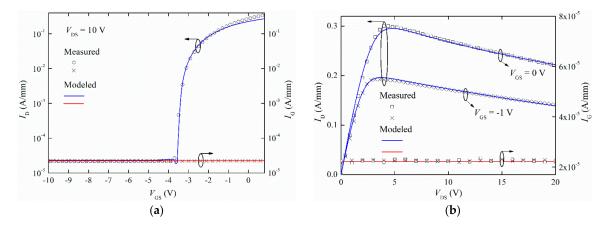

Thus, the resulting modeled (dashed line) and measured (symbols) transfer characteristics in saturation regime (left axis, with  $V_{\rm DS}$  = 10 V), in logarithmic scale, are represented in Figure 8a, together with the corresponding gate current (right axis) in a similar way. A good correspondence between modeled and measured data has been achieved, with an average relative error of 8.3% (around  $V_{\rm GS}$  = 0 V) and 0.6%, respectively, for the drain and gate current. And, again, drain and gate currents in subthreshold regime do match. Similarly, measured and modeled output characteristics (left axis), with the corresponding gate current (right axis), are represented in Figure 8b for different gate voltages. A good agreement is, again, observed, with an average relative error of 1.8% and 1% for the drain and gate current, respectively. Therefore, our model (4) can be considered appropriate for the leakage current of GaN-based HEMTs, through the Schottky gate, within typical operation regimes.

Other physics-based models accounting for reverse gate leakage current have been developed. In [31] the model is based on the characteristic energy related to the tunneling probability in the Wentzel–Kramers–Brillouin approximation, considers mainly TE based mechanisms, and the study is applied to leakage behavior in aged devices. In [32] the model is based on surface donor traps under the gate plus the volume density of bulk traps present in the AlGaN layer and the trap energy

Electronics 2018, 7, 210 8 of 10

dependent rate constant. Notice that the "two-step" gate metal surface traps (filled interface trap states) plus bulk traps tunneling (GaN on SiC process) of [32], is quantified in our work and also located in depth and thickness since a donor trap layer at defined depth emerge in simulations matching suggestions from device manufacturing (in a GaN on Silicon process). However, as simplification is mandatory in compact modeling for circuit designers, our model offers a simpler and differentiable analytical expression for the Schottky gate leakage current of GaN-based HEMTs, which is valid for circuit simulation purposes, while supporting accurately the underlying physics, including the relative weight of PF, FN and TE mechanisms.

**Figure 8.** Measured (symbols) and modeled (lines) (a) transfer characteristic in saturation regime (left axis, with  $V_{\rm DS}=10~{\rm V}$ ) and corresponding gate current (right axis), in logarithmic scale, and (b) output characteristics (left axis) and corresponding gate current (right axis), at different gate voltages:  $V_{\rm GS}=-1~{\rm and}~0~{\rm V}$ .

#### 5. Conclusions

In this work, a gate leakage current in subthreshold regime for an AlGaN/GaN-based HEMT, grown on silicon, has been detected and quantified through measurements and numerical simulations. The gate leakage current is attributed to non-local FN tunneling and Poole–Frenkel emission, with donor trap concentration, activation energy, cross-section, and depth being set beneath the gate. Numerical simulations demonstrate that the gate leakage current flows across the barrier, towards the GaN channel, which has been successfully modeled making use of Verilog-A through a simple analytical expression, which is valid for circuit simulation purposes and typical operation regimes of the transistor, while accurately supporting the underlying physics. Relative errors between measured and modeled data for the gate leakage current demonstrate the validity of our model, which has been successfully incorporated into a DC compact model.

**Author Contributions:** R.R. developed the study, which was directed by B.G., J.G. aided to develop the model for the gate leakage current. F.M. provided the measurements, and G.T. and A.N. assisted on numerical simulations and trapping effects, respectively.

Funding: This research received no external funding.

Conflicts of Interest: The authors declare no conflict of interest.

#### References

Chander, S.; Ajay; Nirmal, D.; Gupta, M. 30 nm Normally off enhancement mode AlGaN/GaN HEMT on SiC substrate for future high speed nanoscale power applications. In Proceedings of the 2017 International Conference on Innovations in Electrical, Electronics, Instrumentation and Media Technology (ICEEIMT), Coimbatore, India, 3–4 February 2017; pp. 293–296. Electronics 2018, 7, 210 9 of 10

Chung, J.W.; Kim, T.-W.; Palacios, T. Advanced gate technologies for state-of-the-art fT in AlGaN/GaN HEMTs. In Proceedings of the 2010 International Electron Devices Meeting, San Francisco, CA, USA, 6–8 December 2010; pp. 30.2.1–30.2.4.

- 3. Meneghesso, G.; Verzellesi, G.; Danesin, F.; Rampazzo, F.; Zanon, F.; Tazzoli, A.; Meneghini, M.; Zanoni, E. Reliability of GaN high-electron-mobility transistors: State of the art and perspectives. *IEEE Trans. Device Mater. Reliab.* 2008, *8*, 332–343. [CrossRef]

- 4. Mukherjee, K.; Darracq, F.; Curutchet, A.; Malbert, N.; Labat, N. TCAD simulation capabilities towards gate leakage current analysis of advanced AlGaN/GaN HEMT devices. *Microelectron. Reliab.* **2017**, 76–77, 350–356. [CrossRef]

- 5. Bisi, D.; Meneghini, M.; de Santi, C.; Chini, A.; Damman, M.; Brückner, P.; Mikulla, M.; Meneghesso, G.; Zanoni, E. Deep-Level Characterization in GaN HEMTs—Part I: Advantages and Limitations of Drain Current Transient Measurements. *IEEE Trans. Electron Devices* **2013**, *60*, 3166–3175. [CrossRef]

- 6. Chini, A.; Soci, F.; Meneghini, M.; Meneghesso, G.; Zanoni, E. Deep Levels Characterization in GaN HEMTs—Part II: Experimental and Numerical Evaluation of Self-Heating Effects on the Extraction of Traps Activation Energy. *IEEE Trans. Electron Devices* **2013**, *60*, 3176–3182. [CrossRef]

- 7. Cornigli, D.; Reggiani, S.; Gnani, E.; Gnudi, A.; Baccarani, G.; Moens, P.; Vanmeerbeek, P.; Banerjee, A.; Meneghesso, G. Numerical investigation of the lateral and vertical leakage currents and breakdown regimes in GaN-on-Silicon vertical structures. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 5.3.1–5.3.4.

- 8. Lenzlinger, M.; Snow, E.H. Fowler-Nordheim Tunneling into Thermally Grown SiO<sub>2</sub>. *J. Appl. Phys.* **1969**, *40*, 278. [CrossRef]

- 9. Schroeder, D. *Modelling of Interface Carrier Transport for Device Simulation*, 1st ed.; Springer: Wien, Austria, 1994; ISBN 978-3-7091-7368-8.

- 10. Colalongo, L.; Valdinoci, M.; Baccarani, G.; Migliorato, P.; Tallarida, G.; Reita, C. Numerical Analysis of Poly-TFTs Under Off Conditions. *Solid-State Electron.* **1997**, *41*, 627–633. [CrossRef]

- 11. Schenk, A. A Model for the Field and Temperature Dependence of Shockley–Read–Hall Lifetimes in Silicon. *Solid-State Electron.* **1992**, *35*, 1585–1596. [CrossRef]

- 12. Kotani, J.; Tajima, M.; Kasai, S.; Hashizume, T. Mechanism of surface conduction in the vicinity of Schottky gates on heterostructures. *Appl. Phys. Lett.* **2007**, *91*, 093501. [CrossRef]

- 13. Mojaver, H.R.; Valizadeh, P. Reverse Gate-Current of AlGaN/GaN HFETs: Evidence of Leakage at Mesa Sidewalls. *IEEE Trans. Electron Devices* **2016**, *63*, 1444–1449. [CrossRef]

- 14. Hamady, S.; Morancho, F.; Beydoun, B.; Austin, P.; Gavelle, M. Scalable normally-off AlGaN/GaN HEMT using fluorine implantation below the channel. In Proceedings of the Symposium de Gènie Electrique (SGE 2014), ENS Cachan, France, 8–10 July 2014.

- 15. Fang, Z.Q.; Look, D.C.; Wang, X.L.; Han, J.; Khan, F.A.; Adesida, I. Plasma-etching-enhanced deep centers in n-GaN grown by metalorganic chemical-vapor deposition. *Appl. Phys. Lett.* **2003**, *82*, 1562–1564. [CrossRef]

- 16. Bouzid-Driad, S.; Maher, H.; Renvoise, M. Optimization of AlGaN/GaN HEMT Schottky contact for microwave applications. In Proceedings of the 2012 7th European Microwave Integrated Circuit Conference, Amsterdam, The Netherlands, 29–30 October 2012; pp. 119–122.

- 17. Joh, J.; del Alamo, J.A. Impact of electrical degradation on trapping characteristics of GaN high electron mobility transistors. In Proceedings of the 2008 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2008; pp. 1–4. [CrossRef]

- 18. Joh, J.; del Alamo, J.A. Mechanisms for Electrical Degradation of GaN High-electron Mobility Transistors. In Proceedings of the 2006 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 11–13 December 2006; pp. 1–4. [CrossRef]

- 19. Jungwoo, J. Physics of electrical degradation in GaN high electron mobility transistors. Ph.D. Thesis, Massachusetts Institute of Technology, Cambridge, MA, USA, 2009.

- 20. Synopsys Inc. Sentaurus device user guide, Version N-2017.09. 2017.

- 21. Rodríguez, R.; González, B.; García, J.; Nunez, A. Electrothermal DC characterization of GaN on Si MOS-HEMTs. *Solid-State Electron.* **2017**, 137, 44–51. [CrossRef]

- 22. Ambacher, O.; Smart, J.; Shealy, J.R.; Weinmann, N.G.; Chu, K.; Murphy, M.; Sierakowski, A.J.; Schaff, W.J.; Eastman, L.F. Two dimensional electron gases induced by spontaneous and piezoelectric polarization in undoped and doped AlGaN/GaN heterostructures. *J. Appl. Phys.* **2000**, *87*, 334–344. [CrossRef]

Electronics 2018, 7, 210 10 of 10

23. Turuvekere, S.; Karumuri, A.; Rahman, A.; Bhattacharya, A.; DasGupta, A.; DasGupta, N. Gate Leakage Mechanisms in AlGaN/GaN and AlInN/GaN HEMTs: Comparison and Modeling. *IEEE Trans. Electron Devices* **2013**, *60*, 3157–3165. [CrossRef]

- 24. Sze, S.M. MOSFET. In *Physics of Semiconductor Devices*; Wiley: New York, NY, USA, 1981.

- 25. Ghosh, S.; Dasgupta, A.; Khandelwal, S.; Agnihotri, S.; Chauhan, Y.S. Surface-Potential-Based Compact Modeling of Gate Current in AlGaN/GaN HEMTs. *IEEE Trans. Electron Devices* **2015**, *62*, 443–448. [CrossRef]

- 26. Yigletu, F.M.; Khandelwal, S.; Fjeldly, T.A.; Iñiguez, B. Compact Charge-Based Physical Models for Current and Capacitances in AlGaN/GaN HEMTs. *IEEE Trans. Electron Devices* **2013**, *60*, 3746–3752. [CrossRef]

- 27. Rodríguez, R.; González, B.; García, J.; Yigletu, F.M.; Tirado, J.M.; Iñiguez, B.; Núñez, A. Numerical simulation and compact modelling of AlGaN/GaN HEMTs with mitigation of self-heating effects by substrate materials. *Phys. Status Solidi A Appl. Mater.* **2015**, 212, 1130–1136. [CrossRef]

- 28. Kuzmík, J.; Javorka, P.; Alam, A.; Marso, M.; Heuken, M.; Kordos, P. Determination of channel temperature in AlGaN/GaN HEMTs grown on sapphire and silicon substrates using DC characterization method. *IEEE Trans. Electron Devices* **2002**, *49*, 1496–1498. [CrossRef]

- 29. Hamady, S. New Concepts for Normally-Off Power Gallium Nitride (GaN) High Electron Mobility Transistor (HEMT). Ph.D. Thesis, Université Toulouse, Toulouse, France, 2014.

- 30. Efthymiou, L.; Longobardi, G.; Camuso, G.; Hsieh, A.P.S.; Udrea, F. Modelling of an AlGaN/GaN Schottky diode and extraction of main parameters. In Proceedings of the 2015 International Semiconductor Conference (CAS), Sinaia, Romania, 12–14 October 2015; pp. 211–214. [CrossRef]

- 31. Mimouni, A.; Fernández, T.; Rodriguez-Tellez, J.; Tazon, A.; Baudrand, H.; Boussuis, M. Gate Leakage Current in GaN HEMT's: A Degradation Modeling Approach. *Electr. Electron. Eng.* **2012**, *2*, 397–402. [CrossRef]

- 32. Ahmed, N.; Dutta, A.K. Analytical models for the 2DEG concentration and gate leakage current in AlGaN/GaN HEMTs. *Solid-State Electron.* **2017**, *132*, 64–72. [CrossRef]

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).