# Real-time emulation of boost inverter using the Systems Modeling Language and Petri nets

A. Gutierrez, Michael Bressan, Fernando Jimenez, Corinne Alonso

# ► To cite this version:

A. Gutierrez, Michael Bressan, Fernando Jimenez, Corinne Alonso. Real-time emulation of boost inverter using the Systems Modeling Language and Petri nets. Mathematics and Computers in Simulation, 2018, 10.1016/j.matcom.2018.07.011. hal-01962916

# HAL Id: hal-01962916 https://laas.hal.science/hal-01962916

Submitted on 31 Dec 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Real-time Emulation of Boost Inverter Using the Systems Modeling Language and Petri Nets

A. Gutierrez<sup>1-2</sup>, M. Bressan<sup>1</sup>, J.F. Jimenez<sup>1-3</sup>, and C. Alonso<sup>2-3</sup>

<sup>1</sup>Universidad de los Andes, Department of Electrical and Electronic Engineering, Bogotá, Colombia

<sup>2</sup>Université de Toulouse III, UPS; Toulouse F-31400, France <sup>3</sup>LAAS-CNRS. 7 Avenue du Colonel Roche, Toulouse F-31077, France

Email: a.gutierrez75@uniandes.edu.co (A. Gutierrez), alonsoc@laas.fr (C. Alonso)

#### Abstract

A boost inverter is a versatile architecture able to supply DC or AC outputs from diverse alternative energy sources. The most relevant advantage of this multipurpose converter is to provide boosting and inversion in a single stage. The boost inverter has been studied from design and control perspectives with renewable energy sources. However, the real-time emulation of boost inverters is less widespread in literature. In this context, the main contribution of this paper is proposing an innovative methodology based on the Systems Modeling Language and Petri nets to emulate in real-time power converters using the boost inverter as a case of study. This approach develops real-time Hardware-in-the-Loop models using a graphical language and Petri nets. These graphical and Petri net features allow a formal validation of computational and time constraints before implementation in FPGA. The proposed methodology is also able to transform the developed models to the High Level Specification of Embedded Systems for automatic code generation. Comparison of real-time emulations and experimental results shows a suitable trade-off between the model accuracy and the computational time.

*Keywords:* Boost inverter, Hardware-in-the-Loop, SysML, Petri net, real-time emulation, FPGA.

### 1. Introduction

Nowadays, alternative energy sources have increased their integration in power systems. As a result, innovative power converters are required to accomplish the power system conditions [1]. Modern power converters should be robust architectures able to interact with intermittent energy sources and electrical grids [2]. Currently, the boost inverter is a power converter able to achieve these requirements which can be tested using real-time emulations [3].

The boost inverter shows interesting characteristics because provide both 8 boosting and inversion in a single stage [4]. These characteristics improve the 9 power system efficiency [5], decrease the harmonic distortion [6], and increase 10 the system reliability [7]. Authors in [8] introduce the boost inverter and pro-11 pose a nonlinear control to take advantages of this converter. Also, further 12 studies present advanced control strategies to improve the boost inverter per-13 formance as presented by [9][10][11]. Indeed, advanced controllers allow the 14 integration between renewable energy sources and the boost inverter [12][13]. 15 16

According to [14], the integration of boost inverters and renewable en-17 ergy sources requires innovative modeling approaches. For instance, authors 18 in [5] and [6] study the boost inverter interconnection with electrical grids 19 and PV modules. According to [15], the boost inverter can be modeled and 20 integrated in wind power systems. Other works also study the use of boost 21 inverters in hybrid architectures based on batteries, supercapacitors, and fuel 22 cells [16][17]. However, the boost inverter shows a highly nonlinear behavior 23 and control complexity which leads to unusual industrial applications despite 24 their remarkable advantages. As a consequence, the real-time emulation of 25 this power converter provides an interesting alternative for the control system 26 design to encourage their industrial application such as the current integra-27 tion of renewable energies in power systems [18][19]. 28

29

Real-time emulations provide several advantages for the study of power converters [20]. Analyses based on real-time emulations allow evaluating changes under different scenarios [21][22]. A relevant advantage of a realtime approach is to test the safety operation of power converters closer to working conditions using a Hardware-in-the-Loop method [23]. However, the real-time emulation of boost inverters is less widespread in the literature despite its powerful features. 37

In order to contribute in the fields of power electronics modeling and real-time emulation, this study proposes an innovative modeling approach using the graphical Systems Modeling Language (SysML)[24]. In this specific case, the boost inverter is modeled given its special characteristics and potential range of applications in current renewable energy systems. Nevertheless, the mathematical framework and the modeling methodology can also be extended to other power converters.

45

The Systems Modeling Language (SysML) is a general-purpose modeling 46 language for specifying, analyzing, designing, and verifying complex systems 47 that may include hardware, software, information, and procedures [25][26]. 48 SysML provides a systems engineering methodology able to model complex 49 systems and useful to describe systems based on power converters and re-50 newable energies [27]. This study takes advantages of powerful modeling 51 possibilities of SysML to describe power electronics systems for further real-52 time emulation in Field Programmable Gate Arrays (FPGAs) [28][29]. The 53 FPGA is selected as a processing device because of the characteristics of par-54 allel processing, versatility, and adaptability [30][20]. 55

56

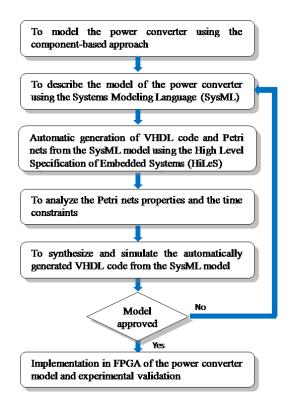

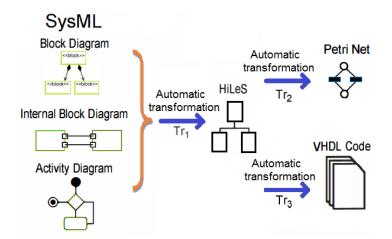

The proposed methodology also employs the High Level Specification 57 of Embedded Systems (HiLeS) to transform automatically the developed 58 SysML models in Petri nets and VHDL code for model implementation in 59 FPGA [31][32]. This study contributes with the use of Petri nets in two 60 directions. First, the Petri nets are employed to verify the structural con-61 sistency of the developed SysML models. Second, the analysis of generated 62 Petri nets allows identifying delays and defining the sequence of operations 63 to achieve the time constraints for real-time emulation of power converters 64 [33]. Fig.1 outlines the proposed modeling methodology through SysML and 65 Petri nets. 66

67

Section II introduces the boost inverter operation and their modeling using a component-based approach. Section III presents the concepts, current state, and scope of real-time emulation methods for power converters. Section IV presents the SysML and the HiLeS - Petri nets framework to emulate in real-time power converters. Section V describes the experimental setup to validate the proposed approach. Finally, emulated and experimental results are discussed.

Figure 1: Modeling methodology based on SysML and Petri nets

# <sup>76</sup> 2. Operation principle of boost inverter and modeling approach

This section introduces the operation principle and theoretical analysis of the boost inverter as a study case for further real-time emulation.

#### 79 2.1. Operation principle

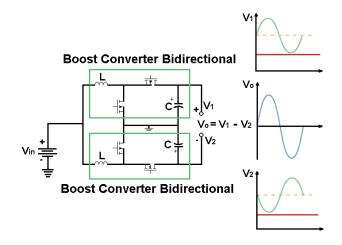

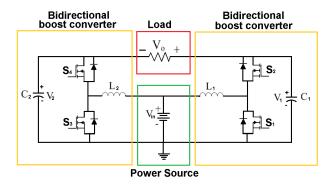

A boost inverter is a power converter build by two complementary bidirectional boost converters [4]. Fig.2 shows the operation principle of the boost converter. The output voltage of a boost inverter is given by eq.(1). When  $v_1$  and  $v_2$  are sinusoidal 180° phase-shifted and dc-biased signals, as shown in eq.(2) and eq.(3), the differential output of the boost inverter is given by eq.(4).

Figure 2: Operation principle of Boost inverter

$$v_o = v_1 - v_2 \tag{1}$$

$$v_1 = V_{dc} + \frac{1}{2} A_o Sin\left(\omega t\right) \tag{2}$$

$$v_2 = V_{dc} + \frac{1}{2} A_o Sin\left(\omega t - \pi\right) \tag{3}$$

$$v_o = A_o Sin\left(\omega t\right) \tag{4}$$

#### 87 2.2. Gain analysis

The gain is the relation between the output and the input voltages of a power converter. The gain is one of the most important parameter for power converters. The ideal boost inverter gain is given by [4], where D is the duty cycle.

$$\frac{V_o}{V_{in}} = \frac{2D - 1}{D(1 - D)}$$

(5)

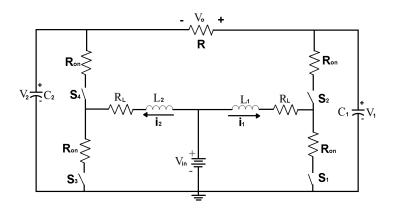

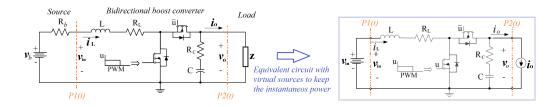

Taking into account the conductive losses, the boost inverter circuit is drawn in Fig.3. Where  $S_1$  to  $S_4$  are ideal switches,  $R_{on}$  represents the conductive losses of switching devices, and  $R_L$  are the conductive losses associated to the inductors [34].

Figure 3: Boost inverter circuit with conductive losses

The boost inverter has two fundamental operation states. In the first operation state,  $S_1 - S_4$  are active. In the second operation state,  $S_2 - S_3$ are active. For the first operation state,

$$v_{L1} = v_{in} - i_1 \left( R_L + R_{on} \right) \tag{6}$$

$$v_{L2} = v_{in} - i_2 \left( R_L + R_{on} \right) - v_2 \tag{7}$$

$$i_{c1} = \frac{v_2 - v_1}{R} \text{ and } i_{c2} = i_2 + \frac{v_1 - v_2}{R}$$

(8)

<sup>100</sup> In the second operation state,

$$v_{L1} = v_{in} - i_1 \left( R_L + R_{on} \right) - v_2 \tag{9}$$

$$v_{L2} = v_{in} - i_2 \left( R_L + R_{on} \right) \tag{10}$$

$$i_{c1} = i_1 + \frac{v_2 - v_1}{R} \text{ and } i_{c2} = \frac{v_1 - v_2}{R}$$

(11)

Applying the principle of inductor volt-second balance and the capacitor charge balance to equations eq.(6) to eq.(11) [35]. Where  $R_s = R_L + R_{on}$ and  $D_1 = 1 - D$ ,

$$\langle V_{L1} \rangle = D \left( V_{in} - I_1 \left( R_s \right) \right) + D' \left( V_{in} - I_1 \left( R_s \right) - V_1 \right) = 0$$

(12)

$$\langle V_{L2} \rangle = D \left( V_{in} - I_2 \left( R_s \right) - V_2 \right) + D' \left( V_{in} - I_2 \left( R_s \right) \right) = 0$$

(13)

$$\langle I_{c2} \rangle = D\left(\frac{V_2 - V_1}{R}\right) + D'\left(I_1 + \frac{V_2 - V_1}{R}\right) = 0$$

(14)

$$\langle I_{c2} \rangle = D\left(I_2 + \frac{V_1 - V_2}{R}\right) + D'\left(I_1 + \frac{V_1 - V_2}{R}\right) = 0$$

(15)

Solving the system of equations from eq.(12) to eq.(15), the boost inverter gain is given by eq.(16) [34].

$$\frac{V_o}{V_{in}} = \frac{2D - 1}{\frac{R_s}{R} \left(\frac{1}{D'} + \frac{D'}{D} - 1\right) + DD'}$$

(16)

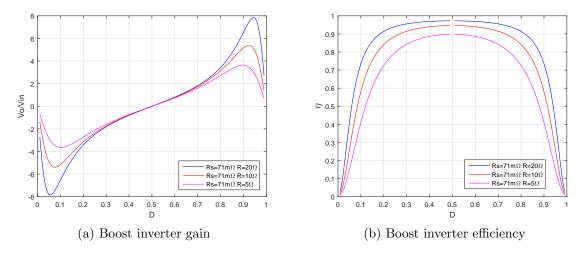

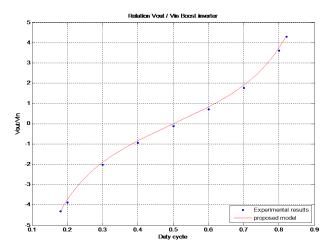

Fig. 4a shows the relationship between the output voltage and the input voltage given a series resistance  $R_s$  associated to conductive and inductance losses and a set of resistive loads R. As shown in Fig. 4a, the gain of a boost inverter can be affected by the load changes. Fig. 4a depicts that an AC voltage can be produced when the duty cycle oscillates around D = 0.5. Finally, eq.(16) determines that the factor  $R_s/R$  limits the boost inverter gain.

Figure 4: Boost inverter gain and efficiency

#### 113 2.3. Efficiency analysis

The efficiency  $\eta$  is another important parameter of power converters. The efficiency is defined as a relation between the output power and the input power. Thus,

$$\eta = \frac{P_{out}}{P_{in}} = \frac{V_{out}I_{out}}{V_{in}I_{in}} = \left(\frac{V_{out}}{V_{in}}\right)\left(\frac{I_{out}}{I_{in}}\right)$$

(17)

Given the following relation for the boost inverter currents,

$$I_{in} = I_1 + I_2 = I_o \left(\frac{2D - 1}{DD'}\right)$$

(18)

<sup>118</sup> Calculating the efficiency  $\eta$  from eq.(16) and eq.(18),

$$\eta = \left(\frac{2D-1}{\frac{R_s}{R}\left(\frac{1}{D'} + \frac{D'}{D} - 1\right) + DD'}\right) \left[\frac{1}{\frac{2D-1}{DD'}}\right]$$

(19)

Fig.4b depicts the boost inverter efficiency  $\eta$  according to eq.(19). Fig.4b 119 shows the influence of the duty cycle on the efficiency. As shown in Fig.4b, 120 variations of  $D \ge 0.8$  and  $D \le 0.2$  impact drastically in the converter effi-121 ciency [18]. Fig. 4a and Fig.4b also show the better operation range between 122  $0.2 \le D \le 0.8$  where variation is more linear and efficiency is higher. Tak-123 ing into account previous results, it is clear that a well developed model 124 is necessary to describe the nonlinear behavior of the boost inverter. Next 125 section describes the component-based approach for boost inverter modeling. 126 127

### <sup>128</sup> 2.4. Component-based approach to model the boost inverter

The previous section showed the non-linearity and behavior of boost in-129 verter which requires innovative modeling approaches. This section intro-130 duces a component-based approach suitable to describe the complex behav-131 ior of power converters which is applied to the boost inverter a case study. 132 This component-based approach is intended to model power converters as 133 building blocks interacting with their environment. This methodology al-134 lows to model the power converter with a high degree of detail disregarding 135 subsequent changes in the power source and load models. 136

The state of the art about modeling of boost inverter is focused on 138 oriented-control approaches [18]. Caceres et .al introduce the model pre-139 sented in [8] and consider for analysis half boost inverter coupled with a 140 fixed source. Approach in [8] simplifies the analysis; however, the dynamic 141 of half boost inverter is disregarded. In [4] is proposed a model to design a 142 slide-mode control on each half boost inverter. According to authors in [4], 143 the output transfer function is evaluated to analyze the boost inverter sta-144 bility. Flores-Bahamonde et .al in [36] assume the boost inverter operation 145 with complementary signals; therefore, two configurations are obtained. In 146 [36], the state equations are given and the second method of Lyapunov is 147 used for stability analysis. According to [37], the proposed model can ex-148 press the converter behavior using a simplify average model. AC operation 149 is represented by a simplified model of the electrical grid [37]. The model is 150 intended to study the harmonic input current impact on the boost inverter 151 [37]. Finally, the boost inverter model in [15] introduces a converter bilinear 152 model from a state-space model considering the grid connection. 153

154

As aforementioned, most of proposed models in literature are intended to 155 control design. Additionally, proposed models simplify the boost inverter be-156 havior, use linear approaches, and disregard the influence of conductive losses. 157 However, these characteristics have an important effect on the efficiency and 158 gain of actual power converters [35]. Another drawback of current models is 159 the lack of scalability and adaptability; therefore, most of these models should 160 be updated when the operation condition changes. For instant, changes in 161 either the type of load or the power source require significant changes in the 162 model. These drawbacks are a disadvantage for real-time emulations because 163 the study of versatile converters such as the boost inverter requires the test 164 under several scenarios. 165

166

In this context, an innovative component-based approach is presented. This methodology explores characteristics of adaptability, scalability, and model integration suitable for the study of power systems built by several types of power sources, converters, and loads. In addition, this method is intended to digital real-time emulations.

172

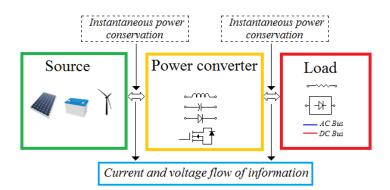

The component-based approach employs the concept of instantaneous power conservation to analyze the power converter systems as structures formed by functional components [18]. Fig.5 shows the general concept about the component-based approach. In this case, the power converter is modeled independently of changes in the power source or the load. This modeling approach uses the flow of information between the power converter and its electrical neighborhood. To achieve this goal, the power converter is modeled with virtual sources able to maintain the equivalent instantaneous power at the input and output ports. The modeling procedure by using the component-based approach is described as follows:

1Step 1: Substitution of the source power model by a virtual voltage source and the load model by a virtual current source. The aim of these changes is to formulate the power converter equations in terms of input and output voltages and currents independently of its electrical neighborhood.

1Step 2: Formulation of the power converter equations in terms of inputs, outputs, and internal parameters. These systems of equations are converted into the discrete domain because this method is intended to digital real-time emulations.

<sup>1</sup>**Step 3:** Formulation of equations for describing the interaction between inputs <sup>192</sup> and outputs with the electrical boundaries.

Figure 5: Component-based modeling approach

The boost inverter modeling applies the component-based approach. Four functional components are identified using this approach. The identified functional components are two bidirectional boost converters, the power source, and the load. Fig.6 shows the functional components of the boost inverter [18].

Figure 6: Boost inverter circuit and functional components

Figure 7: Operation states of bidirectional boost converter modeled with virtual sources

The boost inverter analysis takes as a start point the study of the bidi-199 rectional boost converters. In this case, the bidirectional boost converter is 200 studied using the component-based approach and the instantaneous power 201 conservation. Fig.7 represents the bidirectional boost converter but inter-202 connected to input and output virtual sources. These virtual sources are 203 intended to keep the instantaneous power  $p_n(t) = v_n(t)i_n(t)$  at the input 204 and output ports. For this reason, the input power source is replaced by a 205 voltage source keeping the input current, and the load is replace by a current 206 source keeping the output voltage. The power conservation property allows 207 to model the converter without considering changes in the power source or 208 the load, but only taking into account the information flow with the electrical 209 boundaries (see Fig.5) [18]. 210

211

As shown in Fig.5, the bidirectional boost converter block should interact with the power source and load blocks through information flow. Then, in order to achieve this goal the following mathematical framework is proposed [34].

From circuit in Fig.7, the bidirectional boost converter behavior is given by two operation states represented by the control signal  $u = \{0, 1\}$ . Then, the converter behavior is given by,

$$\frac{di_L}{dt} = \frac{1}{L} \left[ v_{in} - i_L (R_L + R_{on}) - (i_L R_c - i_o R_c + v_c) (1 - u) \right]$$

(20)

$$\frac{dv_c}{dt} = \frac{1}{C} \left[ -i_o + i_L (1-u) \right]$$

(21)

Given the discrete form with a sample time h, and let us consider  $R_s = R_L + R_{on}$ ,

$$i_{L_{k+1}} = \frac{h}{L} [v_{in_k} - i_{L_k} (R_L + R_{on}) - (i_{L_k} R_c - i_{o_k} R_c + v_{c_k}) (1 - u_k)] + i_{L_k}$$

(22)

$$V_{c_{k+1}} = \frac{h}{C} \left[ -i_{o_k} + i_{L_k} (1 - u_k) \right] + v_{c_k}$$

(23)

Finally, the input and output interactions are defined. The output voltage interaction is then,

$$v_{o_k} = v_{c_k} + R_c \left[ i_{L_k} (1 - u_k) - i_{o_k} \right]$$

(24)

Eq.(22) and eq.(24) are the output variables from the bidirectional boost 224 converter block. The calculated  $i_{L_{k+1}}$  can be sent to the power source block 225 and  $v_{o_k}$  is able to be sent to the load block. Furthermore, eq.(22) to eq.(24) 226 are expressed to variables  $v_i$  and  $i_{o_k}$  from associated power source and load 227 blocks. Additional terms in eq.(22) to eq.(24) depend only of internal states 228 and parameters. Then, any change in the power source and load models 229 does not affect the developed converter model. Indeed, this is an advantage 230 for real-time emulation because model operations and execution time can be 231 well defined before model implementation. 232

233

Section IV will integrate the boost bidirectional model with the power source and the load models using the graphical language SysML. This model integration of section IV is proposed to develop real-time emulations. For this reason, before to model the boost inverter in real-time, the next section will introduce the currents state and the scope of real-time emulations in power electronics.

# 240 3. Real-time emulation of power converters

This section describes briefly the basic concepts about real-time emulation, and its current state and scope in power electronics.

243

A real-time emulation of power electronics systems search to reproduce 244 accuracy voltage and current signals in a safety environment. These signals 245 represent the modeled systems and can be used to study control systems or 246 power interactions. This goal requires a fast digital real-time emulator able 247 to solve the equations that model the system [38]. Therefore, in discrete 248 time intervals are produced the output signals equivalent to the emulated 249 system [39]. Two situations can arise from the time constraints to evaluate 250 the model equations. First, the model execution time is shorter than the 251 required time-step. Then, the emulation is considered real-time. In contrast, 252 when emulation solves the equations after the time-step the emulation is con-253 sidered non real-time or offline [39]. 254

255

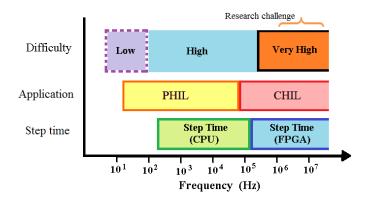

The real-time emulations are classified in two categories [38]. The first 256 category is a full digital real-time emulation. In this case, the emulation 257 occurs inside of the processing device without information interchange with 258 the environment. The second category is the Hardware-in-the-Loop. For this 259 category, an interchange of electrical signals occurs and digital-analog and 260 analog-digital conversion are required [23]. When the Hardware-in-the-Loop 261 system involves an actual controller, it is called a Controller Hardware-in-262 the-Loop (CHIL). Our study is oriented toward Controller Hardware-in-the-263 Loop. In contrast, the emulation that interacts with power transfer is known 264 as a Power Hardware-in-the-Loop (PHIL) [38]. 265

266

According to Faruque et al. [39] a real-time emulator needs to solve an 267 electrical grid-scale model by roughly  $50\mu s$  or a smaller time-step to repro-268 duce electrical transients. Additionally, smaller time-steps are required in 269 power electronics systems because of the high switching frequency of power 270 converters [40]. For Controller Hardware-in-the-Loop, the internal clock of 271 microprocessors for the control system has speed periods of  $1\mu s$  to 10ns. 272 Then, an emulation of these systems requires more computing capability 273 and the ability to emulate in the nanosecond scale [41]. 274

275

Given these features of calculation speed and time constraints, the Field

Programmable Gate Arrays (FPGAs) arise as a suitable devices to achieve 277 the requirements of real-time emulation in power electronics [21]. Fig.8 de-278 picts the frequency range versus simulation complexity [42]. In this figure, 279 the frequency emulation above 100 KHz is feasible for FPGA and represents 280 a research challenge [42]. However, Myaing et .al argue that the main draw-281 back of FPGAs is the complexity for developing code [43]. Indeed, Andina et 282 .al highlight the potential of FPGAs for real-time emulations; however, tools 283 to take more advantages of these devices are still required [44]. For these 284 reasons, the next section describes the SysML and the HiLeS approaches to 285 develop FPGA-based models to contribute with a structural methodology to 286 emulate in real-time power converters. 287

Figure 8: Range of applications and processing devices for real-time emulations

### <sup>288</sup> 4. The SysML and Petri nets to emulate power converters

This section presents the Systems Modeling Language (SysML) [25], the High Level Specification of Embedded Systems (HiLeS) [31], and the Petri nets concepts [45] to develop FPGA-based real-time models of power converters. These models are developed using the component-based approach described in section II with the boost inverter as a study case.

#### 294 4.1. SysML models

The Systems Modeling Language (SysML) is a general-purpose graphical modeling language for specifying, designing, and verifying of engineering systems [25]. The SysML language uses international standardized diagrams to specify the system concepts and architectures. The main diagrams in SysML are the Block Definition Diagrams, the Internal Block Diagrams, and the

Activity Diagrams [25]. The Block Definition Diagrams define the structure

and hierarchy of components in a system. The Internal Block Diagrams describe the interaction between components. Finally, the Activity Diagrams

are intended to model both computational and flow processes.

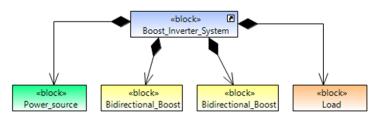

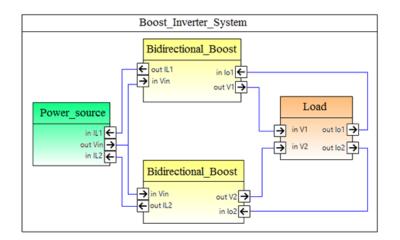

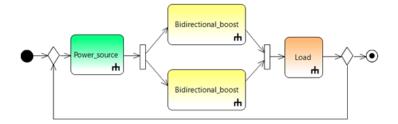

Figure 9: Block Definition Diagram for the boost inverter model

As described in section 2.4, the boost inverter was analyzed as a system 305 built by four functional components. The SysML representation is shown 306 in the Block Definition Diagram of Fig.9. This figure depicts the structural 307 composition of the boost inverter. Fig.10 shows the interaction between the 308 functional components of the boost inverter. This figure represents the Inter-309 nal Block Diagram with the specification of the information flow between the 310 bidirectional converters, the power source, and the load [34]. In this case, the 311 main components are the bidirectional boost converters which interchange 312 current and voltage information with the load and the power source. Finally, 313 the Activity Diagram of Fig.11 represents a simplified sequence of process 314 to evaluate the boost inverter model. In this case, the Activity Diagram 315 represents the operation flow and the concurrency of parallel process. 316 317

The proposed approach allows describing the behavior of each component in contrast with conventional modeling methodologies [18]. As a result, each functional component is modeled with independence of external models. This approach is feasible for modeling current power converters because the interactions should be analyzed for the different types of power sources, converter topologies, and loads [34].

*4.2. Model transformation from SysML to Petri nets and VHDL*

The High Level Specification of Embedded Systems (HiLeS) framework is a free license tool able to transform automatically the SysML diagrams into

Figure 10: Internal Block Diagram for the boost inverter model

Figure 11: Activity Diagram for the boost inverter model

Petri nets and VHDL code [32]. The main advantages of this transformation are the structural and temporal verification of the developed models before implementation.

330

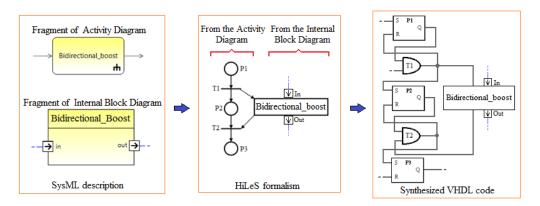

The HiLeS framework automatically transforms each element of the SysML 331 model into an equivalent HiLeS formalism element [31]. The HiLeS formalism 332 integrates in a Petri net representation the Internal Block Diagrams and the 333 Activity Diagrams. Fig.12 depicts an illustrative example of these transfor-334 mations. First, the Internal Block Diagrams are represented by operational 335 blocks which are controlled by a Petri net according to the Activity Dia-336 gram sequence. Then, the control Petri net and the operational blocks are 337 described as a synthesizable VHDL code. At this transformation level, the 338 control Petri net is synthesized in digital components and the operational 339 blocks are represented in VHDL code by Entities and Signals. The transfor-340

<sup>341</sup> mation rules are presented in Reference [46].

The VHDL code automatically generated by the tool takes advantage of the Petri net features to provide a fully parallel architecture intended to decrease the processing time. However, the main constraints of the HiLeS tool are the needs of the algorithm complexity simplification, the code optimization, and the allocation control of the synthesized components. These aspects will be considered in further research on the tool development.

Figure 12: Illustrative example of SysML to VHDL code transformation

Fig.13 shows the SysML transformation chain used by the HiLeS framework. In Fig.13, T1 transforms SysML diagrams to the HiLeS formalism. Stage T2 extracts the Petri net representations from the HiLeS model. Finally, transformation T3 is used to transform the HiLeS description in VHDL code for implementation in FPGA [33]. An illustrative example is described through this section using the bidirectional boost converter model developed in section 2.4.

357

342

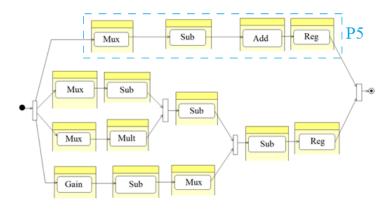

In Fig.14, the Activity Diagram partially represents the flow of operations to calculate the bidirectional boost converter model from eq.(22) to eq.(24). Fig.14 shows the advantage of using Activity Diagrams because these diagrams allow defining the concurrency and interdependency of operations to take advantage of the parallel processing and adaptability of FPGAs. Furthermore, the HiLeS framework transforms automatically the Activity Diagrams in Petri nets according to the rules in [32].

Figure 13: SysML transformations using the HiLeS framework

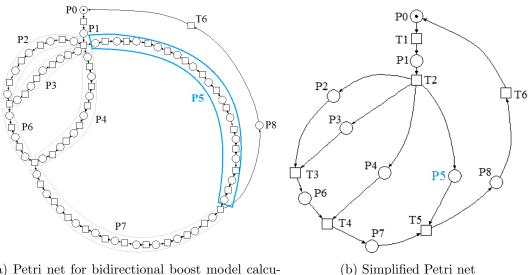

The Petri nets are a graphical and mathematical modeling language 366 for the description of distributed systems. The Petri net elements are the 367 places  $P_n$  (circles), transitions  $T_n$  (rectangles), and arcs (arrows) [45]. Places 368 are connected to transitions by mean of arcs. According to [32], each ele-369 ment from the Activity Diagram is transformed to an equivalent Place-Arc-370 Transition branch. Fig.15a shows the associated Petri net of Fig.14. As 371 example, the sequence of operations  $P_5$  highlighted in the Activity Diagram 372 is translated to a Petri net branch in Fig.15a. A repetitive loop with the 373 transition  $T_6$  is added to the Petri net of Fig.15a to analyze the iterative 374 properties of the equivalent Petri net. Fig.15b shows a simplified version of 375 the Petri net of Fig.15a to illustrate in the next section the formal mathe-376 matical validation. 377

#### 378 4.2.1. Petri nets analysis

The Petri nets and the linear algebra theories allows analyzing the Petri net properties. The main properties of Petri nets are the boundedness, liveness, invariance, and consistency. To accomplish these properties ensure the Petri net stability and the feasible use of computational resources to avoid unexpected behavior after implementation [45].

384

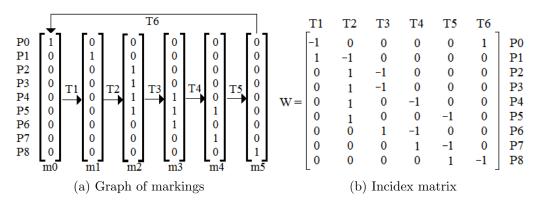

From the simplified Petri net of Fig.15b, the graph of markings is shown Fig.16a. In Petri nets, a change of state is denoted by the movement of tokens or marks (•) from one place to another. A graph of markings represents

Figure 14: Partial Activity Diagram for calculation of the bidirectional boost model

(a) Petri net for bidirectional boost model calculation (b) Sim

Figure 15: Petri net for the bidirectional boost converter model

the possible markings for the analyzed Petri net after transition firing [45]. A marking is a column vector whose components indicate the number of tokens or marks in each place  $(P_n)$ . Fig.16a shows that each place has maximum one token. Then, the simplified Petri net is bounded because it has a limited number of tokens in each place. The interpretation of this property is that the Petri net requires a finite memory space and a finite use of hardware re<sup>394</sup> sources. Furthermore, the graph of markings shows that is possible to reach <sup>395</sup> any marking from any other marking; then, the Petri net is live without <sup>396</sup> deadlocks [45]. An incident matrix **W** denotes in columns the corresponding <sup>397</sup> marking modification when a transition  $T_n$  is firing and to add (1) or remove <sup>398</sup> (-1) tokens [45]. Fig.16b represents the incident matrix of the bidirectional <sup>399</sup> boost converter model.

Figure 16: Petri net representation with linear algebra

A vector of places  $x, x = (p_1, p_2, ..., p_n)$  with  $0 \le p_i$ , which is a solution of  $x^T \cdot W = 0$  is known as a P-invariant and represents the invariant property of Petri nets [45]. Given the incident matrix **W** for the analyzed Petri net and the vector of places x, there is a finite solution for  $x^T \cdot W = 0$  in  $x^T = [4 \ 4 \ 1 \ 1 \ 1 \ 2 \ 3 \ 4]$ . Then, this Petri net is invariant [45].

406

<sup>407</sup> A vector y associated with a firing sequence and solution of  $W \cdot y = 0$ <sup>408</sup> is known as a T-invariant. y represents the consistent property of Petri nets <sup>409</sup> [45]. Given the incident matrix **W** for the analyzed Petri net and the vector <sup>410</sup> of transitions y, there is a finite solution for  $W \cdot y = 0$  in  $y = [1\ 1\ 1\ 1\ 1\ 1]^T$ . <sup>411</sup> Then, this Petri net is consistent [45].

412

As a result, the Petri net for the bidirectional boost converter model is bounded, live, invariant, and consistent [45]. These properties ensure the structural and behavioral stability of the proposed model before implementation in FPGA.

Figure 17: Time graph for the Petri net evolution

The formal validation of Petri nets by means of linear algebra methods is usually validated using computational tools [47]. The use of these automatic analysis tools, such as the integrated tool to HiLeS (TINA - TIme Petri Net Analyzer), allows the formal validation of Petri nets with a large number of places and transitions [47]. Then, developed power converter models in SysML can be transformed to Petri nets for formal Petri net validation without constraint in the Petri net size.

425

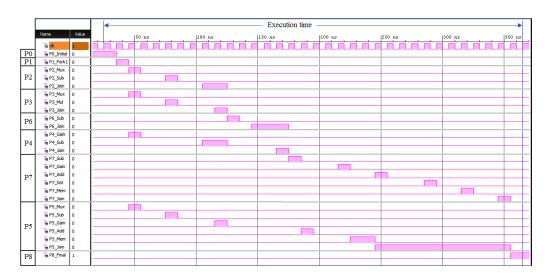

In addition, the HiLeS framework automatically transforms the developed 426 models to VHDL code for FPGA implementation. Then, the Petri net of the 427 bidirectional boost converter model is analyzed by simulating the generated 428 VHDL code. Fig.17 shows the temporal evolution of the model operations. 429 Results in this figure depict the Petri net temporal evolution and the de-430 lays cause by the calculus in each stage. The simulation of Fig.17 allows 431 validating the real-time constraints for the model and identifying the delay 432 problems. In this case, the step time for model calculation is suitable for 433 real-time application given their range in nanoseconds. After validation of 434 the bidirectional boost model characteristics, the entire boost inverter model 435 is integrated and the simulation results are analyzed. 436

437 438

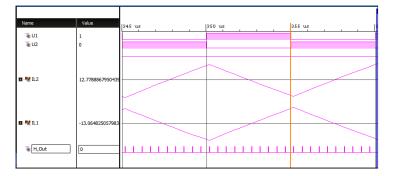

Fig.18 depicts the simulation of the VHDL code for the inductor currents

Figure 18: Simulation results for inductor current with time step around 500nS

<sup>439</sup>  $(I_{L1}, I_{L2})$  of the boost inverter model. Fig.18 shows that the step time for the <sup>440</sup> boost inverter model is around 500nS (sampling signal H\_Out). This step <sup>441</sup> time is significantly lower that the expected switching time  $U = 10\mu s$ . Then, <sup>442</sup> the developed model is able to emulate the boost inverter in real-time given <sup>443</sup> this expected switching time U.

444

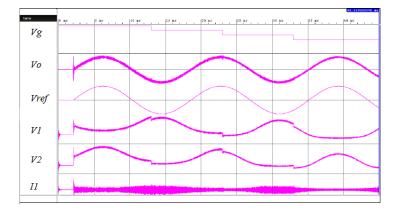

Furthermore, Fig.19 outlines the whole behavior for the boost inverter model driven by a control signal with a Sinusoidal Pulse Width Modulation (SPWM). Simulation of Fig.19 confirms that the developed real-time model is able to follow the dynamic and nonlinear behavior of the boost inverter given a sinusoidal reference. After this suitable results, the next section will describe the experimental setup to compare the developed emulation with an actual boost inverter prototype.

Figure 19: VHDL simulation of boost inverter real-time model

### 452 5. Experimental test to validate the proposed approach

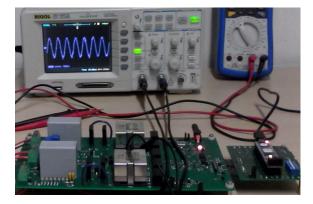

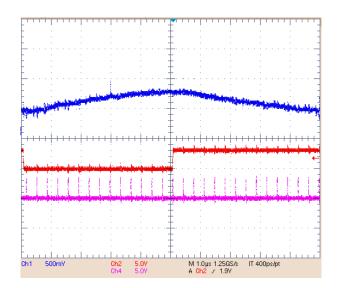

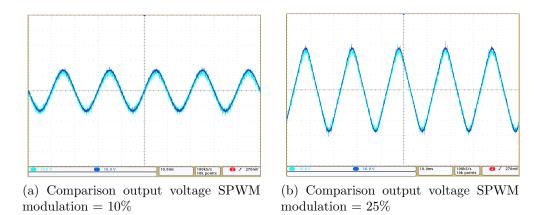

The developed boost inverter model is implemented in FPGA and vali-453 dated in real-time against the experimental test of a physical boost inverter 454 (Fig.20). For validation, a Sinusoidal Pulse Width Modulation (SPWM) 455 controls at the same time the boost inverter model and the boost inverter 456 prototype. The digital signals from the FPGA model are transformed in 457 analogical signals using high speed Digital-to-Analogical converters. Then, 458 the analogical signals are scaled and compared with the actual output sensor 459 signals. Table 1 lists the parameters for the experimental setup. 460 461

Figure 20: Experimental test of boost inverter prototype

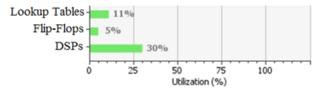

The VHDL code automatically generated from the SysML models is syn-462 thesized in FPGA. In this study, a Zynq-7Z020 - Artix7 series FPGA is used 463 to implement the developed model. The Vivado Design Suite WebPACK<sup>TM</sup> 464 of Xilinx provides the VHDL synthesis, simulation, and configuration file for 465 model implementation in FPGA. Fig.21 summaries the resource utilization 466 after synthesis with an important use of the dedicated Digital Signal Pro-467 cessors (DSPs) given the floating-point operations for high model accuracy. 468 Synthesis results also showed that the execution time is around 350ns which 469 agrees with the expected Petri net analysis. In addition, the ratio between 470 the execution time and the time step is approximately 70% where the differ-471 ence is reserved to the high speed DAC communication. 472

473

Fig.22 depicts the DC comparison between the gain for the FPGA-based emulation and actual boost inverter. Comparison of emulated and physi-

Table 1: Parameters for the experimental validation

| Parameter       | Value                                       |  |  |

|-----------------|---------------------------------------------|--|--|

| $L_1 - L_2$     | $47 \ \mu H$                                |  |  |

| $R_L$           | $6m\Omega$                                  |  |  |

| $C_1 - C_2$     | $10 \; \mu F$                               |  |  |

| $R_c$           | $50  m\Omega$                               |  |  |

| $S_1 - S_4$     | C3M0065090D - SiC MOSFET                    |  |  |

| $R_{on}$        | $65m\Omega$                                 |  |  |

| DriverMOSFET    | 1EDI20N12AF                                 |  |  |

| $SPWM \ signal$ | $F_m = 50 \text{Hz} \ F_c = 100 \text{KHz}$ |  |  |

| DAC             | High speed - $AD5541$                       |  |  |

| FPGA            | Zynq-7Z020 - XC7Z020                        |  |  |

Figure 21: FPGA utilization after synthesis

Figure 22: Boost inverter gain (red line - emulation, blue dot - prototype)

476 cal boost inverter gains shows the FPGA-based emulation accuracy. These

results also agree with the theoretical gain of eq.(16). Emulation results 477 of Fig.23 allow verifying the experimental time step speed in comparison 478 with the switching time for the emulated inductor currents. The boost in-479 verter power results are listed in Table 2 with suitable agreement between 480 the emulation and the experimental results. Finally, results in Fig.24 show 481 the synchronization between the emulated and the physical boost inverter 482 for two percentages of modulation SPWM. In both cases, the results allow 483 confirming the suitable performance of developed emulator to follow the non-484 linear and complex behavior of the boost inverter. In the next section, the 485 results are discussed. 486

| Table 2: Boost inverter power result |

|--------------------------------------|

|--------------------------------------|

|                   | SPWM Modulation $10\%$ |              | SPWM Modulation $25\%$ |              |

|-------------------|------------------------|--------------|------------------------|--------------|

|                   | Emulation              | Experimental | Emulation              | Experimental |

| Input power (W)   | 33.4                   | 33.3         | 187.6                  | 186.5        |

| Output power (W)  | 30.8                   | 30.3         | 167.0                  | 164.1        |

| Efficiency $\eta$ | 0.92                   | 0.91         | 0.89                   | 0.88         |

Figure 23: Time step for emulation of inductor current (blue - inductor current, red - control signal, magenta - time step)

Figure 24: Comparison of emulated and experimental output voltages of the boost inverter

#### 487 6. Results and discussion

Fig.22 shows the gain relation for the proposed emulation model and the actual boost inverter. For this gain comparison, the Medium Square Error  $MSE = \left(\sum_{i=1}^{n} (e_i)^2\right)/n$  is MSE=0.01. The Medium Absolute Error  $MSE = \left(\sum_{i=1}^{n} |e_i|\right)/n$  is MAE=0.093. Then, the gain results validate the suitable accuracy of the real-time emulation model.

493

Fig.23 depicts the inductor current, which is the faster signal, the control signal, and the model sampling signals. These results show that the time for the sampling signal allows calculating the model for the faster signal of the system. This case of study assumes a control signal with switching time of  $10\mu S$  and a time step 500nS suitable to evaluate the model.

499

In Fig.24 both emulated and physical signals are synchronized and compared. Fig.24a and Fig.24b show that the emulated signal is able to follow the behavior of the actual boost inverter in a wide range of SPWM variation. These results confirm that the proposed methodology is suitable to generate models for real-time emulation with a high degree of accuracy.

505

These experimental and emulated results have shown that the proposed methodology based on SysML and Petri nets can contribute to the research challenges discussed in section 3. The time step and accuracy achieved in this study of case are in the expected region of research proposed by Lauss *et .al* [42] with suitable results. Finally, the proposed approach has shown <sup>511</sup> its potential to decrease the gap between the real-time modeling and the <sup>512</sup> complex implementation in FPGA as suggested by Andina *et .al* [44]. <sup>513</sup>

## 514 7. Conclusion

This paper has presented a modeling methodology based on SysML and 515 Petri nets able to model power converters. This study of case was focused on 516 the boost inverter with appropriate results. This methodology identified the 517 boost inverter functional components and their interactions by means of a 518 component-based approach. Furthermore, the bidirectional boost converter, 519 as main functional component of the boost inverter, was analyzed in detail 520 and subsequently integrated to the boost inverter for a real-time emulation. 521 The real-time emulation and experimental results provided a suitable model 522 accuracy and time performance. As a consequence, the proposed methodol-523 ogy has shown its potential to model power converters. In future work, this 524 methodology can be applied to other power systems with different types of 525 energy resources, converter topologies, and nonlinear loads. 526

### 527 Acknowledgements

The authors acknowledge the support provided by the Andes University, the Laboratory for Analysis and Architecture of Systems (LAAS-CNRS), and the Paul Sabatier University in the framework of an international joint supervision PhD. thesis.

#### 532 8. References

- [1] M. Jamil, B. Hussain, M. Abu-Sara, R. J. Boltryk, and S. M. Sharkh,

"Microgrid power electronic converters: State of the art and future challenges," in 2009 44th International Universities Power Engineering Conference (UPEC), pp. 1–5, Sept 2009.

- [2] S. M. Sharkh, M. A. Abusara, G. I. Orfanoudakis, and B. Hussain,

*Power electronic converters for microgrids*. John Wiley and Sons, 2014.

[3] S. Danyali, S. H. Hosseini, and G. B. Gharehpetian, "New extendable

single-stage multi-input dc-dc-ac boost converter," *IEEE Transactions*on Power Electronics, vol. 29, pp. 775–788, Feb 2014.

- [4] R. Caceres and I. Barbi, "A boost dc-ac converter: operation, analysis, control and experimentation," in *Industrial Electronics, Control, and Instrumentation, 1995.*, Proceedings of the 1995 IEEE IECON 21st International Conference on, vol. 1, pp. 546–551 vol.1, Nov 1995.

- [5] Y. Fang and X. Ma, "A novel pv microinverter with coupled inductors and double-boost topology," *IEEE Transactions on Power Electronics*, vol. 25, pp. 3139–3147, Dec 2010.

- [6] H. Renaudineau, D. Lopez, F. Flores-Bahamonde, and S. Kouro,

"Flatness-based control of a boost inverter for pv microinverter application," in 2017 IEEE 8th International Symposium on Power Electronics for Distributed Generation Systems (PEDG), pp. 1–6, April 2017.

- [7] E. Hofreiter and A. M. Bazzi, "Single-stage boost inverter reliability

in solar photovoltaic applications," in 2012 IEEE Power and Energy

*Conference at Illinois*, pp. 1–4, Feb 2012.

- [8] R. O. Caceres and I. Barbi, "A boost dc-ac converter: analysis, design, and experimentation," *IEEE Transactions on Power Electronics*, vol. 14, pp. 134–141, Jan 1999.

- [9] P. Sanchis, A. Ursaea, E. Gubia, and L. Marroyo, "Boost dc-ac inverter: a new control strategy," *IEEE Transactions on Power Electronics*, vol. 20, pp. 343–353, March 2005.

- [10] D. B. W. Abeywardana, B. Hredzak, and V. G. Agelidis, "A rule-based controller to mitigate dc-side second-order harmonic current in a singlephase boost inverter," *IEEE Transactions on Power Electronics*, vol. 31, pp. 1665–1679, Feb 2016.

- [11] R. J. Wai, Y. F. Lin, and Y. K. Liu, "Design of adaptive fuzzy-neuralnetwork control for a single-stage boost inverter," *IEEE Transactions* on Power Electronics, vol. 30, pp. 7282–7298, Dec 2015.

- <sup>569</sup> [12] D. B. W. Abeywardana, B. Hredzak, and V. G. Agelidis, "A fixed<sup>570</sup> frequency sliding mode controller for a boost-inverter-based battery<sup>571</sup> supercapacitor hybrid energy storage system," *IEEE Transactions on*<sup>572</sup> *Power Electronics*, vol. 32, pp. 668–680, Jan 2017.

- <sup>573</sup> [13] D. Lopez, F. Flores-Bahamonde, S. Kouro, M. A. Perez, A. Llor, and

L. Martnez-Salamero, "Predictive control of a single-stage boost dc-ac

photovoltaic microinverter," in *IECON 2016 42nd Annual Conference*of the *IEEE Industrial Electronics Society*, pp. 6746–6751, Oct 2016.

- <sup>577</sup> [14] S. Danyali, S. H. Hosseini, and G. B. Gharehpetian, "New extendable

<sup>578</sup> single-stage multi-input dc-dc/ac boost converter," *IEEE Transactions*<sup>579</sup> on Power Electronics, vol. 29, pp. 775–788, Feb 2014.

- [15] F. Flores-Bahamonde, H. Valderrama-Blavi, J. M. Bosque, A. Leon-Masich, and L. Martinez-Salamero, "Grid-connected boost inverter for small-wind urban integration: Analysis and design," in *IECON* 2012 - 38th Annual Conference on *IEEE Industrial Electronics Society*, pp. 433–439, Oct 2012.

- [16] M. Jang and V. G. Agelidis, "A boost-inverter-based, battery-supported,

fuel-cell sourced three-phase stand-alone power supply," *IEEE Transactions on Power Electronics*, vol. 29, pp. 6472–6480, Dec 2014.

- [17] D. B. W. Abeywardana, B. Hredzak, and V. G. Agelidis, "Single-phase grid-connected lifepo4 battery-supercapacitor hybrid energy storage system with interleaved boost inverter," *IEEE Transactions on Power Electronics*, vol. 30, pp. 5591–5604, Oct 2015.

- [18] A. Gutierrez, Study of Photovoltaic System Integration in Microgrids through Real-Time Modeling and Emulation of its Components Using HiLeS. PhD thesis, Université Toulouse III - Universidad de los Andes, 2017.

- [19] G. Parma and V. Dinavahi, "Real-time digital hardware simulation of

power electronics and drives," in 2007 IEEE Power Engineering Society

*General Meeting*, pp. 1–1, June 2007.

- [20] A. Myaing and V. Dinavahi, "Fpga-based real-time emulation of power

electronic systems with detailed representation of device characteris tics," *IEEE Transactions on Industrial Electronics*, vol. 58, pp. 358–368,

Jan 2011.

- [21] . Lucia, I. Urriza, L. A. Barragan, D. Navarro, . Jimenez, and J. M. Bur dio, "Real-time fpga-based hardware-in-the-loop simulation test bench

- <sup>605</sup> applied to multiple-output power converters," *IEEE Transactions on* <sup>606</sup> *Industry Applications*, vol. 47, pp. 853–860, March 2011.

- [22] D. Ocnasu, Modélisation, Commande et Simulation Temps-Réel Hybride

des Systèmes de Génération Non Conventionnels. PhD thesis, Université

Joseph Fourier, France, 2008.

- [23] S.-J. Oh, C.-H. Yoo, I.-Y. Chung, and D.-J. Won, "Hardware-in-theloop simulation of distributed intelligent energy management system for

microgrids," *Energies*, vol. 6, no. 7, pp. 3263–3283, 2013.

- <sup>613</sup> [24] S. Friedenthal and A. M. and, A Practical Guide to SysML, Third Edi-<sup>614</sup> tion: The Systems Modeling Language. MK, 3rd ed., 2015.

- <sup>615</sup> [25] M. Hause, F. Thom, and A. Moore, "Inside sysml," *Electronics Systems* <sup>616</sup> and Software, vol. 3, pp. 20–25, June 2005.

- <sup>617</sup> [26] D. Dori, *Model-Based Systems Engineering with OPM and SysML*, <sup>618</sup> vol. 1. Springer, first ed., 2016.

- [27] K. Nasraoui, N. Lakhoua, and L. E. Amraoui, "Study and analysis of micro smart grid using the modeling language sysml," in 2017 International Conference on Green Energy Conversion Systems (GECS), pp. 1– 8, March 2017.

- [28] A. Gutierrez, H. Chamorro, and J. Jimenez, "Hardware-in-the-loop based sysml for model and control design of interleaved boost converters," in *Control and Modeling for Power Electronics (COMPEL), 2014 IEEE 15th Workshop on*, pp. 1–6, June 2014.

- [29] D. Rosenberg and S. Mancarella, *Embedded Systems Development using* SysML, vol. 1. OMG, first ed., 2010.

- [30] E. Monmasson, L. Idkhajine, and M. W. Naouar, "Fpga-based controllers," *IEEE Industrial Electronics Magazine*, vol. 5, pp. 14–26, March

2011.

- [31] F. Jimenez, Specification et Conception de Micro-systemes Bases sur des *Circuits Asynchrones.* PhD thesis, Institut National des Sciences Appliquees (Toulouse, Fra), LAAS-CNRS (Toulouse, Fra), Uniandes (Bogota, Col)., 2000.

- [32] H. Hoyos, F. Jimenez, R. Casallas, and D. Correal, "Tucan virtual

prototype generation and time constraints analysis of real-time embedded systems," *Design Automation for Embedded Systems*, vol. 17, no. 1,

p. 129165, 2013.

- [33] A. Gutierrez, H. R. Chamorro, L. F. L. Villa, J. F. Jimenez, and

C. Alonso, "Sysml methodology for hil implementation of pv models,"

in Power Electronics and Applications (EPE'15 ECCE-Europe), 2015

17th European Conference on, pp. 1–7, Sept 2015.

- [34] A. Gutierrez, M. Bressan, F. Jimenez, and C. Alonso, "Development of boost inverter sysml model for hardware-in-the-loop simulations," in *ELECTRIMACS*, 2017.

- [35] R. W. Erickson, Fundamentals of Power Electronics. Chapman and Hall,

second ed., 1997.

- [36] F. Flores-Bahamonde, H. Valderrama-Blavi, J. M. Bosque-Moncusi,

G. Garcia, and L. Martinez-Salamero, "Using the sliding-mode control approach for analysis and design of the boost inverter," *IET Power Electronics*, vol. 9, no. 8, pp. 1625–1634, 2016.

- [37] D. B. W. Abeywardana, B. Hredzak, and V. G. Agelidis, "A rule-based controller to mitigate dc-side second-order harmonic current in a singlephase boost inverter," *IEEE Transactions on Power Electronics*, vol. 31, pp. 1665–1679, Feb 2016.

- [38] D. Maksimovic, A. M. Stankovic, V. J. Thottuvelil, and G. C. Verghese,

"Modeling and simulation of power electronic converters," *Proceedings* of the IEEE, vol. 89, pp. 898–912, Jun 2001.

- [39] M. D. O. Faruque, T. Strasser, G. Lauss, V. Jalili-Marandi, P. Forsyth,

C. Dufour, V. Dinavahi, A. Monti, P. Kotsampopoulos, J. A. Martinez, K. Strunz, M. Saeedifard, X. Wang, D. Shearer, and M. Paolone,

"Real-time simulation technologies for power systems design, testing,

and analysis," *IEEE Power and Energy Technology Systems Journal*,

vol. 2, pp. 63–73, June 2015.

- [40] N. Lin and V. Dinavahi, "Behavioral device-level modeling of modular

multilevel converters in real time for variable-speed drive applications,"

- IEEE Journal of Emerging and Selected Topics in Power Electronics,

vol. 5, pp. 1177–1191, Sept 2017.

- [41] T. Liang and V. Dinavahi, "Real-time system-on-chip emulation of electro-thermal models for power electronic devices via hammerstein configuration," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. PP, no. 99, pp. 1–1, 2017.

- [42] G. F. Lauss, M. O. Faruque, K. Schoder, C. Dufour, A. Viehweider, and J. Langston, "Characteristics and design of power hardware-in-theloop simulations for electrical power systems," *IEEE Transactions on Industrial Electronics*, vol. 63, pp. 406–417, Jan 2016.

- [43] A. Myaing and V. Dinavahi, "Fpga-based real-time emulation of power electronic systems with detailed representation of device characteristics," in 2011 IEEE Power and Energy Society General Meeting, pp. 1–11, July 2011.

- [44] J. J. Rodriguez-Andina, M. D. Valdes, and M. J. Moure, "Advanced features and industrial applications of fpgas a review," *IEEE Transactions on Industrial Informatics*, vol. 11, pp. 853–864, Aug 2015.

- [45] D. Rene and H. Alla., Discrete, Continuous, and Hybrid Petri Nets.

Springer, 2005.

- [46] C. Arcos, "Hiles-pl : un framework para la construcción de líneas especializadas en el diseño de sistemas embebidos," Master's thesis, Universidad de los Andes, 2012.

- [47] B. Berthomieu and F. Vernadat, "Time petri nets analysis with tina,"

in *Quantitative Evaluation of Systems*, 2006. QEST 2006. Third International Conference on, pp. 123–124, Sept 2006.