## Hardware-in-the-loop simulation of PV systems in micro-grids using SysML models

A. Gutierrez, Harold Chamorro, J. Jimenez, Luiz Fernando Lavado Villa, Corinne Alonso

#### ▶ To cite this version:

A. Gutierrez, Harold Chamorro, J. Jimenez, Luiz Fernando Lavado Villa, Corinne Alonso. Hardware-in-the-loop simulation of PV systems in micro-grids using SysML models. IEEE 16th Workshop on Control and Modeling for Power Electronics (COMPEL 2015), IEEE, Jul 2015, Vancouver, Canada. 10.1109/COMPEL.2015.7236466 . hal-01963537

### HAL Id: hal-01963537 https://laas.hal.science/hal-01963537v1

Submitted on 30 Dec 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Hardware-in-the-Loop Simulation of PV Systems in Micro-grids Using SysML Models

A. Gutierrez<sup>1-3</sup>, H.R. Chamorro<sup>2</sup>, J.F. Jimenez<sup>1</sup>, L.F.L. Villa<sup>3-4</sup>, C. Alonso<sup>3-4</sup>

<sup>1</sup>Universidad de los Andes, Department of Electrical and Electronic Engineering, Bogotá, Colombia

<sup>2</sup>KTH Royal Institute of Technology, Stockholm, Sweden

<sup>3</sup>Univ. de Toulouse, Univ. Paul Sabatier, LAAS, F-31400, Toulouse, France

<sup>4</sup>CNRS; LAAS; 7 Avenue du Colonel Roche, F-31077, Toulouse, France

Email: {a.gutierrez75; fjimenez}@uniandes.edu.co, hr.chamo@ieee.org, {luiz.villa; alonsoc}@laas.fr

Abstract—This paper outlines a methodology for modeling photovoltaic systems in embedded hardware. This methodology uses the HiLeS platform to transform SysML models in Petri nets and generate VHDL code. The proposed methodology is intended for Hardware-in-the-Loop simulations of power converters and PV panels in microgrids. In addition, this methodology allows the design of MPPT controllers for their direct implementation in FPGA.

Index Terms—Photovoltaic, Hardware-in-the-Loop, FPGA, SysML, Petri net, Boost converter, MPPT.

#### I. Introduction

Currently, the extensive use of power electronics in microgrids has increased their complexity [1] [2]. As a consequence, new strategies are needed for real-time simulation and control systems design in power electronics [3]. Indeed, high switching frequency of power converters increase the processing speed requirements of controllers [4] [5]. As a consequence, high performance devices are required to accomplish the performance requirements of these power electronics systems. Taking into account the previous reasons, FPGA is a suitable option to implement Hardware-in-the-Loop models of power electronics and control electronic systems in micro-grids [6]. However, designing and implementation of advanced microgrids models requires a structural design methodology. In order to accomplish these design requirements, the HiLeS formalism (High Level Specification of Embedded Systems) is presented as a design methodology for developing Hardwarein-the-Loop simulations of power electronics in micro-grids. In addition, the HiLeS formalism through the HiLeS platform allows to validate and transform the SysML diagrams in Petri nets and VHDL code for implementations in FPGA [7]. This representation in Petri nets also allows a formal net structural analysis to avoid undesired computational behavior [8]. In addition, the automatic code generation provided by the HiLeS platform decreases the time of design and increase productivity.

In section II is presented a general description of the HiLeS platform. Section III shows the mathematical model of a PV panel used in this document. In section IV the numerical model of a Boost converter is analyzed. Section V presents a conventional MPPT controller, and section VI the control

Petri net of the system is shown. Finally, simulations and experimental result are presented in section VII.

## II. HILES PLATFORM FOR HIL SIMULATIONS OF MICRO-GRIDS

Hardware-in-the-Loop (HIL) emulations base on FPGA require tools to decrease the complexity through the design process. As a result, HiLeS platform provides a tool for designers to generate high level descriptions of embedded systems defining the functional composition, hierarchy and structure [9]. HiLeS platform is based on transformations from SysML to Petri nets and VHDL code for formal validation and hardware implementation.

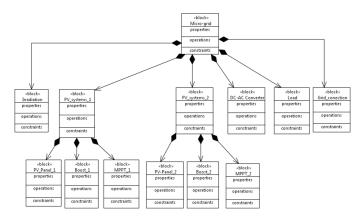

Fig. 1: Partial *Block Definition Diagram* of micro-grid based on PV systems.

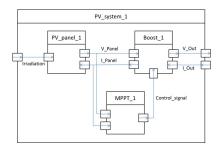

1) SysML Models: SysML is an international standard language for modeling engineering systems [10]. Representative diagrams of SysML are Block Definition Diagrams, Internal Block Diagrams, and Activity Diagrams. SysML uses Block Definition Diagrams (BDD) to describe structural composition of systems, and Internal Block Diagram (IBD) to define the interconnections among the system components. Furthermore, SysML describe the system behavior by means of Activity Diagrams. Fig.1 shows the partial Block Definition Diagram (BDD) of a micro-grid based on PV systems. Fig.2 shows the partial Internal Block Diagram (IBD) for describing the interconnections among PV system components. The use of

SysML diagrams provides and structural design strategy which allows integrating several engineering fields in a common standard.

Fig. 2: Partial *Internal Block Diagram* of a PV system in a micro-grid.

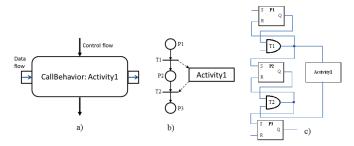

2) From SysML Models to Petri nets: Main advantage of using Activity Diagrams in HiLeS platform is the representation in Petri nets according to the transformation rules defined in [11]. This representation based on Petri nets allows a formal net structural analysis in order to avoid undesired computational behavior. Furthermore, the transformation rules from SysML models to control Petri nets allows the automatic VHDL code generation for implementation in FPGA (Fig.3).

Fig. 3: a) Activity Diagram Component b) HiLeS Control Petri Net c) Equivalent synthesized VHDL code.

#### III. MATHEMATICAL MODEL OF PV PANEL

Photovoltaic panels can be modeled using the single diode circuit [12]. Let  $I_{ph}$  be the light generated current, under constant temperature conditions, the  $I_{ph}$  is proportional to the solar irradiance  $S_R$  where  $I_{ph}=GS_R$ . The characteristics of the PV cell with temperature constant are given by:

$$G S_R - I_0 \left( e^{\frac{V_D}{V_t}} - 1 \right) - \frac{V_D}{R_p} - I_{pv} = 0$$

(1)

A PV panel is built by N photovoltaic cells connected in series; therefore, the PV panel voltage is given by  $V_{panel}=N$  ( $V_D-R_sI_{pv}$ ). From equation (1),  $V_D$  can be expressed as.

$$e^{\frac{V_D}{V_t}} = \frac{1}{I_0 R_p} (G S_R R_p - I_{pv} R_p + I_0 R_p - V_D)$$

(2)

Hardware implementation of analytical PV panel model from (2) is developed by a numerical method. Using the

Newton-Raphson method [13], the term  $V_D$  in equation (3) can be found by iteration of:

$$V_{D_{n+1}} = V_{D_n} - V_t \left( I_{pv} R_p - G S_R R_p + I_0 R_p e^{\frac{V_{D_n}}{V^t}} - I_0 R_p + V_{D_n} \right) I_0 R_p e^{\frac{V_{D_n}}{V^t}} + V_t$$

(3)

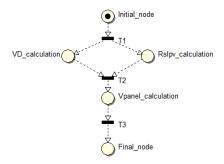

Fig. 4: Partial Activity Diagram of PV panel model.

Fig.4 describes the partial activity diagram for solving the PV panel model, and Fig.5 shows the associated control Petri net which is appropriate for implementation on FPGA.

Fig. 5: Partial control Petri net of PV panel model.

#### IV. NUMERICAL MODEL OF BOOST CONVERTER

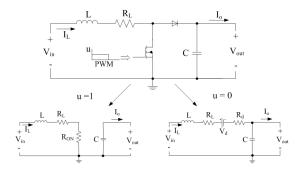

Boost converters are power converters of wide application in photovoltaic systems. Fig.6 shows a conventional boost converter circuit including losses. The behavior of a boost converter depends on the PWM signal. The inductor voltage and the capacitor current as function of the control signal u are given by eq.(4) and eq.(5).

$$\frac{di_L}{dt} = \frac{1}{L} [V_{in} - i_L R_L - (i_L R_{on}) u - (V_d + i_L R_d + i_L R_c - i_o R_c + V_c) (1 - u)]$$

(4)

$$\frac{dv_c}{dt} = \frac{1}{C} \left[ -i_o + i_L (1 - u) \right] \tag{5}$$

Given the discrete form of (4) and (5) with a sample time h,

$$i_{L}(k+1) = \frac{h}{L} [V_{in}(k) - i_{L}(k)R_{L} - (i_{L}(k)R_{on})u(k) - (V_{d} + i_{L}(k)R_{d} + i_{L}(k)R_{c} - i_{o}(k)R_{c} + V_{c}(k))(1 - u(k))] + i_{L}(k)$$

(6)

$$V_c(k+1) = \frac{h}{C} \left[ -i_o(k) + i_L(k)(1 - u(k)) \right] + V_c(k)$$

(7)

Eq.(6) and eq.(7) are intended to use in circuits with impedance as load. However, in the specific case of PV systems, the boost converter load is associated to constant DC voltage source.

Fig. 6: Boost converter.

Therefore, boost converter control regulates the output current toward the constant DC voltage source. To model in SysML both situations with impedance and constant DC voltage source the following analysis is proposed. The output voltage is given by,

$$V_o(k) = V_c(k) + R_c \left[ i_L(k)(1-u) - i_o(k) \right] \tag{8}$$

The model with impedance as load can be calculated from eq.(8) and eq.(9).

$$i_o(k) = \frac{V_o(k)}{Z} \tag{9}$$

On the other hand, the model with constant DC voltage source as load  $V_o(k) = V_B$  is given by,

$$V_B = V_c(k) + R_c \left[ i_L(k)(1 - u) - i_o(k) \right]$$

(10)

Thus,

$$i_o(k) = i_L(k)(1-u) + \frac{V_c(k) - V_B}{R_c}$$

(11)

Fig.7 depicts the partial *Activity Diagram*, and Fig.8 presents the equivalent control Petri net of boost converter model to describe the calculation sequence.

Fig. 7: Partial Activity Diagram of boost converter model.

Fig. 8: Partial control Petri net of boost converter model.

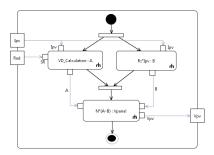

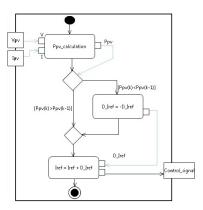

Fig. 9: Partial Activity Diagram of MPPT controller.

#### V. MPPT CONTROLLER

Currently, there are many different MPPT techniques [14] [15]; these are used in PV arrays to obtain the maximum power available from the system. The most popular algorithms is the Perturb and Observe method.

Fig.9 shows a partial MPPT based on the Perturb and Observe method modeled by means of *Activity Diagrams*, and Fig.10 shows the equivalent Petri net. Indeed, HiLeS methodology is focus on structural composition which allows assessing several MPPT methods for subsequent implementation in dedicated embedded hardware on FPGA.

Fig. 10: Partial control Petri net of MPPT controller.

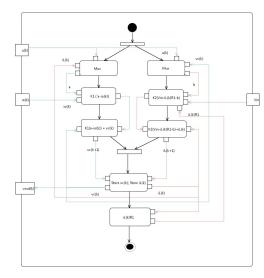

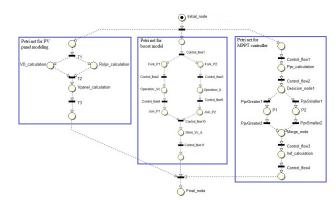

#### VI. CONTROL PETRI NET OF PV SYSTEM MODEL

According to the description of the PV system in Fig.2, the main system components are the PV panel, the boost converter, and the MPPT controller. The behavior of each components has been modeled by means of Activity Diagrams with their equivalent control Petri nets (Fig.5, Fig.8, Fig.10). As a consequence, a general control Petri net is proposed according to [11] in Fig.11. This general control Petri net describes in concurrent way the behavior of the PV system model. In fact, the proposed methodology allows taking advantage of the high performance and concurrent processing of FPGAs. Finally, description of PV system model in terms of Petri nets is suitable to verify theoretical properties of the associated Petri nets for structural and behavioral analysis before implementation. In this case, such analysis shows that the general Petri net of the PV system model is bounded, consistent, and live. As a result, the proposed control Petri net can be implemented in FPGA with low probability of undesired behavior.

#### VII. RESULTS

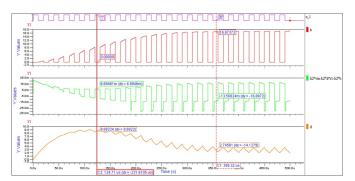

In order to validate the proposed methodology, VHDL simulations in the software Systen Vision are taken as reference. Fig.12 shows the calculation sequence of the inductor current simulation for a boost converter modeled by SysML and HiLeS platform.

Fig.13 shows the inductor current and the capacitor voltage simulations for the boost converter model; these results use math operations in float point format according to the IEEE

Fig. 11: Partial general control Petri net of the PV system model.

Fig. 12: Inductor current of boost converter model using VHDL code from HiLeS platform.

754 standard. Simulation results show coherence with theoretical models.

Fig. 13: Capacitor voltage of boost converter model using VHDL code from HiLeS platform.

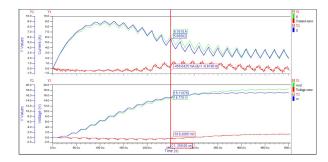

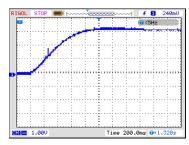

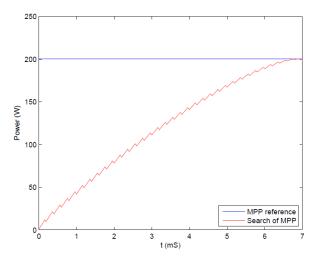

In Fig.14, the result shows the Hardware-in-the-Loop implementation for Boost converter model. In addition, Fig.15 presents the suitable search action of the MPPT controller given as a reference a commercial PV panel under known irradiance.

#### VIII. CONCLUSION

This paper shows a methodology to implement PV system models in embedded hardware. The methodology is based on HiLeS platform, SysML diagrams and Petri nets. This methodology allows organizing the design process with adequate time and appropriated hardware utilization. These characteristics are suitable for HIL modeling with high complexity level such as applications in micro-grids. Simulation results show consistency with theoretical models. Finally, description of PV system models in terms of Petri nets allows verifying properties for structural and behavioral analysis before implementation in FPGA.

Fig. 14: Experimental result of boost converter model implemented in FPGA.

Fig. 15: Simulation of *Perturb and Observe* method for MPP search in PV model from HiLeS platform.

#### REFERENCES

- M. Tavakkoli, A. Radan, and H. Hassibi, "Design and simulation of electronic infrastructure of a dc smart micro grid," in *Smart Grids* (ICSG), 2012 2nd Iranian Conference on, pp. 1–6, May 2012.

- [2] D. Wilson, J. Neely, M. Cook, S. Glover, J. Young, and R. Robinett, "Hamiltonian control design for dc microgrids with stochastic sources and loads with applications," in *Power Electronics, Electrical Drives, Automation and Motion (SPEEDAM)*, 2014 International Symposium on, pp. 1264–1271, June 2014.

- [3] N. Soultanis and N. Hatziargyriou, "Dynamic simulation of power electronics dominated micro-grids," in *Power Engineering Society General Meeting*, 2006. IEEE, pp. 7 pp.-, 2006.

- [4] K. Fathy, T. Doi, K. Morimoto, H. W. Lee, and M. Nakaoka, "A new high frequency linked soft-switching pwm dc-dc converter with high and low side dc rail active edge resonant snubbers for high performance arc welder," in *Industry Applications Conference*, 2006. 41st IAS Annual Meeting. Conference Record of the 2006 IEEE, vol. 5, pp. 2129–2135, Oct 2006.

- [5] K. Morimoto, T. Doi, H. Manabe, M. Nakaoka, H.-W. Lee, N. Ahmed, E. Hiraki, and T. Ahmed, "Next generation high efficiency high power dc-dc converter incorporating active switch and snubbing capacitor assisted full-bridge soft-switching pwm inverter with high frequency transformer for large current output," in *Applied Power Electronics Conference and Exposition*, 2005. APEC 2005. Twentieth Annual IEEE, vol. 3, pp. 1549–1555 Vol. 3, March 2005.

- [6] I. Leonard, T. Baldwin, and M. Sloderbeck, "Accelerating the customerdriven microgrid through real-time digital simulation," in *Power Energy Society General Meeting*, 2009. PES '09. IEEE, pp. 1–3, July 2009.

- [7] C. Gomez, J.-C. Pascal, J. Jimenez, and P. Esteban, "Heterogeneous systems verification on hiles designer tool," in *IECON 2010 - 36th Annual Conference on IEEE Industrial Electronics Society*, pp. 132– 137, Nov 2010.

- [8] B. Berthomieu and F. Vernadat, "Time petri nets analysis with tina," in Quantitative Evaluation of Systems, 2006. QEST 2006. Third International Conference on, pp. 123–124, Sept 2006.

- [9] A. Gutierrez, H. Chamorro, and J. Jimenez, "Hardware-in-the-loop based sysml for model and control design of interleaved boost converters," in Control and Modeling for Power Electronics (COMPEL), 2014 IEEE 15th Workshop on, pp. 1–6, June 2014.

- [10] O.M.G., "Systems modeling language (omg sysml) specification, in http://sysml.org/docs/specs/omgsysml-v1.3-12-06-02.pdf," June 2012.

- [11] "https://hiles.uniandes.edu.co/."

- [12] E. Koutroulis, K. Kalaitzakis, and V. Tzitzilonis, "Development of an fpga-based system for real-time simulation of photovoltaic modules," in *Rapid System Prototyping*, 2006. Seventeenth IEEE International Workshop on, pp. 200–208, June 2006.

- [13] J.-H. Jung and S. Ahmed, "Model construction of single crystalline photovoltaic panels for real-time simulation," in *Energy Conversion Congress and Exposition (ECCE)*, 2010 IEEE, pp. 342–349, Sept 2010.

- [14] A. Ali, M. Saied, M. Mostafa, and T. Abdel-Moneim, "A survey of maximum ppt techniques of pv systems," in *Energytech*, 2012 IEEE, pp. 1–17, May 2012.

- [15] D. Beriber and A. Talha, "Mppt techniques for pv systems," in *Power Engineering, Energy and Electrical Drives (POWERENG)*, 2013 Fourth International Conference on, pp. 1437–1442, May 2013.