## Physical origin of the gate current surge during short-circuit operation of SiC MOSFET

François Boige, David Trémouilles, Frédéric Richardeau

## ▶ To cite this version:

François Boige, David Trémouilles, Frédéric Richardeau. Physical origin of the gate current surge during short-circuit operation of SiC MOSFET. IEEE Electron Device Letters, 2019, 40 (5), pp.666-669. 10.1109/led.2019.2896939 . hal-02020275

## HAL Id: hal-02020275 https://laas.hal.science/hal-02020275

Submitted on 27 Feb 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés. This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/LED.2019.2896939, IEEE Electron Device Letters

#### ice Letters

# Physical origin of the gate current surge during short-circuit operation of SiC MOSFET

F. Boige, D. Trémouilles, F. Richardeau

*Abstract*— During short-circuit of a vertical 4H-SiC power MOSFET, a high gate current starts to flow through the gate dielectric. We demonstrate that the Schottky emission is the main physical mechanisms.

*Index Terms*— 4H-SiC MOSFET, Short-circuit, gate oxide, Schottky emission, Fowler-Nordheim

#### I. Introduction

High performance electrical-power switches, offering the lowest possible energy losses are required to manage electrical power efficiently. Power devices based on wide bandgap material like Silicon Carbide (SiC) MOSFET are emerging as an effective technology solution to provide such high performance switches. One main obstacle of the SiC MOSFET expansion to industrial application is their reliability and especially their low robustness compared with Silicon devices in short-circuit (SC) operation [1]-[7]. The observed behaviour is different compared to Si devices. Indeed, the SC current density is much higher and after few microseconds in SC operation, a large gate current appears. This current has been studied from a "user point of view" in [2] and some physical explanation have been proposed in [7], [8]. It is generally assumed that the physical origin of this gate current is due to Fowler-Nordheim (F-N) tunnelling. However, in SC condition and especially with a SiC power device, the junction temperature rises rapidly to reach 1200 K to 1800 K [5], [9]. Furthermore, the gate electrical field is at nominal level (≈4 MV/cm) which does not favour F-N conduction which is supposed to be triggered by a high electric field and is hardly a function of the temperature.

In this work, we investigated on the physical conduction mechanism which best corresponds with the experimental behaviour on a vertical power device.

In the first section, the experimental results and the main hypothesis are discussed. In the second section, the F-N model and the thermionic emission model are presented and compared. Finally, these models are discussed regarding experimental observation.

#### II. EXPERIMENTAL RESULTS

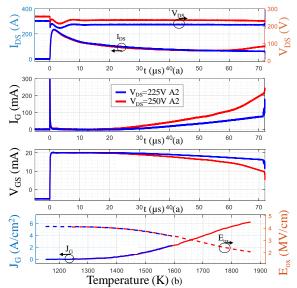

The device under test (DUT) is a 1200 V 80 m $\Omega$  4H-SiC planar power MOSFET. The DUT was tested during SC stress with increasing drain bias until device failure. The experimental setup is described in [10]. The waveforms of the SC tests are presented in Fig. 1a. During the SC, the DUT undergoes a high

Manuscript send 17/12/18. Date of the current version 17/12/18. This research work received financial support from the French National Research Agency (ANR). Project name: HIT-TEMS managed by CNAM Paris and Satie lab. Grant number ANR-15-CE05-0010.

power-density peak leading to a fast rise of its junction temperature. A 1D thermal model has been developed in [9] in order to estimate this temperature. The thermal model is composed of the top aluminium layer and the SiC bulk. The heat dissipated during the short-circuit is located in the depletion layer just under the junction. All the physical parameters are temperature dependent. In the two tests presented in Fig. 1a, all gate currents approximately can rise up to 200 mA and behave similarly versus the estimated temperature (Fig. 1b), demonstrating a strong correlation between the two physical quantities. However, this large gate current does not damage the device in the tests. Indeed, if few SC of few microseconds are performed, the gate current dynamic will remain the same and no measurable degradation can be observed [2]. Based on these observations, the gate current must be a conduction mechanism through the gate oxide.

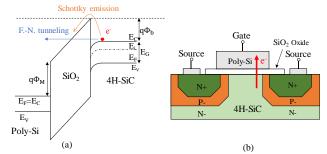

According to Chiu *et al* [11], if an insulator has a low trap density like for the SiO<sub>2</sub> considered in this work, two main conduction mechanisms coexist in thick dielectric films: Schottky emission and F-N tunnelling. These mechanisms are illustrated in Fig.2a and 2b. When the gate bias is large enough, the electron sees a triangular barrier formed by the dielectric. In that case, the electron has a probability to cross the barrier and

Fig. 1 (a)Waveforms of a SiC 1200V 80 m $\Omega$  MOSFET SiC in short-circuit operation for two V<sub>DS</sub>. (R<sub>G</sub>=47  $\Omega$ , V<sub>gs</sub>=20 V). (b) Gate current vs Temperature at R<sub>G</sub>=47  $\Omega$ , V<sub>buffer</sub>=20 V e<sub>ox</sub>=50 nm S<sub>ox</sub>=3.32 mm<sup>2</sup>

F. Boige and F. Richardeau are with the LAPLACE laboratory, University of Toulouse, CNRS, INPT, UPS, France. (e-mail: boige@laplace.univ-tlse.fr).

D. Tremouilles is with LAAS-CNRS, University of Toulouse, CNRS, Toulouse, France.

Fig. 2 Schematic band diagram for Vgs > 0 V of the Metal Oxide Semiconductor (MOS) structure consisting of a highly doped n poly-Si, silicon dioxide and 4H-SiC. (a) The F.-N. tunneling and the Schottky emission are illustrated at high bias (b) Cross section of a VDMOS, in red the electrons flow direction.

the resulting current is called F.-N. tunnelling. On the other hand, when the electron has enough thermal energy to exceed the barrier at the interface and then to cross the dielectric barrier, the resulting current follows the Schottky-emission model (also referred to as thermionic emission). Considering the vertical SiC power MOSFET's gate oxide thickness (typically  $\approx$ 50 nm)[12] and the operating conditions in SC test: the nominal electric field (E≤4 MV/cm) and the strong temperature rise, the models that could fit the physical mechanism are temperature dependent F-N tunnelling [13] and the Schottky-emission model.

## III. EXPLORATIONS OF THE CONDUCTION MODELS ACROSS A DIELECTRIC

### A. Fowler Nordheim temperature dependent model

The expression of the F-N tunnelling current [11] is:

$$J_{FN} = \frac{q^3}{8\pi h \Phi_B} \cdot E^2 \cdot exp \left[ -\frac{8\pi \sqrt{2m_{ox} \Phi_B^3}}{3qhE} \right]$$

(1)

where q is the elementary charge, h the Plank's constant,  $\phi_B$  the semiconductor-oxide barrier height,  $m_{ox} = 0.42 \cdot m_0$  the effective mass of electron in the oxide [14],  $m_0$  the free electron mass and E the electrical field magnitude.

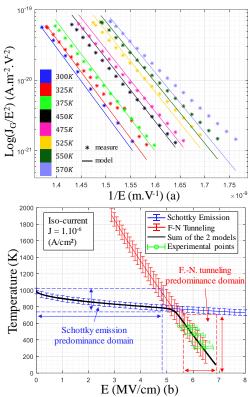

F-N current expression (1) is not an explicit function of the temperature. However, physical parameters such as, the semiconductor-oxide barrier height  $\Phi_B$  can be modeled as temperature dependent in order to model the heating of the 4H-SiC [13]. In order to know how  $\Phi_B$  depends on the temperature, we measured the gate current as a function of the gate bias at different stabilized temperature (300 K to 575 K) with drain and source shorted to ground. The measures are performed on a thermally regulated chunk under probes connected to a source measure unit. The measures are pulsed and the current is limited at 100nA, as displayed Fig. 3a. Equation (1) has been used to fit the measured current.  $\Phi_B$  has been chosen as a linear function of the temperature ( $\Phi_B = \Phi_{B0} + d \Phi_B / dT \cdot T$ ) as justified in [15].  $\Phi_B$  value at 300 K has been constrained in a range complying with literature values [16]. The electrical field is deducted from the gate voltage through this relation E = $V_G/e_{ox}$  where  $e_{ox}$  is the gate oxide thickness. Although for a

Fig. 3 (a) Fitting of the F-N model function of the temperature. (b) Isocurrent density of the fitted models FN tunnelling and Schottky emission in the plan temperature vs electrical field and the measured points under probe at fixed temperature. F-N model function of the temperature for  $e_{ox} = 48.5 \text{ nm}, \Phi_B(V) = -7.116 \cdot 10^{-4} \cdot T + 2.914$

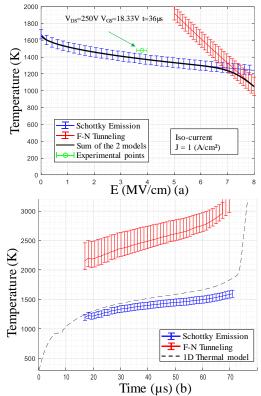

Fig. 4 (a)iso-current density of the models FN tunnelling and Schottky emission in the plan temperature vs electrical field and the measured points in short-circuit. (b) Estimated temperature with the Schottky model, the FN tunnelling and the 1D thermal model.

F. Boige et al.

SiC power MOSFET, the gate oxide is known to be about 50nm thick, the value is not precisely known so it is one of the fitted parameters. The gate oxide surface has been estimated using measures of the length of a cell available in [17]. The fitting has three been performed with fitting parameters  $(\Phi_{B0}, d\Phi_B/dT, e_{ox})$  with fixed boundaries and solved with CMA-ES algorithm [18]. The fitted parameter values are summarised in table I and the model obtained is compared with experimental results in Fig. 3a. Fitted model is extrapolated and represented as a temperature vs electrical field graph for a selected current density in Fig. 3b. As expected, the FN model matched very well the measurement results.

| PARAMETERS FITTED                       |                                                                             |

|-----------------------------------------|-----------------------------------------------------------------------------|

| Parameter                               | Min/Mean/Max                                                                |

| $\Phi_B$ at 300K(eV)                    | 2.6/2.7/2.8 [16] min/max imposed                                            |

| $\frac{d\Phi_B}{dT}(eV/K)$ $e_{ox}(nm)$ | $-7.379 \cdot 10^{-4} / -7.116 \cdot 10^{-4} / -6.876 \cdot 10^{-4}$ fitted |

|                                         | 46/48.5/51 fitted                                                           |

## B. Thermionic emission (Schottky emission)

The expression of the Schottky emission model [11]:

$$J_{SE} = \frac{4\pi q k^2 m_{ox}}{h^3} \cdot T^2 \cdot \exp\left[\frac{-\phi_B + \sqrt{q^3 E/(4\pi\epsilon_F\epsilon_0)}}{kT}\right]$$

(2)

where k is Boltzmann's constant,  $\epsilon_0$  the permittivity of vacuum,  $\epsilon_r = n^2 = 1.45^2$  [19] is the SiO<sub>2</sub> dynamic electrical constant which is close to the square of the optical refraction indices [11]. In this model, the mathematical expression (2) is explicitly dependent of the temperature so  $\Phi_B$  is not temperature dependent. The model is extrapolated and displayed in a temperature vs electrical field graph for a given current density in Fig. 3b. The dark line represents an iso gate-current density regardless of the physical mechanism causing it. It is clear that between 5.7 and 6.9 MV/cm, the current produced by the FN tunnelling is prevailing and the Schottky-emission current is negligible.

## C. Comparison of SC measurement results with the Emission and the FN model

The aim of the study is finding the most appropriate model to explain the origin of the large experimental gate-current observed during short-circuit operation. The current, Fig 1b, is a strong function of the temperature and the electrical field such as the Schottky emission model and the FN tunnelling model, respectively. The temperature of the experimental points in SC test are estimated with a 1D-thermal model. Experimental points are placed in the temperature vs electrical field graph in Fig. 4a together with FN and Schottky models at a given current density. For the electrical field and temperature of the SC test, the experimental point is very close to the Schottky model. The electrical field or temperature should have been much higher for the FN model to match with the experimental results. As a conclusion, the Schottky emission phenomena is clearly the most appropriate to model and explain the experimental results.

## *D.* Confrontation of the Schottky model and the thermal model

1

In order to confirm the results of the previous section, the oxide temperature has been estimated using the Schottky emission and the FN tunnelling models and the results compared with the 1D thermal model. Two different electrical measurements are used in order to estimate the temperature. In the first case, the temperature is estimated using the gate voltage and the gate current as inputs and in the second case, the temperature is estimated using the drain current and bias as inputs. The estimated temperatures are displayed in Fig. 4b, for the Schottky model and the FN tunnelling model, respectively. The temperatures estimated with the Schottky emission model are 10% to 20% lower than the 1D thermal model. However, the temperatures estimated with the FN tunnelling model are 35% to 50% higher than the 1D thermal model. In conclusion, the temperatures estimated with the Schottky and the 1D thermal model are very similar despite totally different electrical input and models are used. The residual difference between the two estimated temperatures could be attributed to 1D thermal model being known to always overestimate temperature.

#### IV. CONCLUSION

The Schottky emission is most likely to be the mechanism explaining the large gate current observed in SiC MOSFET during short circuit operation. It is important to note that Schottky emission mechanisms would also coexist in silicon MOSFETs, however it is not observed as the temperature required for such Schottky current cannot be reached as it is above the thermal runaway temperature of silicon. Moreover, the barrier height  $\Phi_B$  is higher for Si/SiO<sub>2</sub> than SiC/SiO<sub>2</sub> one. Generally speaking, we could expect to observe Schottky emission current across oxide in other wide bandgap materials too such as: GaN and diamond, that can also bear extreme temperature. Finally and as a perspective, the gate current measurement could provide an image of the oxide temperature using the Schottky model, even if detecting this current is already an indicator that the component is already extremely hot (1160 K-1300 K).

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/LED.2019.2896939, IEEE Electron Device Letters

F. Boige et al.

### REFERENCE

- [1] Z. Wang, X. Shi, Y. Xue, L. M. Tolbert, B. J. Blalock, et F. Wang, « Design and performance evaluation of overcurrent protection schemes for silicon carbide (SiC) power MOSFETs », in 2013 IEEE Energy Conversion Congress and Exposition, 2013, p. 5418-5425 https://doi.org/10.1109/ECCE.2013.6647436.

- [2] F. Boige et F. Richardeau, « Gate leakage-current analysis and modelling of planar and trench power SiC MOSFET devices in extreme short-circuit operation », *Microelectron. Reliab.*, vol. 76-77, nº Supplement C, p. 532-538, sept. 2017 https://doi.org/10.1016/j.microrel.2017.06.084.

- [3] R. Ouaida, M. Berthou, J. León, X. Perpiñà, S. Oge, P. Brosselard, et C. Joubert, « Gate Oxide Degradation of SiC MOSFET in Switching Conditions », *IEEE Electron Device Lett.*, vol. 35, nº 12, p. 1284-1286, déc. 2014 https://doi.org/10.1109/LED.2014.2361674.

- C. Chen, D. Labrousse, S. Lefebvre, M. Petit, C. Buttay, et H. Morel, « Study of short-circuit robustness of SiC MOSFETs, analysis of the failure modes and comparison with BJTs », *Microelectron. Reliab.*, vol. 55, n° 9, p. 1708-1713, août 2015 https://doi.org/10.1016/j.microrel.2015.06.097.

- [5] Z. Wang, X. Shi, L. M. Tolbert, F. Wang, Z. Liang, D. Costinett, et B. J. Blalock, « Temperature-Dependent Short-Circuit Capability of Silicon Carbide Power MOSFETs », *IEEE Trans. Power Electron.*, vol. 31, n° 2, p. 1555-1566, févr. 2016 https://doi.org/10.1109/TPEL.2015.2416358.

- [6] G. Romano, A. Fayyaz, M. Riccio, L. Maresca, G. Breglio, A. Castellazzi, et A. Irace, « A Comprehensive Study of Short-Circuit Ruggedness of Silicon Carbide Power MOSFETs », *IEEE J. Emerg. Sel. Top. Power Electron.*, vol. 4, n° 3, p. 978-987, sept. 2016 https://doi.org/10.1109/JESTPE.2016.2563220.

- [7] S. Mbarek, F. Fouquet, P. Dherbecourt, M. Masmoudi, et O. Latry, « Gate oxide degradation of SiC MOSFET under short-circuit aging tests », *Microelectron. Reliab.*, vol. 64, n° Supplement C, p. 415-418, sept. 2016 https://doi.org/10.1016/j.microrel.2016.07.132.

- [8] T. T. Nguyen, A. Ahmed, T. V. Thang, et J. H. Park, « Gate Oxide Reliability Issues of SiC MOSFETs Under Short-Circuit Operation », *IEEE Trans. Power Electron.*, vol. 30, n° 5, p. 2445-2455, mai 2015 https://doi.org/10.1109/TPEL.2014.2353417.

- [9] F. Boige, F. Richardeau, S. Lefebvre, et M. Cousineau, « SiC power MOSFET in short-circuit operation: Electro-thermal macro-modelling combining physical and numerical approaches with circuit-type implementation », *Math. Comput. Simul.*, sept. 2018 https://doi.org/10.1016/j.matcom.2018.09.020.

- F. Boige, F. Richardeau, S. Lefebvre, J.-M. Blaquière, G. Guibaud, et A. Bourennane, « Ensure an original and safe "fail-to-open" mode in planar and trench power SiC MOSFET devices in extreme short-circuit operation », *Microelectron. Reliab.*, vol. 88-90, p. 598-603, sept. 2018 https://doi.org/10.1016/j.microrel.2018.07.026.

[11] F.-C. Chiu, « A Review on Conduction Mechanisms in Dielectric Films », Advances in Materials Science and Engineering, 2014. [En ligne]. Disponible sur: https://www.hindawi.com/journals/amse/2014/578168/.

[Consulté le: 20-déc-2017] https://doi.org/10.1155/2014/578168.

1

M. Nawaz, « On the Evaluation of Gate Dielectrics for 4H-SiC Based Power MOSFETs », Active and Passive Electronic Components, 2015. [En ligne]. Disponible sur: https://www.hindawi.com/journals/apec/2015/651527/. [Consulté le: 14-mai-2018]

https://doi.org/10.1155/2015/651527.

- [13] G. Pananakakis, G. Ghibaudo, R. Kies, et C. Papadas, « Temperature dependence of the Fowler–Nordheim current in metal-oxide-degenerate semiconductor structures », J. Appl. Phys., vol. 78, n° 4, p. 2635, juin 1998 https://doi.org/10.1063/1.360124.

- [14] M. Lenzlinger et E. H. Snow, «Fowler-Nordheim Tunneling into Thermally Grown SiO2 », J. Appl. Phys., vol. 40, n° 1, p. 278-283, janv. 1969 https://doi.org/10.1063/1.1657043.

- [15] D. Schroeder et A. Avellán, « Physical explanation of the barrier height temperature dependence in metal-oxidesemiconductor leakage current models », *Appl. Phys. Lett.*, vol. 82, n° 25, p. 4510-4512, juin 2003 https://doi.org/10.1063/1.1587256.

- [16] V. V. Afanas'ev, M. Bassler, G. Pensl, M. J. Schulz, et E. Stein von Kamienski, « Band offsets and electronic structure of SiC/SiO2 interfaces », *J. Appl. Phys.*, vol. 79, n° 6, p. 3108-3114, mars 1996 https://doi.org/10.1063/1.361254.

- [17] F. Boige, F. Richardeau, D. Trémouilles, S. Lefebvre, et G. Guibaud, « Investigation on damaged planar-oxide of 1200V SiC power MOSFETs in non-destructive shortcircuit operation », *Microelectron. Reliab.*, vol. 76-77, n° Supplement C, p. 500-506, sept. 2017 https://doi.org/10.1016/j.microrel.2017.06.085.

- [18] N. Hansen, « A CMA-ES for Mixed-Integer Nonlinear Optimization », INRIA, report, oct. 2011.

- [19] «RefractiveIndex.INFO Refractive index database ».

[En ligne]. Disponible sur: https://refractiveindex.info/.

[Consulté le: 26-oct-2018].