## Large-Scale Monolithic Fabrication of III–V Vertical Nanowires on a Standard Si(100) Microelectronic Substrate

Aurélie Lecestre, Mickael Martin, Fuccio Cristiano, Thierry Baron, Guilhem Larrieu

#### ▶ To cite this version:

Aurélie Lecestre, Mickael Martin, Fuccio Cristiano, Thierry Baron, Guilhem Larrieu. Large-Scale Monolithic Fabrication of III–V Vertical Nanowires on a Standard Si(100) Microelectronic Substrate. ACS Omega, 2022, 7, pp.5836 - 5843. 10.1021/acsomega.1c05876. hal-03600996

### HAL Id: hal-03600996 https://laas.hal.science/hal-03600996

Submitted on 8 Mar 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

http://pubs.acs.org/journal/acsodf Article

# Large-Scale Monolithic Fabrication of III—V Vertical Nanowires on a Standard Si(100) Microelectronic Substrate

Aurélie Lecestre, Mickael Martin, Filadelfo Cristiano, Thierry Baron, and Guilhem Larrieu\*

Cite This: ACS Omega 2022, 7, 5836-5843

ACCESS I

Metrics & More

Article Recommendations

Supporting Information

ABSTRACT: Vertical III—V nanowires are of great interest for a large number of applications, but their integration still suffers from manufacturing difficulties of these one-dimensional nanostructures on the standard Si(100) microelectronic platform at a large scale. Here, a top-down approach based on the structure of a thin III—V epitaxial layer on Si was proposed to obtain monolithic GaAs or GaSb nanowires as well as GaAs—Si nanowires with an axial heterostructure. Based on a few complementary metal—oxide—semiconductor-compatible fabrication steps, III—V nanowires with a high crystalline quality as well as a uniform diameter (30 nm), morphology, positioning, and orientation were fabricated. In

addition, the patterning control of nanowires at the nanoscale was thoroughly characterized by structural and chemical analyses to finely tune the key process parameters. To properly control the morphology of the nanowires during reactive-ion etching (RIE), the balance between the plasma properties and the formation of a protective layer on the nanowire sidewall was studied in detail. Furthermore, high-resolution microscopy analyses were performed to gain a better understanding of the protective layer's composition and to observe the crystalline quality of the nanowires. This approach paves the way for the possible scale-up integration of III—V-based nanowire devices with conventional Si/complementary metal—oxide—semiconductor technology.

#### INTRODUCTION

In the semiconductor world, III-V materials are complementary to silicon (Si). Their exceptional electronic mobilities and direct band gap properties make them attractive in a large spectrum of applications like nanoelectronics, 1,2 nanophotonics, <sup>3,4</sup> biological sensing, <sup>5</sup> photovoltaics, <sup>6,7</sup> and optoelectronics. <sup>8-10</sup> All of these applications greatly benefit from integration with a III-V-nanostructured layer, in particular vertical nanowires. <sup>11,12</sup> Their one-dimensional geometry (large surface-to-volume ratio) and their ability to create heterostructures (axial and radial) offer advantages in terms of their integration and compatibility with conventional microfabrication facilities. However, Si has been and will continue to be the most appropriate platform for the mass production of electronic devices due to its abundance, robustness, and high-quality oxide (SiO<sub>2</sub>) as well as the accumulated knowledge around this material and related technologies over the past 50 years. In this study, the cointegration of III-V devices with Si-complementary metal-oxide-semiconductor electronics is proposed to advance the design of new systems that combine the advantages of III-V and Si.

However, the integration of a III–V nanostructure on a Si(100) substrate, the industry-standard Si platform, represents an important challenge to obtain III–V nanowires with a low crystal defect density that are localized and oriented with high precision. For monolithic integration, direct epitaxy of III–V materials on Si(100) is required. One of the key difficulties to

epitaxial approaches is to overcome material defects stemming from the crystal lattice mismatch with Si. 13 Moreover, the localization and orientation of III-V nanowires on Si are essential for device integration. The most popular methods to obtain localized III-V nanowires on Si are based on a bottomup approach, with selective area epitaxy, where the III-V nanostructures are grown selectively on a Si substrate, in most cases using a catalyst 14-16 (e.g., the vapor-liquid-solid method). The first demonstration used networks of metallic catalysts patterned by a liftoff process before nanowire growth.7,13 Later, self-catalyzed approaches were proposed (e.g., Ga droplets are self-localized in a hole matrix structured in a SiO<sub>2</sub> layer). 17,18 The main advantages of bottom-up growth approaches are the crystalline bulk quality and the favorable surface properties of nanowires. Nevertheless, it is still challenging to fabricate nanowires with high reproducibility on all wafer-scale in terms of diameter, morphology, positioning, crystal structure, and dopant concentration. Moreover, nanowires grown in the vertical direction with a

Received: October 20, 2021 Accepted: January 19, 2022 Published: February 8, 2022

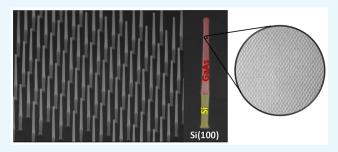

Figure 1. Top-down nano-patterning of vertical GaAs nanowires on a Si(100) substrate (schematic representation and the associated SEM images in a tilted view): (a) nanopatterning of a negative mask by e-beam lithography (HSQ nanopatterns). (b) GaAs plasma etching using  $Cl_2$ -based chemistry by tuning the anisotropic etching and the protective layer formation. (c) Stripping of the remaining layers (HSQ resist and sidewall protective layer) by chemical etching.

high yield only have been demonstrated on a Si(111) substrate. Interestingly, the control of the growth direction independently of the substrate orientation has been obtained, thanks to a growth template. This method has provided perfectly vertical III—V nanowires on a Si(100) substrate with a low defect density but at the cost of an increase in the process complexity. Additionally, ultimate scaling of the nanowire diameter/pitch is difficult to obtain. Furthermore, the faceting on the top of the nanowire and enlargement of the foot of the structures<sup>20</sup> are issues for device integration, in particular the low resistive contact formation. Finally, very few studies have focused on the patterning of III—V vertical nanowires by a top-down approach with scaled dimensions<sup>21–23</sup> and these have not considered monolithic integration with Si.

Here, we present a wafer-scale approach to fabricate a III–V vertical nanowire array with a low defect density as well as tight control of the location and the diameter on a standard Si(100) microelectronic substrate. This approach is demonstrated on different materials (GaAs and GaSb) and architectures (array of nanowires and array of axial heterostructures). The patterning control of nanowires at the nanoscale was thoroughly studied by structural and chemical analyses by scanning electron microscopy (SEM) and transmission electron microscopy (TEM) coupled to energy-dispersive X-ray spectroscopy (EDX) to understand and tune the key parameters (plasma properties, protective layers, and crystal-line properties).

## ■ LARGE-SCALE PATTERNING OF A VERTICAL NANOWIRE ARRAY

Our approach is presented in Figure 1, where each step is illustrated with a schematic diagram with the associated SEM images. The vertical III–V nanowires were fabricated using only four standard techniques of micro-/nanofabrication: planar epitaxy of the III–V layer on a Si(100) substrate, nanolithography, plasma etching, and selective chemical stripping.

The starting III—V layer (GaAs and GaSb) was grown by metalorganic chemical vapor deposition on a 300 mm Si(100) substrate with a layer free of antiphase boundaries. Specific Si surface engineering based on annealing creates atomic steps on the Si surface that prevent antiphase boundary formation. The crystalline quality of the epitaxial layer is of prime importance because these crystalline defects degrade the carrier mobility.<sup>24</sup>

Details of the process can be found in references 25, 26. Thicknesses of the III-V layer ranging from 200 to 800 nm were used. First, nanopatterns (Figure 1a) were made by electron beam lithography using a 90 nm negative-tone resist layer, namely, hydrogen silsesquioxane (HSQ), which is a flowable oxide from Dow Corning<sup>27</sup> diluted in methyl isobutyl ketone. To overcome the adhesion issues of small HSQ patterns on a III-V surface, the following surface cleaning protocol was performed prior to HSQ coating: (i) oxygen (O<sub>2</sub>) plasma to remove organic residues, (ii) a deoxidation step with 37% HCl mixed with deionized water (DIW) (1:1) for 1 min, (iii) rinsing step with DIW, and (iv) dehydration step on a hot plate at 110 °C for 5 min. The electron beam exposure was carried out with a Raith 150 system at low energy (20 keV) with a base dose of 350 pC/cm a step of 2 nm, and a current of 120 pA. The circular shape was designed using a starlike pattern, composed of lines starting and finishing in the center of the pattern to force the symmetry of the nanopillars and homogeneous distribution of the Gaussian energy.<sup>27</sup> After exposure, the resist was developed by manual immersion in 25% tetramethylammonium hydroxide solution in water to enhance the pattern contrast.<sup>27</sup> A tilted SEM image of an array of HSQ patterns with a diameter of 30 nm, a height of 90 nm, and a pitch of 300 nm is shown in Figure 1a. The following step, illustrated in Figure 1b, is the transfer of nanomasks into the GaAs layer by anisotropic plasma etching. This dry etching is one of the most important modules of the top-down process to reach high aspect ratio and nanometer-scale nanowires with vertical and smooth sidewalls. The key point is the tight engineering of anisotropic etching (the balance between chemical etching and ion bombardment) and protective layer formation on the nanowire sidewall, as depicted in Figure 1b. GaAs nanowires with a vertical sidewall could be achieved with plasma-based-chlorine (Cl<sub>2</sub>) chemistry (Figure 1b) down to the Si/GaAs interface. The detection of the etching endpoint was controlled with a laser interferometer to avoid large overetching, which would erode the nanowire base and degrade the mechanical stability of the nanostructures. Finally, the last step was the stripping of the remaining layers (HSQ) resist and sidewall protective layer) by chemical etching with 5% hydrofluoric acid (HF) (Figure 1c).

#### ■ RESULTS AND DISCUSSION

**Verticality Control.** The diameter and orientation of nanowires are fundamental for device integration. For example,

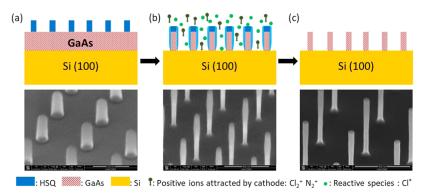

Figure 2. Impact of the plasma parameters on the nanowire sidewall anisotropy and on the GaAs etch rate as well as the related SEM images of the specific conditions (scale bar = 100 nm): (a) Impact of the  $Cl_2/N_2$  gas ratio at Picp = 200 W; Pbias = 60 W; P = 6 mT; and T = 35 °C on nanowire arrays of 60 nm diameter, 600 nm height, and 300 nm space. (b) Impact of the ICP power influence at  $Cl_2/N_2$  = 8; Pbias = 60 W; P = 6 mT; and T = 35 °C on nanowire arrays of 40 nm diameter, 600 nm height, and 300 nm space.

gate-all-around transistors 21,22 use nanowires as the conducting channel, and the surface properties or diameter variation can significantly impact the electrical characteristics. Inductively coupled plasma (ICP) reactive-ion etching is the most appropriate system to obtain high-aspect-ratio nanowires with a very low roughness because it allows the gas to be ionized independently of ionic bombardment. Several plasma chemistries can be used to etch GaAs. Generally, chlorine gases are the most suitable to form  $GaCl_x$  and  $AsCl_x$  volatile products like  $BCl_3^{\ 31-33}$   $SiCl_4^{\ 34}$  and  $Cl_2^{\ 29,30,35-38}$  The current study focused on  $Cl_2/nitrogen$   $(N_2)$  chemistry using only chlorine gas,<sup>28</sup> Cl<sub>2</sub>, which is less corrosive and dangerous than BCl<sub>3</sub> or SiCl<sub>4</sub>. As shown in Figure 2, control of the nanostructure geometry by plasma etching was studied by evaluating two key parameters: the gas chemistry (Cl<sub>2</sub>/N<sub>2</sub> ratio) and the coil power. Because all of the process parameters are interdependent, the objective was to determine the optimal parameters to obtain a good balance between physical etching (sputtering-related mechanism, mainly anisotropic) and chemical etching (surface reaction-related mechanism, mainly isotropic).

First, to have a better overview of the chemical versus physical etching contribution, we considered the gas chemistry of  $Cl_2$  and  $N_2$  involved in the plasma.  $Cl_2$  is a reactive gas promoting the chemical etching of GaAs to form the following

volatile species: GaCl<sub>x</sub> and AsCl<sub>x</sub>. N<sub>2</sub> is a neutral gas promoting physical etching by ion bombardment. The SEM images in the tilted view (Figure 2a) show the GaAs etch rate and the angle between the nanostructure sidewall with a Si (100) bulk surface as a function of the Cl<sub>2</sub>/N<sub>2</sub> gas ratio in the ICP with specific conditions (200 W), highlighting the resulting nanowire shape. The N2 flow rate was fixed at 10 sccm, while the Cl<sub>2</sub> flow rate was varied from 10 to 80 sccm. The other process parameters were set constant: radio frequency power, 60 W; ICP power, 200 W; chamber pressure, 6 mTorr; and sample holder temperature, 35 °C. Optical emission spectrometry measurements, presented in Supporting Information Figure S1, show the Cl<sup>2+</sup> quantities in the plasma. As expected, when the Cl<sub>2</sub>/N<sub>2</sub> gas ratio was decreased, the reactive species quantity was reduced, and the plasma was highly physical. As the GaAs etch rate decreased, the etching selectivity between the HSQ mask and GaAs was very poor, leading to fast etching of the mask and preventing fabrication of high-aspect-ratio vertical nanowires (Figure 2a, left). Increasing the Cl<sub>2</sub> flow rate also increased the quantities of the reactive species as well as species renewal in the reactor. Thus, increasing the Cl<sub>2</sub> flow rate favored the chemical reaction over physical etching (ionic bombardment). As a consequence, the GaAs etch rate increased together with a

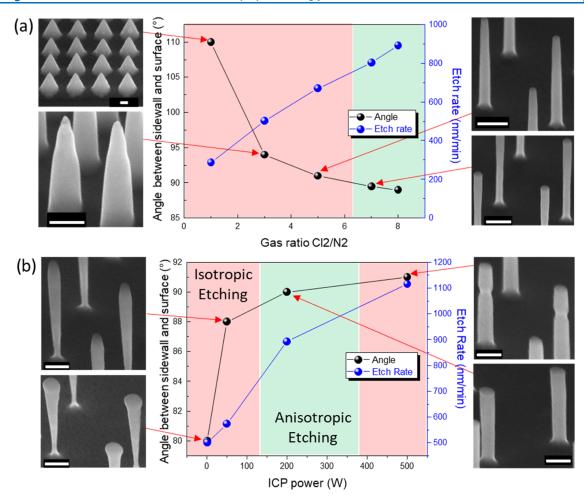

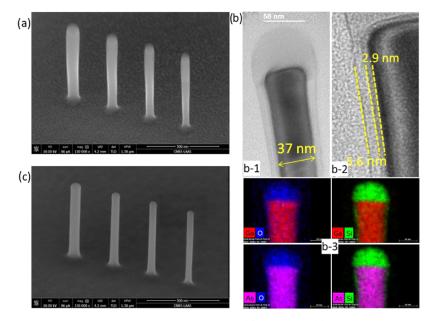

Figure 3. Characterization of the protective layer: SEM images in a tilted view (a) before and (c) after HF cleaning of GaAs vertical nanowires. (b) EDX-TEM ex situ analysis of the amorphous protective layer generated during the plasma etching step, which covers the GaAs vertical nanowires.

better HSQ selectivity, providing a very good improvement of the sidewall verticality (Figure 2a, right).

Next, to investigate the impact of the ICP coil power, the other process parameters were set constant: radio frequency power, 60 W; chamber pressure, 6 mTorr;  $\text{Cl}_2/\text{N}_2$  gas ratio, 8; and holder temperature, 35 °C. Figure 2b shows the influence of the coil power on the GaAs etch rate and the verticality of the nanowire sidewalls, again with some specific conditions observed by SEM images in the tilted view. The ICP coil power controls the dissociation of the plasma in the reactive species and ions as well as the directionality of these particles. The increase of ICP power, from 0 to 500 W, increased the etch rate from 0.5 to 1.1  $\mu\text{m}/\text{min}$ , thanks to a higher reactive species density that also had an impact on the sidewall verticality of the nanostructures.

When the ICP power remained low, the dissociation energy in the plasma was weak, generating a low quantity of Cl<sub>2</sub><sup>+</sup> and N2+ ions, as confirmed by optical emission spectrometry measurements at 1 and 50 W (see Supporting Information Figure S1). Moreover, N2 has a bond-dissociation energy (BDE = 9.79 eV) much lower than that of  $Cl_2$  (BDE = 2.51 eV). Therefore, the chemical reaction between Cl<sub>2</sub> and GaAs was favored over ionic bombardment. As chemical etching is mostly isotropic, the sidewall profile of the nanostructures has a "re-entering" shape, forming an angle with the Si(100) bulk surface lower than 90°. It was necessary to apply a sufficient power level to obtain a good balance between chemical and physical etching to tend toward a vertical profile (etching angle =  $90^{\circ}$ ), which was reached with an ICP power of 200 W. If the ICP power was too high, the ion density would be very large, and the mean free path of ions would become very short, leading to more ion collision and ion deviation in the vertical direction. This configuration was more sensitive to a charge effect due to the HSQ dielectric mask, which could locally enhance the ion deviation. As shown in the SEM image in Figure 2b, a narrow part of the nanowire was overetched in the vicinity of the HSQ mask with an ICP power of 500 W. Finally, the optimal conditions to feature vertical GaAs nanowires were

as follows:  $P_{\rm ICP}$  = 200 W;  $P_{\rm bias}$  = 60 W;  $Cl_2/N_2$  = 8; P = 6 mT; and T = 35 °C.

**Protective Layer.** Figure 3a presents the SEM image in a tilted view after the plasma etching step using these optimized conditions. It shows that the top part is thicker than the bottom. In fact, it is expected that a covering layer forms during the chemical reaction and/or the redeposition of volatile compounds produced during the etching. The top part of the nanowire was thicker than the bottom part due to a cumulative effect during the etching.

Similar passivation has been observed previously on nanowire sidewalls during the etching of other III-V materials  $^{29,30}$  using  $Cl_2/N_2$  ICP reactive-ion etching. We, therefore, analyzed the NWs just after RIE by TEM. Figure 3b-1 presents ex situ EDX-TEM analysis of the nanowires performed on a TEM lamella lifted out using a focused ion beam (FIB) from the original substrate. This analysis confirms that an amorphous layer is present on the top and around the crystalline NWs. A high magnification image (Figure 3b-2) indicates that the amorphous layer formed on the nanowire sidewalls had a maximum thickness of approximately 9 nm on the top of the nanowire. This layer was composed of two sublayers: an inner layer (around 3 nm) and an outer layer (6 nm). The EDX maps, presented in Figure 3b-3, show that the outer amorphous layer was mainly composed of Si and O. Lateral concentration profiles extracted from the maps (not shown) clearly indicate that the Si/O layer is about 10 nm wide, in agreement with the TEM observation. In addition, the Ga profiles extend into the Si/O layer by around 2 nm more than the As one. Overall, these analyses show that the inner layer, around 3 nm thick, was a native oxide, probably Ga<sub>2</sub>O<sub>3</sub> because Ga is preferentially oxidized over As. This inner layer extended under the HSQ mask. Interestingly, the outer layer, around 5.5 nm, did not contain any N element, indicating that a nonvolatile GaN or AsN complex was not formed on the sidewalls. These elements could be provided by the HSQ mask or from the Si carrier where the GaAs sample was stuck. Thanks to the good selectivity between SiO<sub>2</sub> and GaAs (1:6) with our optimized  $Cl_2/N_2$  process conditions, the  $SiO_x$

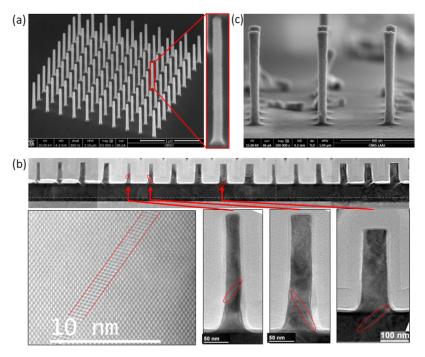

Figure 4. Nanowires with a high aspect ratio and structural characterization. (a) GaAs nanowire array on Si(100) with an aspect ratio up to 15 (diameter = 35 nm, height = 540 nm, pitch = 200 nm). (b) TEM observation of a FIB cross section on several GaAs nanowires showing the probability of defects with a nanowire. (c) GaSb nanowires (diameter = 50 nm, height = 660 nm, pitch = 400 nm) on a Si(100) wafer obtained following the same top-down strategy shown with patterned GaAs nanowires.

protective layer played an important role in obtaining the vertical sidewall by preventing isotropic chemical etching on the top part of the nanostructures.

Finally, Figure 3c shows the NWs after the wet chemical etch (1 min in 5% HF). The HF solution removes the covering layer. This SEM image (Figure 3c) shows perfectly homogeneous NWs. Therefore, the oxide layer was removed during HSQ mask stripping by HF.

Crystalline Defects and a Versatile Approach. Figure 4a shows the SEM image in a tilted view of an array of 100 GaAs nanowires with a pitch of 200 nm on Si(100) obtained using the optimized parameters presented below. The zoomed image of a nanowire highlights the very good diameter homogeneity (~35 nm) along its entire length (540 nm) and a high aspect ratio of 15. This demonstration of GaAs nanowires on a Si (100) substrate meets, for the first time, the requirements for nanowire device fabrication in terms of the control of localization, verticality, diameter, aspect ratio, and density. In addition, the roughness of the sidewall was very low, with an atomically flat interface demonstrated by highangle annular dark-field scanning transmission electron microscopy analysis (not shown). Figure 4b presents the TEM cross-sectional analysis of 16 GaAs nanowires with different diameters. More than 80% of the nanowires exhibited defect-free crystalline structures. Crystalline defects could be observed on three nanowires. These defects were disoriented crystalline plans called "twinned planes" and were very localized in a defined region of the nanostructures without extension in the entire height. The impact of these defects on the electrical characteristics remains low compared to antiphase boundary defects. Indeed, the mobility and the resistivity have been measured on similar GaAs/Si substrates grown by metalorganic chemical vapor deposition with and without an antiphase boundary.<sup>23</sup> With antiphase boundary

defects, the mobility was 10 times lower and the resistivity was 5 times higher compared to the GaAs layer used in the current study. In addition, the roughness of the sidewall was very low, with an atomically flat interface demonstrated by high-angle annular dark-field scanning transmission electron microscopy analysis.

Low-crystalline-defect epitaxial layer growth by metalorganic chemical vapor deposition on Si(100) can be extended to other materials. <sup>25,39,40</sup> In this study, the top-down structure approach, based on  $Cl_2/N_2$  plasma etching, was applied with the optimized conditions on a GaSb layer. Figure 4c shows vertical GaSb nanowires on a Si(100) substrate with a length of 660 nm and a diameter of 50 nm, demonstrating the versatility of the approach and envisioning a possible cointegration of GaAs and GaSb vertical nanowires on the same standard Si(100) microelectronic substrate.

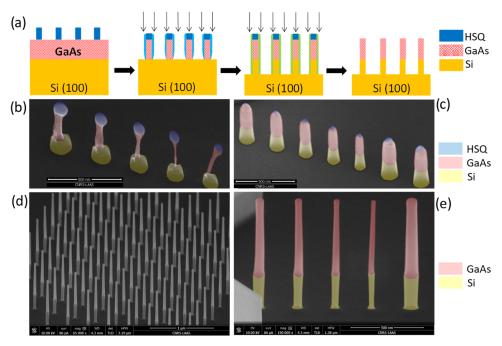

**Axial Heterostructure GaAs/Si Nanowires.** To add to the complexity of this work, we investigated the possibility of creating a GaAs/Si nanowire heterostructure based on the proposed top-down approach (Figure 5). The synthesis of heterostructured nanowires (axial<sup>2</sup> and core—shell<sup>4</sup>) is well known using the bottom-up approach<sup>41,42</sup> but it is much more difficult to address by the top-down approach.

Figure 5a schematically presents the process steps to fabricate axial heterostructured nanowires. First, the GaAs nanowires were patterned by etching the GaAs layer down to the Si/GaAs interface. After this step, 50 nm of the HSQ resist remained on top of the GaAs nanowires. At this stage, the Si etching step had to be selective with HSQ and not laterally etch the GaAs nanowires. For that, we have to choose plasma chemistry that protects sidewalls, as schematized by a green covering layer in Figure 5a. The false-color SEM image (Figure 5b) shows the result after the anisotropic Cl<sub>2</sub> plasma step usually used to define vertical Si nanostructures. An Pure Cl<sub>2</sub>

Figure 5. Heterostructured GaAs/Si nanowires: (a) Process flow chart. (b) Two successive plasma etchings (GaAs with the current plasma procedure followed by Si etching using plasma-based  $Cl_2$  chemistry). (c)  $O_2$  is added with  $Cl_2$  to avoid anisotropic etching of the GaAs nanowires. (d) Two successive plasma etchings:  $Cl_2/N_2$  plasma for GaAs nanowires and then  $SF_6/C_4F_8/O_2$  plasma for Si nanowires, resulting in heterostructured GaAs/Si nanowires with a GaAs length of 640 nm and a Si length of 270 nm. (e) Colorized SEM image of 910 nm high heterostructured GaAs/Si nanowires with a diameter ranging between 40 and 90 nm.

plasma is highly isotropic due to GaAs nanowire degradation. To enhance the SiO<sub>x</sub> layer deposition and to protect the GaAs nanowire sidewall, short O2 plasma cycles were added during the Cl<sub>2</sub> etching process (O<sub>2</sub> plasma for 30 s and Cl<sub>2</sub> plasma for 30 s), and GaAs/Si nanowires with an axial heterostructure were obtained (Figure 5b). However, the main drawback of these cycles of Cl<sub>2</sub> plasma/O<sub>2</sub> plasma was the poor selectivity between HSQ and Si (~1). To improve this situation, a process based on fluorine chemistry (SF<sub>6</sub>/C<sub>4</sub>F<sub>8</sub>/O<sub>2</sub>) was introduced, providing a Si/HSQ selectivity of 5. Figure 5d shows the SEM images of a network of 100 heterostructured GaAs/Si nanowires with a diameter of 40 nm and a pitch between nanowires of 200 nm. The colorized SEM image shown in Figure 5e demonstrates 910 nm high heterostructured GaAs/Si nanowires with a diameter ranging between 40 and 90 nm. For perfect patterning of these heterostructured nanowires, the challenge is to master the transition between the two etching chemistries without degrading the Si/GaAs interface. Therefore, detection of the endpoint during GaAs etching is critical. This Si/GaAs interface is detailed in Supporting Information Figure S2. The overetching of GaAs must be less than 3 s; otherwise, the lateral etching at the bottom of the nanowires would be accentuated, resulting in mechanical fragility of the nanowires and carrier mobility scattering.

#### CONCLUSIONS

For the first time, we demonstrated the fabrication of a vertical III–V (GaAs or GaSb) nanowire array on a standard Si(100) microelectronic platform by a wafer-scale approach that is complementary metal—oxide—semiconductor compatible using low-corrosive chlorine-based chemistry. III–V nanowires patterned on a Si(100) substrate with a high aspect ratio (up to 15). The nanostructures were structurally characterized to

evaluate the crystalline defects of the GaAs nanowires. This top-down approach enables perfect control of all of the nanostructure features (location, verticality, diameter, aspect ratio, and density). Moreover, this approach was pushed forward by combining two sequential plasma etching steps to pattern GaAs—Si nanowires with an axial heterostructure that has a diameter of 40 nm and a length of 900 nm. This large-scale technology on the Si(100) platform paves the way for new integration schemes for large-scale applications in nanoelectronics, nanophotonics, or photovoltaics.

#### ASSOCIATED CONTENT

#### Supporting Information

The Supporting Information is available free of charge at https://pubs.acs.org/doi/10.1021/acsomega.1c05876.

Figure S.1: Optical emission spectrometry (OES) measurements OES at 1 and 50 W and Figure S.2: endpoint detection during GaAs etching to master the GaAs/Si interface of heterostructured nanowires (PDF).

#### AUTHOR INFORMATION

#### **Corresponding Author**

Guilhem Larrieu – LAAS-CNRS, Université de Toulouse, CNRS, INP, Toulouse 31031, France; orcid.org/0000-0001-5157-2277; Phone: +33 56133 7984; Email: glarrieu@laas.fr

#### **Authors**

Aurélie Lecestre — LAAS-CNRS, Université de Toulouse, CNRS, INP, Toulouse 31031, France Mickael Martin — Univ. Grenoble Alpes, CNRS, CEA-Leti/ Minatec, Grenoble INP, LTM, F-38054 Grenoble, France Filadelfo Cristiano — LAAS-CNRS, Université de Toulouse, CNRS, INP, Toulouse 31031, France Thierry Baron — Univ. Grenoble Alpes, CNRS, CEA-Leti/ Minatec, Grenoble INP, LTM, F-38054 Grenoble, France; orcid.org/0000-0001-5005-6596

Complete contact information is available at: https://pubs.acs.org/10.1021/acsomega.1c05876

#### **Notes**

The authors declare no competing financial interest.

#### ACKNOWLEDGMENTS

The authors thank F. Carcenac, P. Dubreuil, and B. Reig from LAAS-CNRS for technical assistance. This work was supported by Idex UNITI Toulouse (VERTELEC Emergence Project 2016-071-CIF-D-DRDV), by the DGA, the ANR LEGO (ANR-18-CE24-0005-01), and the LAAS-CNRS micro and nanotechnology platform, a member of the Renatech French National Network.

#### REFERENCES

- (1) Tomioka, K.; Yoshimura, M.; Fukui, T. A III–V nanowire channel on silicon for high-performance vertical transistors. *Nature* **2012**, 488, 189–192.

- (2) Ganjipour, B.; Wallentin, J.; Borgström, M. T.; Samuelson, L.; Thelander, C. Tunnel field-effect transistors based on InP-GaAs heterostructure nanowires. ACS Nano 2012, 6, 3109–3113.

- (3) Yan, R.; Gargas, D.; Yang, P. Nanowires photonics. *Nature Photonics* **2009**, *3*, 569–576.

- (4) Saxena, D.; Mokkapati, S.; Parkinson, P.; Jiang, N.; Gao, Q.; Tan, H. H.; Jagadish, C. Optically pumped room-temperature GaAs nanowire lasers. *Nat. Photonics* **2013**, *7*, 963–968.

- (5) Hällström, W.; Lexholm, M.; Suyatin, D. B.; Hammarin, G.; Hessman, D.; Samuelson, L.; Montelius, L.; Kanje, M.; Prinz, C. N. Fifteen-piconewton force detection from neural growth cones using nanowire arrays. *Nano Lett.* **2010**, *10*, 782–787.

- (6) Dhindsa, N.; Chia, A.; Boulanger, J.; Khodadad, I.; LaPierre, R.; Saini, S. S. Highly ordered vertical GaAs nanowire arrays with dry etching and their optical properties. *Nanotechnology* **2014**, *25*, No. 305303.

- (7) Åberg, I.; Asoli, D.; Naseem, U.; Gilboy, J. P.; Sundvall, C.; Dahlgren, A.; Svensson, K. E.; Anttu, N.; Björk, M. T.; Samuelson, L.; et al. A GaAs Nanowire Array Solar Cell With 15.3% Efficiency at 1 Sun. *IEEE J. Photovoltaics* **2016**, *6*, 185–190.

- (8) Tomioka, K.; Motohisa, J.; Hara, S.; Hiruma, K.; Fukui, T. GaAs/AlGaAs core multishell nanowire-based light-emitting diodes on Si. *Nano Lett.* **2010**, *10*, 1639–1644.

- (9) Signorello, G.; Karg, S.; Björk, M. T.; Gotsmann, B.; Riel, H. Tuning the light emission from GaAs nanowires over 290 meV with uniaxial strain. *Nano Lett.* **2013**, *13*, 917–924.

- (10) Marasovic, I.; Garma, T.; Betti, T. Modelling a nanowire grid for light-sensing applications. *J. Phys. D: Appl. Phys.* **2012**, 45, No. 215102.

- (11) Joyce, H. J.; Boland, J. L.; Davies, C. L.; Baig, S. A.; Johnston, M. B. A review of the electrical properties of semiconductor nanowires: insights gained from terahertz conductivity spectroscopy. *Semicond. Sci. Technol.* **2016**, *31*, No. 103003.

- (12) Semiconductor nanowires II: properties and applications; Dayeh, S. A.; Dayeh, S. A.; Morral, A. F.; Jagadish, C., Eds.; Academic Press Elsevier, 2016; Vol. 94.

- (13) Li, Q.; Lau, K. M. Epitaxial growth of highly mismatched III-V materials on (001) silicon for electronics and optoelectronics. *Prog. Cryst. Growth Charact. Mater.* **2017**, *63*, 105–120.

- (14) Choi, H. In Vapor-Liquid-Solid Growth of Semiconductor Nanowires Semiconductor Nanostructures for Optoelectronic Devices; Yi, G. C., Ed.; Springer: Berlin, 2012; pp 1–36.

- (15) Güniat, L.; Martí-Sánchez, S.; Garcia, O.; Boscardin, M.; Vindice, D.; Tappy, N.; Friedl, M.; Kim, W.; Zamani, M.; Francaviglia, L.; Balgarkashi, A.; Leran, J.-B.; Arbiol, J.; Morral, A. F. III–V

- integration on Si (100): Vertical nanospades. ACS Nano 2019, 13, 5833-5840.

- (16) Cavalli, A.; Wang, J.; Zadeh, I. E.; Reimer, M. E.; Verheijen, M. A.; Soini, M.; Plissard, S. R.; Zwiller, V.; Haverkort, J. E. M.; Bakkers, E. P. A. M. High-yield growth and characterization of  $\langle 100 \rangle$  InP p-n diode nanowires. *Nano Lett.* **2016**, *16*, 3071–3077.

- (17) Plissard, S.; Dick, K. A.; Larrieu, G.; Godey, S.; Addad, A.; Wallart, X.; Caroff, P. Gold-free growth of GaAs nanowires on silicon: arrays and polytypism. *Nanotechnology* **2010**, *21*, No. 385602.

- (18) Paek, J. H.; Nishiwaki, T.; Yamaguchi, M.; Sawaki, N. Catalyst free MBE-VLS growth of GaAs nanowires on (111)Si substrate. *Phys. Status Solidi C* **2009**, *6*, 1436–1440.

- (19) Borg, M.; Schmid, H.; Moselund, K. E.; Signorello, G.; Gignac, L.; Bruley, J.; Breslin, C.; Kanungo, P. D.; Werner, P.; Riel, H. Vertical III–V nanowire device integration on Si(100). *Nano Lett.* **2014**, *14*, 1914–1920.

- (20) Merckling, C.; Waldron, N.; Jiang, S.; Guo, W.; Collaert, N.; Caymax, M.; Vancoille, E.; et al. Heteroepitaxy of InP on Si(001) by selective-area metal organic vapor-phase epitaxy in sub-50 nm width trenches: The role of the nucleation layer and the recess engineering. *J. Appl. Phys.* **2014**, *115*, No. 023710.

- (21) Zhao, X.; Alamo, J. A. Nanometer-scale vertical-sidewall reactive ion etching of InGaAs for 3-D III-V MOSFETs. *IEEE Electron Device Lett.* **2014**, *35*, 521–523.

- (22) Zhao, X.; Lin, J.; Heidelberger, C.; Fitzgerald, E. A.; del Alamo, J. A. Vertical nanowire InGaAs MOSFETs fabricated by a top-down approach. *Tech. Dig. Int. Electron Devices Meet.* **2013**, 28.4.1–28.4.4.

- (23) Naureen, S.; Shahid, N.; Sanatinia, R.; Anand, S. Top-down fabrication of high quality III-V nanostructures by monolayer controlled sculpting and simul-taneous passivation,. *Adv. Funct. Mater.* **2013**, 23, 1620–1627.

- (24) Merckling, C.; Waldron, N.; Jiang, S.; Guo, W.; Collaert, N.; Caymax, M.; Vancoille, E.; Barla, K.; Thean, A.; Heyns, M.; Vandervorst, W. Heteroepitaxy of InP on Si(001) by selective-area metal organic vapor-phase epitaxy in sub-50 nm width trenches: The role of the nucleation layer and the recess engineering. *J. Appl. Phys.* **2014**, *115*, No. 023710.

- (25) Cipro, R.; Baron, T.; Martin, M.; Moeyaert, J.; David, S.; Gorbenko, V.; Bassani, F.; Bogumilowicz, Y.; Barnes, J. P.; Rochat, N.; Loup, V.; Vizioz, C.; Allouti, N.; Chauvin, N.; Bao, X. Y.; Ye, Z.; Pin, J. B.; Sanchez, E. Low defect InGaAs quantum well selectively grown by metal organic chemical vapor deposition on Si(100) 300 mm wafers for next generation non planar devices. *Appl. Phys. Lett.* **2014**, *104*, No. 262103.

- (26) Alcotte, R.; Martin, M.; Moeyaert, J.; Cipro, R.; David, S.; Bassani, F.; Ducroquet, F.; Bogumilowicz, Y.; Sanchez, E.; Ye, Z.; Baron, X. Y.; Pin, J. B.; Baron, T. Epitaxial growth of antiphase boundary free GaAs layer on 300 mm Si(001) substrate by metalorganic chemical vapour deposition with high mobility. *APL Mater.* **2016**, *4*, No. 046101.

- (27) Guerfi, Y.; Carcenac, F.; Larrieu, G. High resolution HSQ nanopillar arrays with low energy electron beam lithography. *Microelectron. Eng.* **2013**, *110*, 173–176.

- (28) Jalabert, L.; Dubreuil, P.; Carcenac, F.; Pinaud, S.; Salvagnac, L.; Granier, H.; Fontaine, C. High aspect ratio GaAs nanowires made by ICP-RIE etching using Cl2/N2 chemistry. *Microelectron. Eng.* **2008**, *85*, 1173–1178.

- (29) Volatier, M.; Duchesne, D.; Morandotti, R.; Arès, R.; Aimez, V. Extremely high aspect ratio GaAs and GaAs/AlGaAs nanowaveguides fabricated using chlorine ICP etching with N2-promoted passivation. *Nanotechnology* **2010**, *21*, No. 134014.

- (30) Bouchoule, S.; Patriarche, G.; Guilet, S.; Gatilova, L.; Largeau, L.; Chabert, P. Sidewall passivation assisted by a silicon coverplate during Cl2—H2 and HBr inductively coupled plasma etching of InP for photonic devices. *J. Vac. Sci. Technol., B: Microelectron. Nanometer Struct.—Process., Meas., Phenom.* **2008**, 26, 1071—1023.

- (31) Lee, J. W.; Noh, H. S.; Lee, S. H.; Park, J. H.; Choi, K. H.; Pearton, S. J. Dry etching process of GaAs in capacitively coupled BCl3-based plasmas. *Thin Solid Films* **2010**, *518*, 6488–6491.

- (32) Maeda, T.; Lee, J. W.; Shul, R. J.; Han, J.; Hong, J.; Lambers, E. S.; Pearton, S. J.; Abernathy, C. R.; Hobson, W. S. Inductively coupled plasma etching of III—V semiconductors in BCl3-based chemistries: I. GaAs, GaN, GaP, GaSb and AlGaAs. *Appl. Surf. Sci.* 1999, 143, 174—182.

- (33) Vigneron, P. B.; Joint, F.; Isac, N.; Colombelli, R.; Herth, E. Advanced and reliable GaAs/AlGaAs ICP-DRIE etching for optoelectronic, microelectronic and microsystem applications. *Microelectron. Eng.* **2018**, 202, 42–50.

- (34) Chao, J.-J.; Wang, D.-S.; Shiu, S.-C.; Hung, S.-C.; Lin, C.-F. Controlled formation of well-aligned GaAs nanowires with a high aspect ratio on transparent substrates. *Semicond. Sci. Technol.* **2010**, 25, 065014.

- (35) Park, S.; Kim, S.-S.; Wang, L.; Ho, S.-T. InGaAsP-InP nanoscale waveguide-coupled microring lasers with submilliampere threshold current using Cl/sub 2/–N/sub 2/-based high-density plasma etching. *IEEE J. Quantum Electron.* **2005**, 41, 351–356.

- (36) Strasser, P.; Wuest, R.; Robin, F.; Erni, D.; Jackel, H. Detailed analysis of the influence of an inductively coupled plasma reactive-ion etching process on the hole depth and shape of photonic crystals in InP/InGaAsP. *J. Vac. Sci. Technol.B* **2007**, 25, 387.

- (37) Park, Y. H.; Kim, J. K.; Lee, J. H.; Joo, Y. W.; Noh, H. S.; Lee, J. W.; Pearton, S. J. N2 effect on GaAs etching at 150 mTorr capacitively-coupled Cl2/N2 plasma. *Microelectron. Eng.* **2010**, 87, 548–552.

- (38) Liu, K.; Ren, X-m.; Huang, Y-q.; Cai, S-w.; Duan, X-f.; Wang, Q.; Kang, C.; Li, J-s.; Chen, Q-t.; Fei, J-r. Inductively coupled plasma etching of GaAs in Cl2/Ar, Cl2/Ar/O2 chemistries with photoresist mask. *Appl. Surf. Sci.* **2015**, *356*, 776–779.

- (39) Cerba, T.; Martin, M.; Moeyaert, J.; David, S.; Rouviere, J. L.; Cerutti, L.; Alcotte, R.; Rodriguez, J. B.; Bawedin, M.; Boutry, H.; Bassani, F.; Bogumilowicz, Y.; Gergaud, P.; Tournié, E.; Baron, T. Anti phase boundary free GaSb layer grown on 300 mm (001)-Si substrate by metal organic chemical vapor deposition. *Thin Solid Films* **2018**, *645*, 5–9.

- (40) Cerba, T.; Hauchecorne, P.; Martin, M.; Moeyaera, J.; Alcotte, R.; Salem, B.; Eustache, E.; Bezard, P.; Chevalier, X.; Lombard, G.; Bassani, F.; David, S.; Beainy, G.; Tournié, E.; Patriarche, G.; Boutry, H.; Bawedin, M.; Baron, T. InAs/GaSb thin layers directly grown on nominal (001)-Si substrate by MOVPE for the fabrication of InAs FINFET. J. Cryst. Growth 2019, 510, 18–22.

- (41) Wu, Y.; Xiang, J.; Yang, C.; Lu, W.; Lieber, C. M. Single-crystal metallic nanowires and metal/semiconductor nanowire heterostructures. *Nature* **2004**, *430*, 61–65.

- (42) Lauhon, L. J.; Gudiksen, M. S.; Lieber, C. M. Semiconductor nanowire heterostructures. *Philos. Trans. R. Soc., A* **2004**, 362, 1247–1260.

- (43) Han, X. L.; Larrieu, G.; Dubois, E. Realization of vertical silicon nanowire networks with an ultra-high density using a top-down approach. *J. Nanosci. Nanotechnol.* **2010**, *10*, 7423–7427.