# Thermal consideration in nanoscale gate-all-around vertical transistors

Guilhem Larrieu, Houssem Rezgui, Abhishek Kumar, Jonas Müller, Sylvain Pelloquin, Yifan Wang, Marina Deng, Aurélie Lecestre, Cristell Maneux, Mukherjee Chhandak

### ▶ To cite this version:

Guilhem Larrieu, Houssem Rezgui, Abhishek Kumar, Jonas Müller, Sylvain Pelloquin, et al.. Thermal consideration in nanoscale gate-all-around vertical transistors. Silicon Nanoelectronics Workshop (SNW 2023), Jun 2023, Kyoto, Japan. pp.27-28, 10.23919/SNW57900.2023.10183951. hal-04189328

## HAL Id: hal-04189328 https://laas.hal.science/hal-04189328v1

Submitted on 29 Aug2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### Thermal consideration in nanoscale gate-all-around vertical transistors

Guilhem Larrieu<sup>1</sup>, Houssem Rezgui<sup>2</sup>, Abhishek Kumar<sup>1</sup>, Jonas Müller<sup>1</sup>, Sylvain Pelloquin<sup>1</sup>, Yifan

Wang<sup>2</sup>, Marina Deng<sup>2</sup>, Aurélie Lecestre<sup>1</sup>, Cristell Maneux<sup>2</sup>, Chhandak Mukherjee<sup>2</sup>

<sup>1</sup>LAAS CNRS, UPR 8001, CNRS, Université of Toulouse, France <sup>2</sup> IMS laboratory, University of Bordeaux, France.

Email: glarrieu@laas.fr

Abstract — Devolvement of high-performance logic application in sub-20 nm technology node has gained significant attention due to their improved electrostatic and thermal control. In this work, we investigate electro-thermal transport in vertical junctionless nanowire transistors (VNWFET) at cryogenic temperatures to understand thermal effects in nanoscale regime. It highlights that heat dissipation and thermal stability are more efficient compared to planar Finfet configuration.

*Keywords:* Semiconductor, junctionless nanowire transistors, nanoscale thermal transport, thermal conductivity, cryogenic.

#### I. INTRODUCTION:

In the present era, transistors have attained a state of high miniaturization, with technology nodes such as N5 possessing physical gate lengths less than 20 nm. At these scales, classical physical principles confront competing mechanisms and configurations intrinsic to the nanoscale. Additionally, in short channel lengths thermal management poses significant challenges, encompassing low thermal stability and leakage current due to self-heating effects and hot-spot formation [1]. This paper presents an investigation of the thermal properties of a vertical conduction sub-20 nm gate-all-around (GAA) junctionless transistor technology, a promising candidate for future technology nodes due to its ability to support denser architectures through a compact device layout. Given its highly miniaturized design and unconventional layout of metallic and insulating layers, this architecture is particularly intriguing for addressing thermal challenges of highly advanced devices. In this scope, it has thus become crucial that design considerations include renewed focus on electrothermal optimizations to satisfy Moore's law trends [2]. Thermal conduction is governed by phonon transport in sub-10 nm devices that include (1) ballistic, (2) boundary scattering and (3) confinement regimes [3]. Guyer and Krumhansl equation (GKE) has recently been demonstrated to capture non-diffusive heat transport in nanoscale regime beyond the classical Fourier's law, offering understanding of non-local thermal effects [4]. Based on the GKE formulation, this work investigates for the first time electrothermal behavior of nanoscale GAA junctionless transistors.

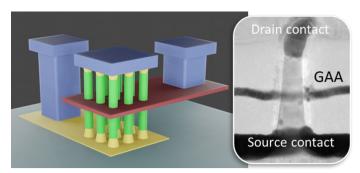

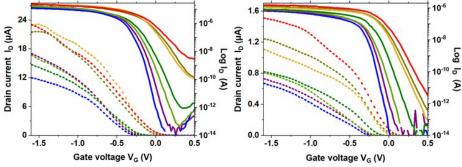

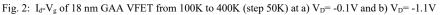

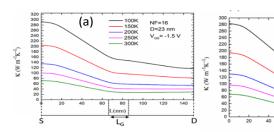

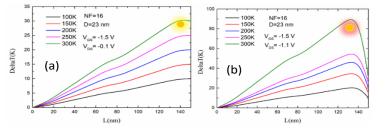

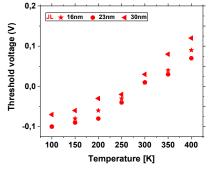

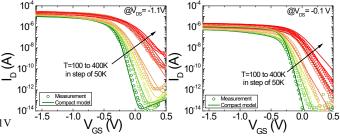

II. DEVICE AND TEMPERATURE CHARACTERIZATION Fig.1 present a schematic view of the vertical junction-less device with a metallic GAA of 18 nm and symmetrical PtSi contacts, as described in [5]. The measured I<sub>D</sub>-V<sub>G</sub> curves are plotted in Fig. 2 for different temperatures ranging between 100 K  $\leq$  T  $\leq$  400 K, for p-Type JL GAA MOSFETs (Fig. 2) with a NW diameter 23 nm. The drive current increases monotonically with the temperature both at low and high V<sub>D</sub>, in accordance with the behavior observed for junctionless FETs [6]. The decrease in drain current at lower temperatures can be attributed to the suppression of the thermally-activated conducting currents at the contact which is not compensated by the improvement of mobility at low temperature. A transition between low and high temperature regimes for  $V_{th}$  (reflected by a change of slope of the  $V_{th}$ -T plot in Fig. 3) at around 200-300 K, exhibit a NW size-dependent transition of the dominant scattering mechanisms in the nanostructures. The subthreshold slope evolution with the temperature for different NW diameters (Fig. 4) is compared to a theoretical prediction for MOSFET devices (ln10·(KT/q)).

#### III. THERMAL ANALYSIS

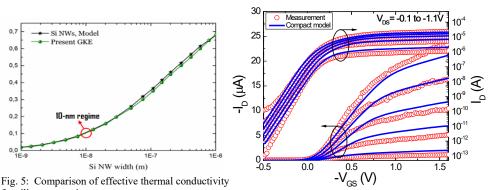

Through cryogenic static characterizations and finite element modeling, we studied heat accumulation in a single nanowire using COMSOL Multiphysics [7] based on GKE formulation. Unlike the linear temperature gradient in classical regimes, non-Fourier transport can accurately describe nonequilibrium states in both steady and transient ultrafast nanoscale thermal transport based on GKE and energy conservation. Non-local response of phonon destitution is used for the prediction of the effective thermal conductivity in nanowires as shown in Fig. 5, illustrating that the present GKE matches well with the reported data [8]. Thermal conductivity reduces significantly below the 10-nm regime. Distribution of thermal conductivity and temperature along the nanowire, shown in Figs. 6 and 7, respectively, indicate a degradation of thermal performances near the drain region due to the dominance of resistive phonon transport. However, beyond the point of heat accumulation near the drain, especially at V<sub>D</sub>= -1.1V, device temperature drops rapidly towards the drain contact (Fig. 7), indicating an efficient heat evacuation that further improves with more parallel nanowires. In terms of electrical performance under temperature, a key parameter for the junctionless device is its threshold voltage, which shows two distinct temperature coefficients between two heat conductive regimes separated around 250K (Fig. 3). The VNWFET compact model [9] has been adapted to incorporate this effect through temperature dependence of key parameters such as Vth, Schottky barrier, Raccess, vsat and SS. Following model calibration against room temperature data (Fig. 8), good model accuracy was achieved for drain current temperature dependence (Fig. 9), highlighting the need for better understanding of nanoscale thermal transport for accurate electro-thermal modelling. Finally, Table 1 demonstrates that the extracted thermal conductivity in JLNTs is higher than FinFETs technologies. The structure of GAA JLNTs guarantee less confinement effects and therefore higher effective thermal conductivity. In technological point of view, JLNT is more thermally stable.

#### CONCLUSIONS

We investigated nanoscale electrothermal transport in sub 20 nm GAA vertical nanowire junctionless transistors. Results indicate two distinct heat conduction regimes at low and high temperature ranges that were taken into account to model its electrical characteristics. Efficient heat dissipation and better thermal stability justify the benefits of this technology as a beyond CMOS alternative.

#### **ACKNOWLEDGMENTS**

This work was supported by the project FVLLMONTI funded by European Union's H2020 program (Nº101016776) and by the LAAS-CNRS micro and nanotechnologies platform, a member of the Renatech french national network

#### REFERENCES

[1] H. Zhang, et al. J. Phys. Chem. C, 122(5), 2641-2647, 2018. [2] A. L. Moore, L. Shi, Materials Today, 14 (4), 163-174, 2014. [3] S. Know et al. Nanoscale, 8(27), 13155-13167, 2016. [4] Y. Guo et al. Phys. Rev. B, 97, 035421-27, 2018. [5] Y Guerfi, G Larrieu, Nanoscale Res. Lett., 11 (2016) 210. [6] C.-W. Lee, et al. IEEE Trans. Electron Dev. 57(3), 620, 2010. [7] COMSOL, Inc., COMSOL Multiphysics [8] J. Lai et al. IEEE Trans. Electron Dev., 67, 4085, 2020. [9] C. Mukherjee et al. Solid-State Electron, 183, 2021. [10] H. Rezgui, et al., IEEE Trans. Electron Dev.68(1), 2021

Fig. 1: Schematic and TEM cross section view of the vertical junction-less GAA devices. The metallic GAA features 18nm gate length. The channel is p-type homogeneous doping (3E19 at.cm-3) and have symmetrical Pt-silicided contacts.

0,7

0,6

0,5

0,

0.2

0,1

0,0 1E

× NN 0,3 Si NWs, Model

Present GKE

IΠ-nm re

1E-8

for silicon nanowire at room temperature

100K

150K

200K

250K

80

L(nm)

(b)

1E-7

Si NW width (m)

NF=16 D=23 nm

V\_= -1.5 V

1E-6

Fig. 4: Evolution of SS as a function of temperature

Effective thermal conductivity along the nanowire for (a)  $V_{ds}$ = -0.1V. (b)  $V_{ds}$ = -1.1V Fig. 6:

Fig. 7: The temperature distribution within the nanowire for (a)  $V_{ds}$ =-0.1V. (b)  $V_{ds}$ =-1.1V

Fig. 3: Evolution of Vth as a function of temperature

Fig. 8: Compact model validation at room temperature

Fig. 9: Compact model validation against temperature data at  $V_{DS}$  = -1.1V and -0.1V.

|          | JLNTs      | FinFET      |

|----------|------------|-------------|

| 23-nm Lg | 18 (W/m/K) | 12 (W/m/K)  |

| 18-nm Lg | 10 (W/m/K) | 8.2 (W/m/K) |

Table 1: The extracted thermal conductivity in SOI FinFETs [10] and JLNTs (present work)