# ITEC+EATS 2022 Short Course Software-Defined Power Electronics: Theory and Study Cases

Matthias Preindl, Luiz Fernando Lavado Villa, Liwei Zhou, Matthew Jahnes,

Jean Alinei

#### ► To cite this version:

Matthias Preindl, Luiz Fernando Lavado Villa, Liwei Zhou, Matthew Jahnes, Jean Alinei. ITEC+EATS 2022 Short Course Software-Defined Power Electronics: Theory and Study Cases. Doctoral. ITEC + EATS Conference 2022 Anaheim, CA, United States. 2022, pp.139. hal-04430648

## HAL Id: hal-04430648 https://laas.hal.science/hal-04430648

Submitted on 1 Feb2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Distributed under a Creative Commons Attribution - NonCommercial - ShareAlike 4.0 International License

# ITEC+EATS 2022 Short Course Software-Defined Power Electronics: Theory and Study Cases

Matthias Preindl, Columbia University Luiz Villa, University of Toulouse Liwei Zhou, Columbia University Matthew Jahnes, Columbia University Jean Alinei, University of Toulouse

TRANSCENDING DISCIPLINES, TRANSFORMING LIVES

$\Delta \Delta C$

CNrs

- I. Introduction (Luiz 9min, Matthias 12min, Luiz 9min).

- II. Software-Defined Control Techniques (Liwei 15min)

- III. Software-Defined Hardware Design (Matthew 30min)

- IV. Design case of Transformerless Converter (Liwei 15min)

- V. Zephyr-Based Implementation (Luiz 60min)

- VI. Design case of Multi-Level Converters (Matthias 15min)

- VII. Conclusion (Matthias 8min, Luiz 7min)

# Introduction

Matthias Preindl, Luiz Villa

TRANSCENDING DISCIPLINES, TRANSFORMING LIVES

# Background - The Great Energy Transition

COLUMBIA | ENGINEERING The Fu Foundation School of Engineering and Applied Science

- Is a branch of electrical engineering  $\geq$

- Electronics that is made to handle power flows  $\geq$

- Goes from mW to MW  $\geq$

- DC-DC and DC-AC (1 or 3 phase)  $\geq$

- **Application-oriented design**  $\geq$

- **Battery charging**

- **Energy management**  $\geq$

- Motor control  $\geq$

- **Grid connection of renewables**  $\geq$

CNrs

COLUMBIA | ENGINEERING

# Background - How does Power Electronics work?

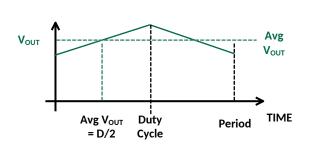

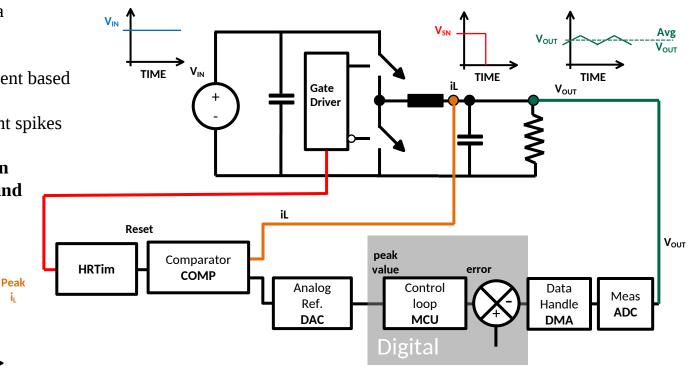

Open Digital Powe V<sub>SN</sub> Vout TIME TIME TIME Power **Switches** Filter VIN Gate Vout Driver PWM Control Modulator Duty TIME Cycle **Control Loop**

🚼 Columbia | Enginee

The Fu Foundation School of Engineering and Applied Science

V<sub>IN</sub>

CNrs

- Power converters regulate voltages and/or currents in either DC our AC

- Regulation is done through control loops

- Control loops use measurements to regulate power flow

- Power flow is controlled via PWM signals sent to the  $\geq$ power switches via gate driver circuits

- Output filters smooth out the output voltage and current

- **Real-Time is critical for stability**  $\geq$

- The P.E. community is very analog solution oriented  $\geq$

- We believe the time is ripe for digitalizing power electronics

- > Decarbonizing the economy will require more electricity

- > More electricity will require more power electronics

- Digitalization has emerged as a means to reduce time-to-market and standardize the development of solutions

- Energy transition will be greatly accelerated if power electronics becomes more standardized, modular and digital

**Open Digital Powe**

Two examples give a good idea of the state of the art of digitalization

- ≻ IoT

- Fully integrated software stack

- > No more bare metal

- Digital Power controllers

- Bare metal

- > Ultra-flexible micro-controllers with specialized peripherals

- High integration between peripherals

- Specialized for real-time control

- > Integrated fault-management and telemetry protocols

The Problem: On which target can we combine the abstraction API approach of IoT with the performance of dedicated analog peripherals ?

Columbia Engineering

The Fu Foundation School of Engineering and Applied Science

**UwnTech**

**Open Digital Power**

# Background - Digitalization state-of-the art

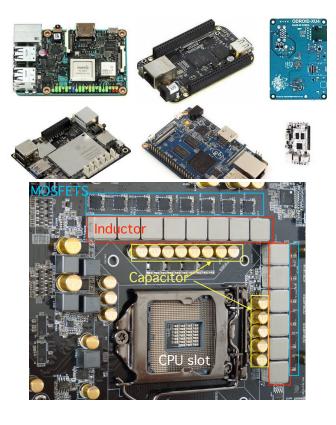

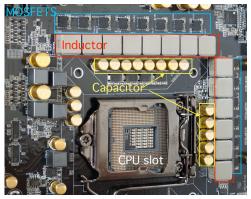

- Multiple silicon vendors have Digital power SoC in their portfolios

- Some are Function defined

- Multiphase converters for CPU power delivery

- Provide

Telemetry

- Optimize

control laws

- Tied to a specific use case

Some are reprogrammable as they can cover multiple power topologies.

- Digital power SoC do have

- > Dedicated High Resolution PWM generators

- Dedicated Fast Analog peripheral

- > ADC, DAC and comparators

- > Dedicated Hardware for fast control computation

- Some require vendor specific languages and libraries

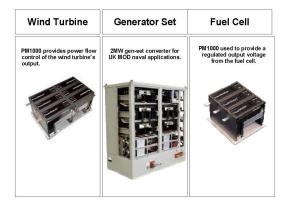

### Background - The pioneers

# **Power Electronics Building Blocks (PEBB):**

- ≻ Power component.

- ≻Control card.

- ≻Cooling system.

- ≻Communication system.

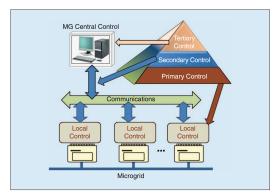

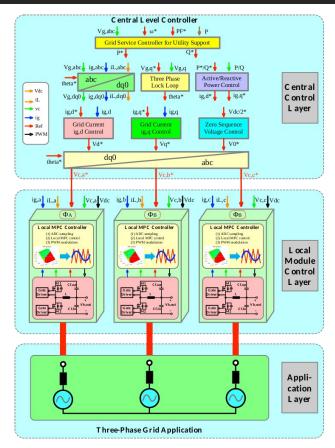

### **Microgrid Hierarchical Control Structure:**

- ≻Grid level central control.

- ➢ Distributed resource level local control.

- ≻ Communication system.

- ≻ Multi-layer control structure.

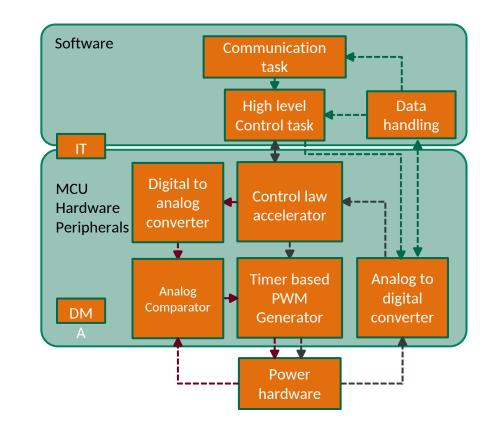

## Background - The digital Power Stack

COLUMBIA | ENGINEERING The Fu Foundation School of Engineering and Applied Science

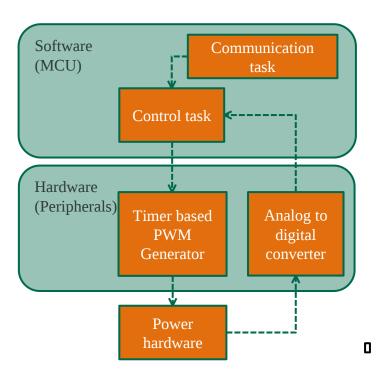

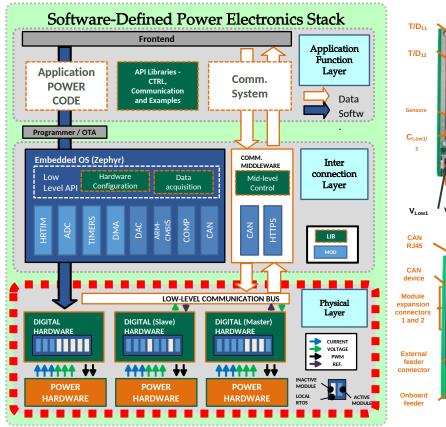

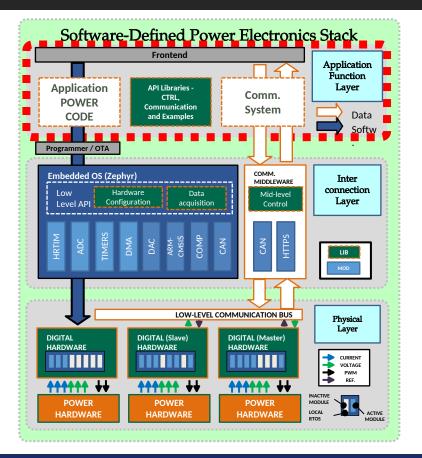

The digital power electronics stack has two parts: Software and Hardware Peripherals

- Software handles communication tasks and control

- Hardware comprises PWM Generation and ADC operation

Low level loop

- The power hardware sends data to the ADC and receives the PWM from the Timer

- > The control task drives the PWM

🚰 Columbia | Engineering

The Fu Foundation School of Engineering and Applied Science

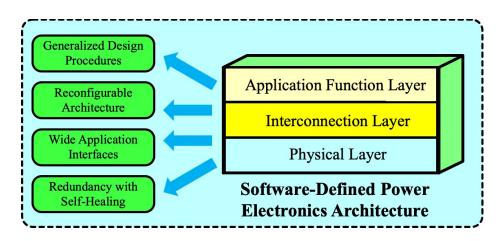

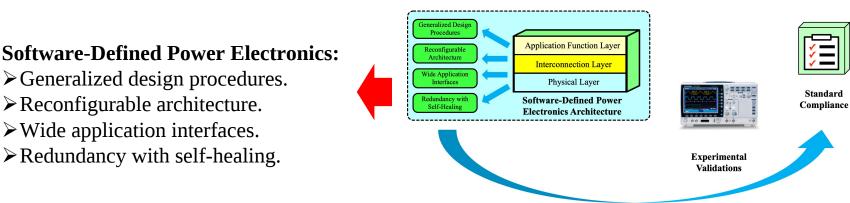

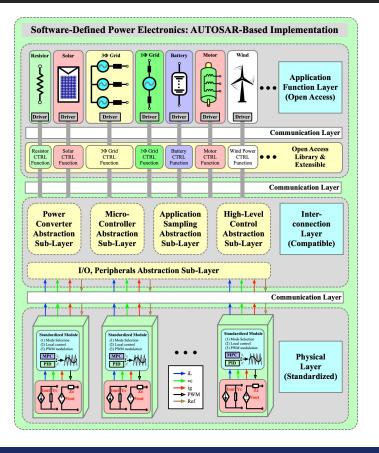

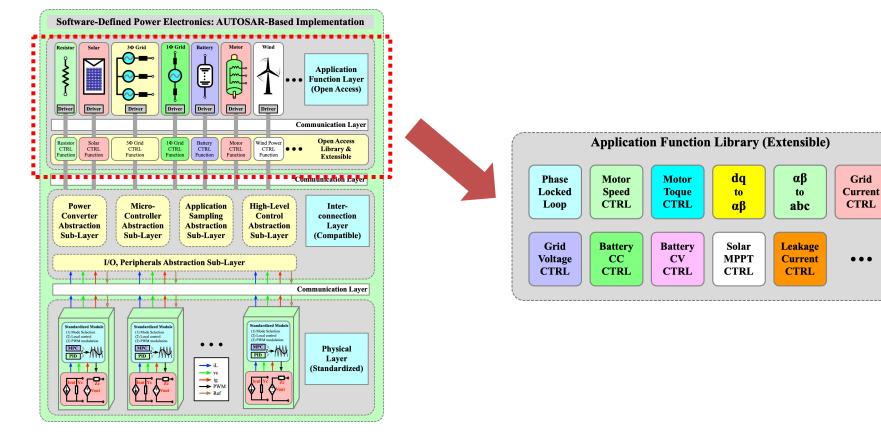

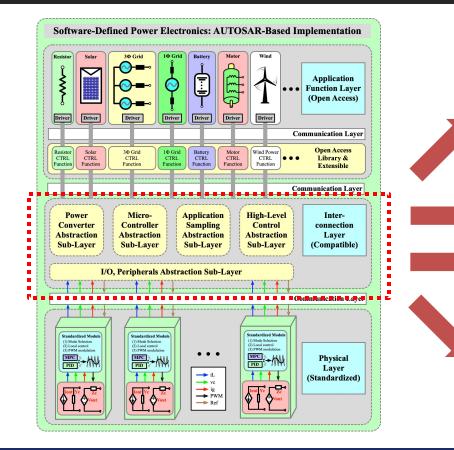

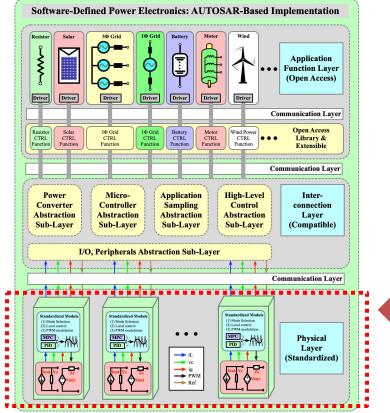

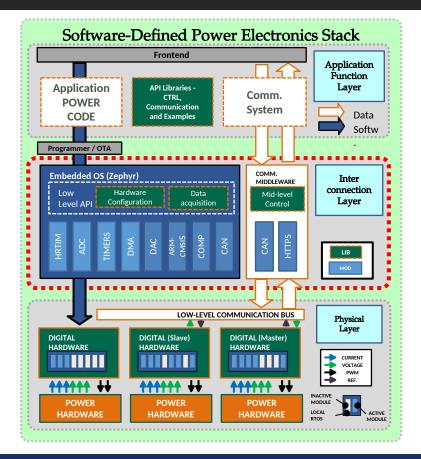

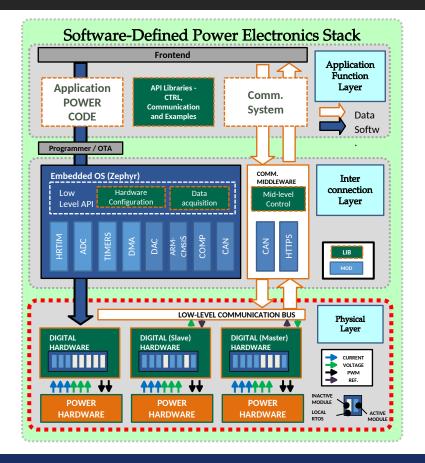

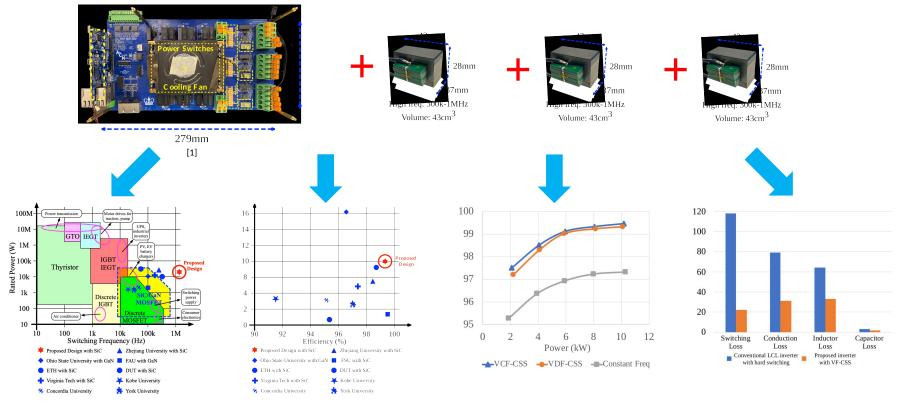

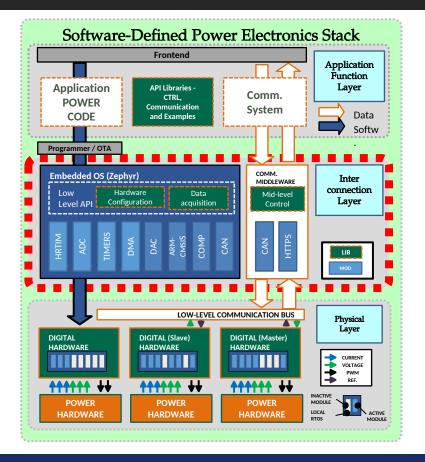

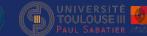

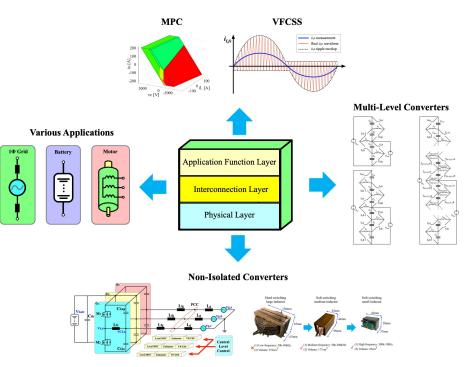

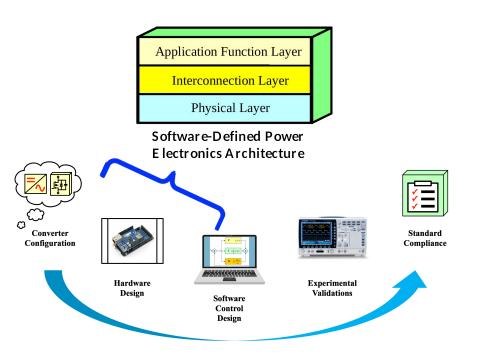

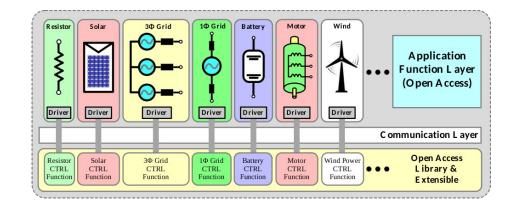

- Application Layer: Interfaced with Different load/source applications, e.g., EV battery, single/three-phase grid, solar, motor.

- Interconnection Layer: Manage power converters from module to integrated circuit; central power/voltage/current control functions.

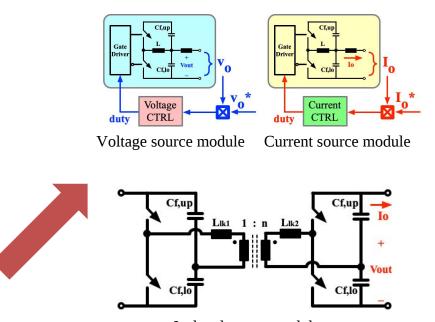

- Physical Layer: Voltage/current source types of module; local voltage/current stabilization; PWM modulation.

🚰 Columbia | Engineering

The Fu Foundation School of Engineering and Applied Science

$\overline{\Delta}$

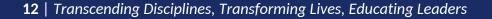

# **Conventional Power Electronics Design:**

- ≻ Various interfaced applications.

- Different power ratings.

- ≻Hardware design.

- ≻ Software design.

COLUMBIA | ENGINEERING The Fu Foundation School of Engineering and Applied Science

# **Two Multi-Layer Implementations:**

# ≻AUTOSAR-based implementation.

> Zephyr-based implementation.

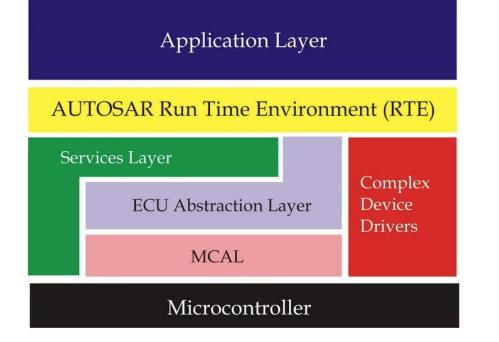

# **AUTOSAR Structure:**

- > Application Layer: application code.

- > AUTOSAR RTE: Running time environment.

- Service Layer: application services.

- ► ECU Abstraction Layer: I/O, hardware.

≻MCAL: micro-controller system.

🚼 Columbia | Engineering

The Fu Foundation School of Engineering and Applied Science

Application Layer: Interfaces and functions with different load/source applications, e.g., EV battery, single/three-phase grid, solar, motor.

Interconnection Layer: Link between application and physical layers; manage power converters from module to integrated system; central power/voltage/current control functions.

Physical Layer: Voltage/current source types of module; local voltage/current stabilization; PWM modulation.

**CNrS**

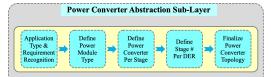

## **AUTOSAR-Based Implementation: Application Function Layer**

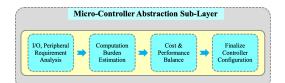

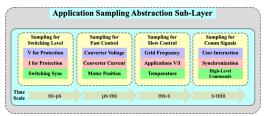

### AUTOSAR-Based Implementation: Interconnection Layer

COLUMBIA | ENGINEERING The Fu Foundation School of Engineering and Applied Science

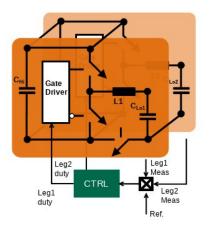

## **AUTOSAR-Based Implementation: Physical Layer**

COLUMBIA | ENGINEERING The Fu Foundation School of Engineering and Applied Science

Isolated power module

#### **Module Configuration:**

- ➤ Upper/lower power switches.

- ➢ Upper/lower output capacitors.

- Switch side inductor (optimized).

#### **Communications:**

- > CAN: Controller Area Network.

- ▶ FSI: Fast Serial Interface from TI.

- ➢ Ethernet.

The Fu Foundation School of Engineering and Apr

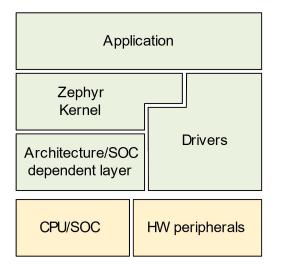

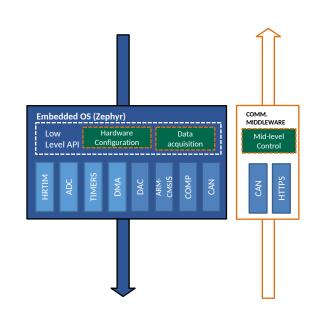

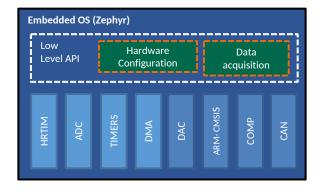

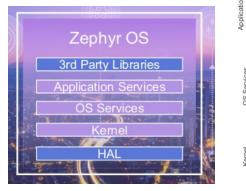

### Normal Zephyr layering

# **Zephyr Structure:**

CN

- $\blacktriangleright$  Application Layer: application code.

- > ZEPHYR KERNEL: Running time environment

- > Architecture/SOC dependent layer: peripherals unique to the target SOC

- Drivers Layer: Hardware agnostic drivers for SOC and peripherals

- SOC-HW peripherals: micro-controller system.

🚰 Columbia | Engineering

The Fu Foundation School of Engineering and Applied Science

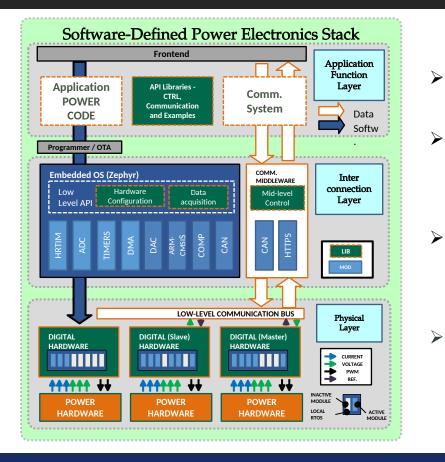

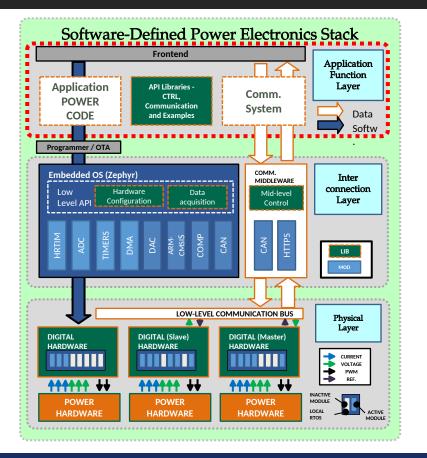

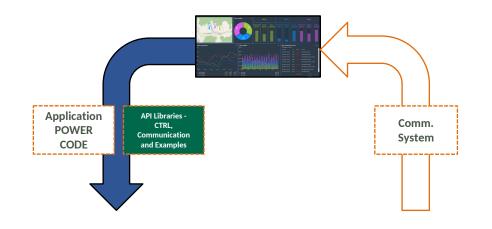

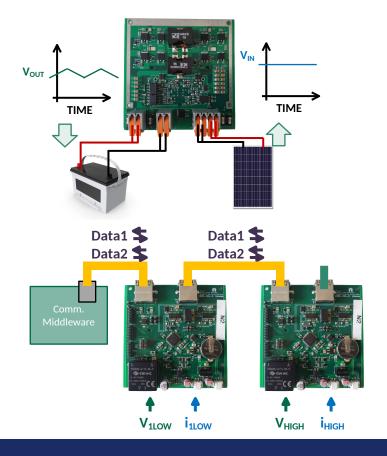

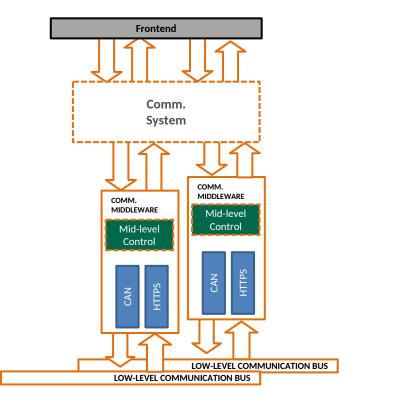

#### **Application Layer:**

- A frontend for data visualization and firmware update

- Libraries provide functions for power and data

#### Interconnection Layer:

- A programmer/over the air links the application to the Zephyr based system for code compiling and update

- A communication middleware provides bi-directional data flow and mid-layer control

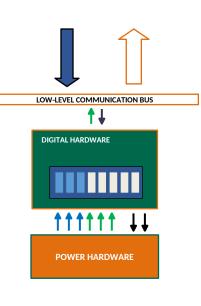

### **Physical Layer:**

- Each module is composed of a digital and power hardware connected to a low-level communication bus

- Multiple control schemes can be implemented: Decentralized, Mid-level or frontend based

### Downlink and Uplink

**CNrS**

- > The downlink flashes onto the digital hardware

- The uplink is done from a low-level bus to a communication system via a middleware

# Zephyr Based Implementation: Application Function Layer

# Zephyr Based Implementation: Interconnection Layer

Open Digital Power

# Zephyr Based Implementation: Physical Layer

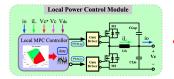

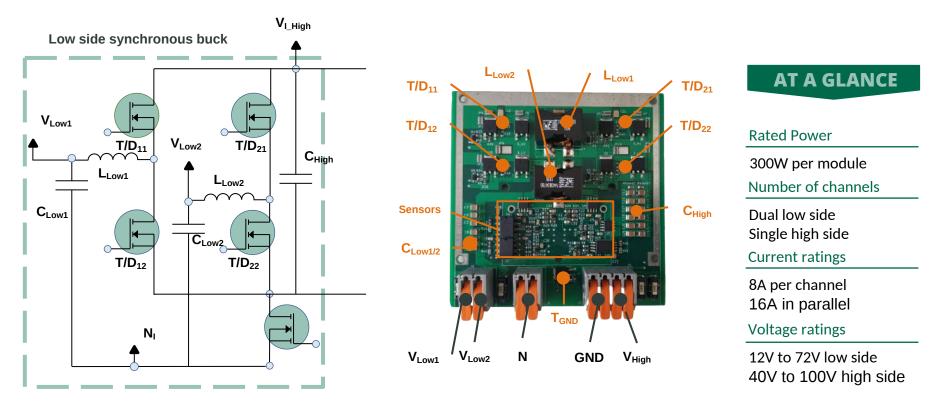

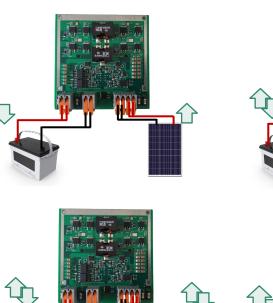

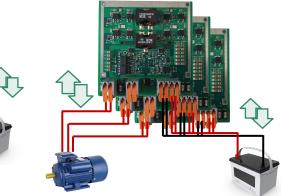

#### **Power Module Configuration:**

- > Two legs and a NGND switch

- Bi-directional DC-DC Buck/Boost

- Single phase DC-AC

### **Digital Module Configuration:**

- CAN: Controller Area Network.

- USB: Bootloader Programming and Over the Air capabilities

- > Serial and other extensions possible

# **Software-Defined Control Techniques**

Liwei Zhou

TRANSCENDING DISCIPLINES, TRANSFORMING LIVES

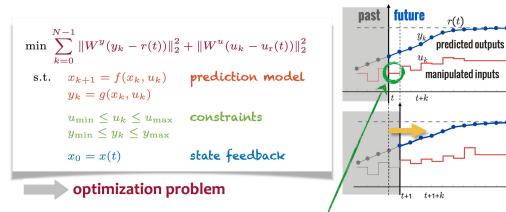

# Model Predictive Control Introduction

• **Goal**: find the best control sequence over a future horizon of *N* steps

### Advantages of MPC:

- Better dynamic performance.

- Multi-objective optimization.

- Optimize current timeslot with future timeslots in account.

- At each time *t*:

- get new measurements to update the estimate of the current state x(t)

- solve the optimization problem with respect to  $\{u_0,\ldots,u_{N-1}\}$

- apply only the first optimal move  $u(t)=u_0^*$ , discard the remaining samples

[1] 2019 A. Bemporad - "Model Predictive Control"

**28** | Transcending Disciplines, Transforming Lives, Educating Leaders

t+N

t+N+1

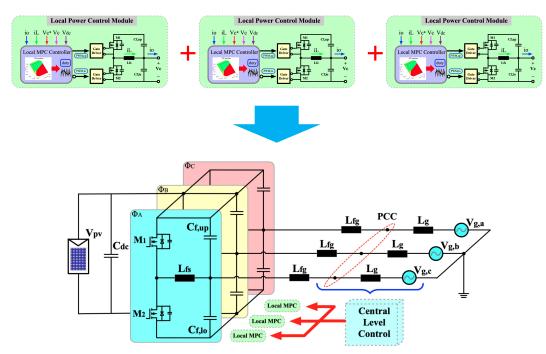

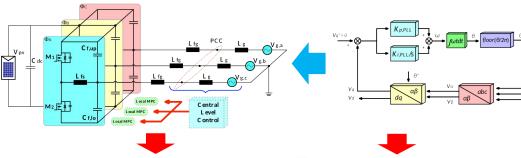

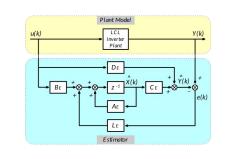

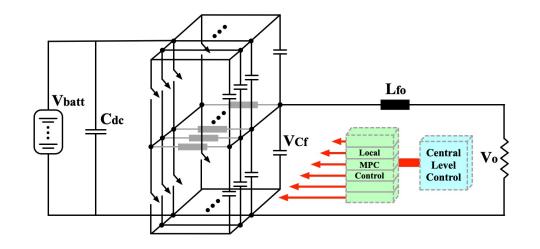

# Model Predictive Control for Modular Power Converters

#### **Discrete State Space Equations:**

$$i_{Lfs}(k+1) = i_{Lfs}(k) - \frac{T_s}{L_{fs}}v_{Cf}(k) + \frac{V_{dc}T_s}{L_{fs}}d(k)$$

$$v_{Cf}(k+1) = \frac{T_s}{C_f}i_{Lfs}(k) + v_{Cf}(k) - \frac{T_s}{C_f}i_{Lfg}(k)$$

#### **Standardized Format:**

$$X_{k+1} = AX_k + Bu_k + Ee_k$$

$$A = \begin{bmatrix} 1 - \frac{R_{Lfs}}{L_{fs}} & -\frac{T_s}{L_{fs}} \\ \frac{T_s}{C_f} & 1 \end{bmatrix}, B = \begin{bmatrix} \frac{T_s}{L_{fs}} \\ 0 \end{bmatrix}, E = \begin{bmatrix} 0 \\ -\frac{T_s}{C_f} \end{bmatrix},$$

$$X_k = \begin{bmatrix} i_{Lfs}(k) \\ v_{Cf}(k) \end{bmatrix}, u_k = \begin{bmatrix} V_{dc}d(k) \end{bmatrix}, e_k = \begin{bmatrix} i_{Lfg}(k) \end{bmatrix}.$$

**Cost Function:**

$$\min \quad \sum_{k=0}^{N_c} \tilde{X}_k^T Q \tilde{X}_k + \sum_{k=0}^{N_p-1} \triangle u_k^T R \triangle u_k$$

**Constraints:**

$$\begin{split} \tilde{X}_{k+1} &= A\tilde{X}_k + Bu_k + Ee_k \in \mathcal{X} \\ & \bigtriangleup u_k = u_k - u_{k-1} \in \mathcal{U} \\ \begin{bmatrix} -I_{Lfs,max} \\ 0 \end{bmatrix} \leq X_k \leq \begin{bmatrix} I_{Lfs,max} \\ V_{dc} \end{bmatrix} \\ \begin{bmatrix} 0 \end{bmatrix} \leq u_k \leq \begin{bmatrix} V_{dc} \end{bmatrix} \\ \begin{bmatrix} -I_{Lfg,max} \end{bmatrix} \leq e_k \leq \begin{bmatrix} I_{Lfg,max} \end{bmatrix}. \end{split}$$

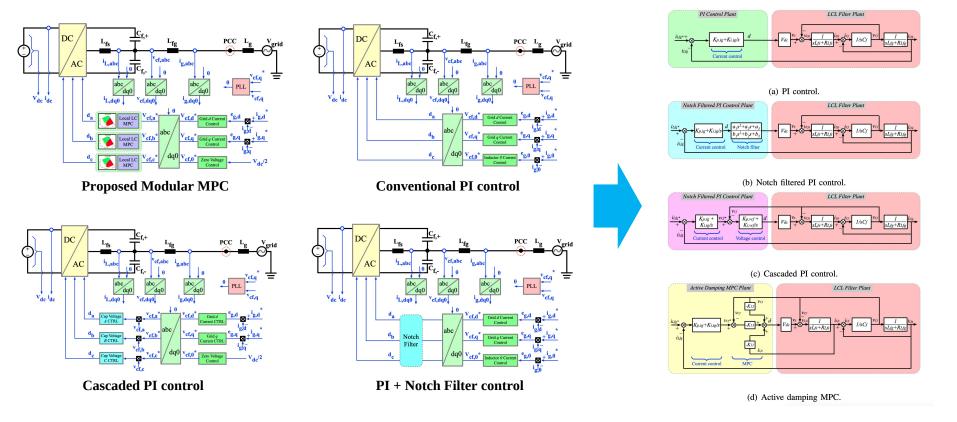

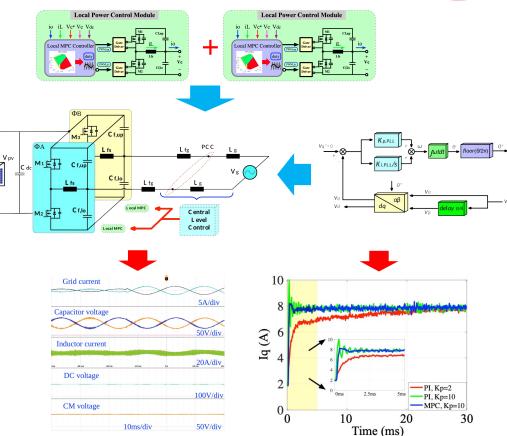

# Model Predictive Control for Modular Power Converters

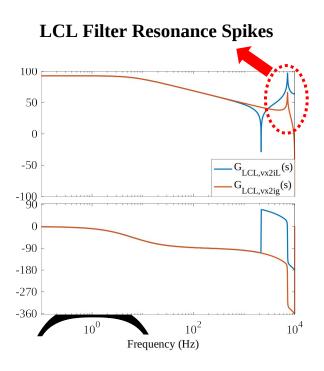

- Motivations: MPC for better dynamic performance; MPC for LCL filter active resonance damping.

- Methods: Modular MPC cascaded control structure including outer loop PI and inner loop per module MPC.

- Merits: Improved transient performance; Less resonance spikes; Higher control bandwidth.

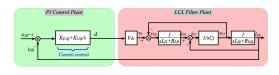

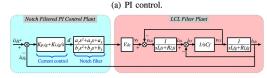

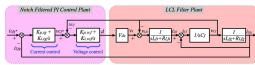

# Resonance Issue in Typical LCL Filter Inverter System

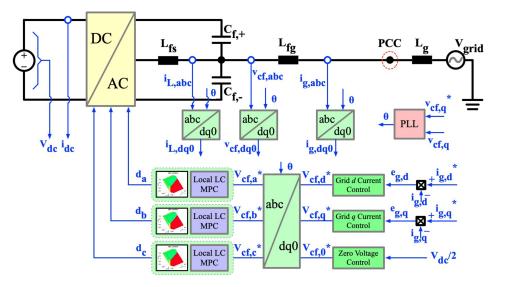

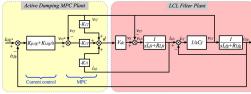

# Modular Model Predictive Control for Active Damping

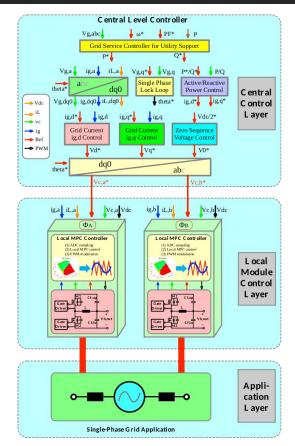

- Outer Loop Grid Current Control: Regulate grid current in dq0 reference frame with PI controller to derive the output capacitor references for innter loop MPC.

- Inner Loop Per Module MPC Control: Regulate output capacitor voltage in abc reference frame with MPC by receiving reference from outer loop PI.

- Phase-Locked Loop: Transformations between abc and dq0 reference frame for control purpose.

# Modular Model Predictive Control for Active Damping

# MPC Active Damping Mechanism

(b) Notch filtered PI control.

(d) Active damping MPC.

**34** | Transcending Disciplines, Transforming Lives, Educating Leaders

COLUMBIA | ENGINEERING The Fu Foundation School of Engineering and Applied Science

$10^{4}$

$10^{3}$

Frequency (Hz)

From Igrid error to Vcf

$10^{-2}$

**CNrS**

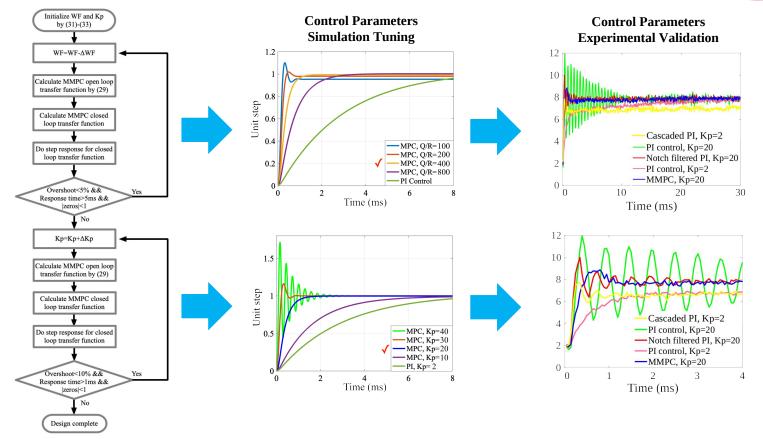

# MPC Control Parameters Design Method

COLUMBIA | ENGINEERING The Fu Foundation School of Engineering and Applied Science

Proposed MPC with high gain

Notch filtered PI with high gain

Conventional PI with high gain

Cascaded PI with high gain

#### Validated Merits of designed MPC:

- Active damping for LCL filter.

- Better dynamic performance.

- ➢ High control bandwidth.

- Less oscillation in steady state.

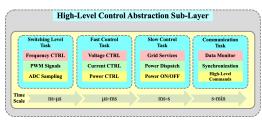

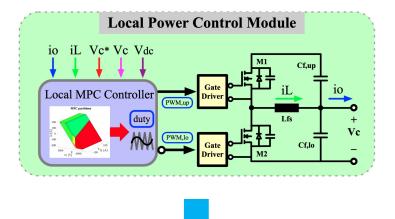

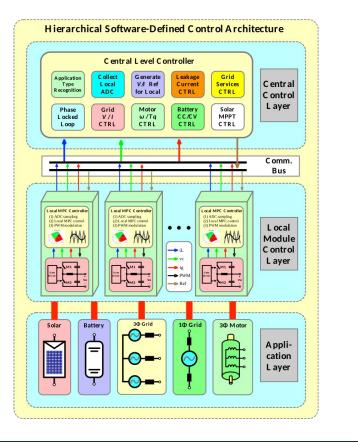

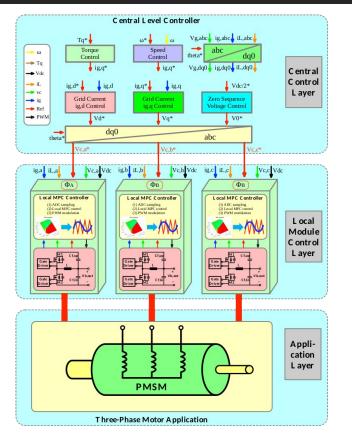

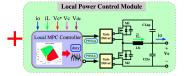

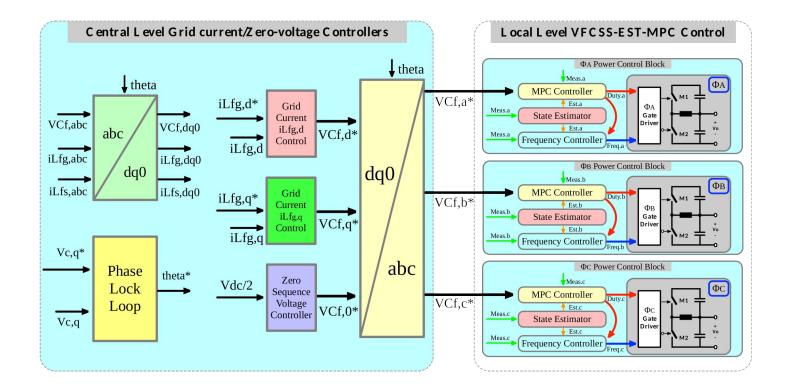

#### Hierarchical Software-Defined Power Electronics Architecture

Central Control Layer: Manage power converters from module to integrated circuitry topology; central voltage/current/power/torque/speed control functions; application type recognition.

Local Power Module Layer: Local voltage/current MPC control; variable-frequency critical-softswitching control; state observer; PWM modulation.

Application Layer: Interfaces with different electrified load/source applications, e.g., EV battery, single/three-phase grid, solar, motor.

### Single-Phase Grid-Connection Application

M

COLUMBIA | ENGINEERING The Fu Foundation School of Engineering and Applied Science

The Fu Foundation School of Engineering and Applied Science

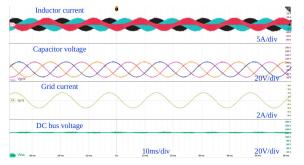

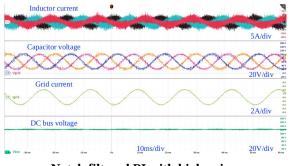

### Three-Phase Grid-Connection Application

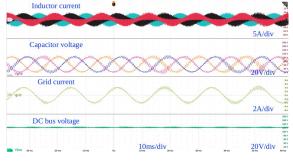

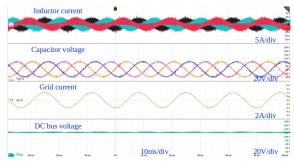

Inductor current

Capacitor voltage

Grid current

DC voltage

CM voltage

**39** | Transcending Disciplines, Transforming Lives, Educating Leaders

COLUMBIA | ENGINEERING The Fu Foundation School of Engineering and Applied Science

### Three-Phase Motor Traction Application

400

200

-200

0

0.01 0.02

0.03

Time (s)

COLUMBIA | ENGINEERING The Fu Foundation School of Engineering and Applied Science

**40** | Transcending Disciplines, Transforming Lives, Educating Leaders

0.04 0.05

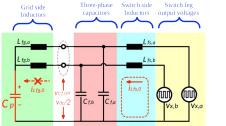

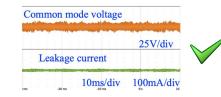

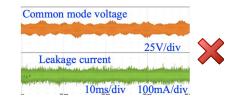

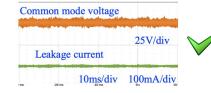

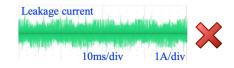

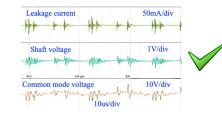

### Merits of Zero-Sequence Stabilization for Low CM Noise

Grid side

Inductors

0

Vx,c Vx,b Vx,a

#### **Proposed Control and Topology:**

#### **Conventional Control and Topology:**

Cf.c Cf.b Cf.a

## **Software-Defined Hardware Design**

**Matthew Jahnes**

TRANSCENDING DISCIPLINES, TRANSFORMING LIVES

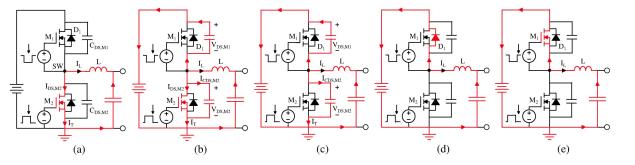

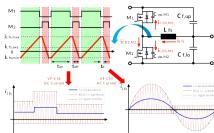

### Achieving High Efficiency and High Power Density Modules

- **1) Upper Capacitor topology** reduction in both EMI and capacitance RMS ripple for a given output capacitance

- allows for reduction in output capacitance

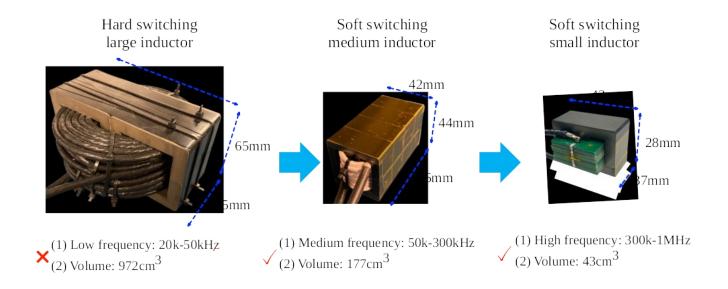

#### 2) Variable Frequency Critical Soft Switching (VFCSS)

- enables an increase in switching by factor of 5, reduction in inductance by factor of 10, without sacrificing efficiency

#### 3) Additional C<sub>oss</sub> Capacitance

- used in conjunction with critical soft switching scheme to reduce turn-off switching losses

#### 4) Optimization process for both size and efficiency

- procedure to optimize for both size and efficiency simultaneously

4 Methods:

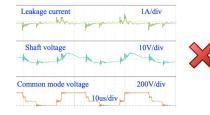

## Upper Capacitor Topology

### Upper Capacitor Topology

Columbia Engl

he Fu Foundation School of Engineering and

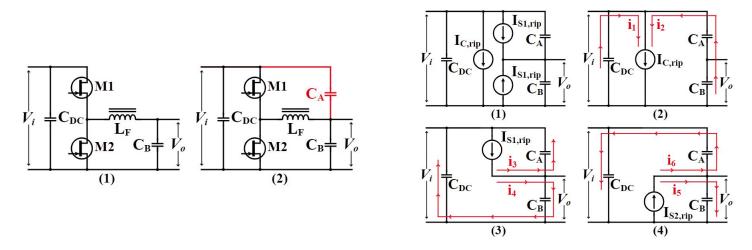

- Upper capacitor C<sub>A</sub> is not included in typical buck converters

- It allows for differential mode ripple currents present at  $V_{\text{o}}$  and  $V_{\text{i}}$  to be cancelled

- Increasing  $f_{\mbox{\tiny sw}}$  is a common way to reduce required inductance and capacitance

- However, it becomes ineffective beyond a certain frequency as the limit of ripple current handling capability of the output capacitance is reached

CNrs

### Upper Capacitor Topology

🚼 Columbia | Engineering

The Fu Foundation School of Engineering and Applied Science

- By partially cancelling out ripple currents within the output capacitance, we can lessen the ripple current handling capacitance requirements

- For a given total capacitance, allocating a proportion to C<sub>A</sub> brings:

- over 50% reduction in the switching frequency harmonic

- over 20% reduction in total capacitor ripple current

This allows for a reduction in output filter capacitance value and size

CNrs

## Variable Frequency Critical Soft Switching (VFCSS)

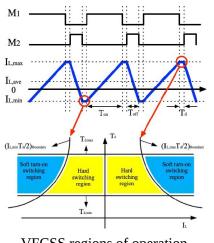

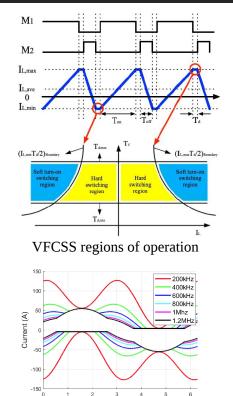

### Variable Frequency Critical Soft-Switching (VFCSS)

🖶 Columbia | Engineering

The Fu Foundation School of Engineering and Applied Science

VFCSS regions of operation

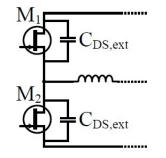

**Critical Soft Switching** allows for C<sub>ds</sub> capacitors to be charged/discharged through the natural current commutation of the inductor current

- and not by applying a step voltage during a forced  $V_{\text{ds}}$  transition

- instead, **FETs are switched "on" after the C**<sub>ds</sub> **capacitances have transitioned in voltage** (charged/discharged)

- this transition occurs during the deadtime of the switching states

- the product of the deadtime and the inductor current needs to be sufficient to charge/discharge  $C_{\rm ds}$  of both FETs

This allows for the exchange of turn-on losses for turn-off losses

B. Agrawal, L. Zhou, A. Emadi and M. Preindl, "Variable-Frequency Critical Soft-Switching of Wide-Bandgap Devices for Efficient High-Frequency Nonisolated DC-DC Converters," in *IEEE Transactions on Vehicular Technology*, vol. 69, no. 6, pp. 6094-6106, June 2020, doi: 10.1109/TVT.2020.2987028. L. Zhou and M. Preindl, "Optimal Frequency and Critical Soft Switching Control of DC/DC Converter," 2019 IEEE Energy Conversion Congress and Exposition (ECCE), 2019, pp. 1536-1541, doi: 10.1109/ECCE.2019.8912991.

L. Zhou and M. Preindl, "Variable-Switching Constant-Sampling Frequency Critical Soft Switching MPC for DC/DC Converters," in IEEE Transactions on Energy Conversion, vol. 36, no. 2, pp. 1548-1561, June 2021, doi: 10.1109/TEC.2021.305830

## Variable Frequency Critical Soft-Switching (VFCSS)

🚼 Columbia | Engi

The Fu Foundation School of Engineering and

Inductor current envelopes for different VFCSS upper f<sub>sw</sub> bounds

Effective Critical Soft-Switching requires:

- sufficient product of deadtime and inductor current

- correct inductor current direction

need to control the peaks and valleys of the inductor current ripple

$$T_{L,p-p} = \frac{D\left(1-D\right)V_{DC}}{f_{sw}L_{sw}}$$

The peak to peak inductor ripple current is a product of duty cycle, the DC voltage, switching frequency, and inductance

The DC term of the inductor ripple current is a product of the load

The switching frequency must be controlled to achieve a desired peak

and valley points of the inductor ripple current

Variable Frequency Critical Soft-Switching

Effective VFCSS requires high inductor ripple current, necessitating a decrease in inductance

allows for a simultaneous reduction in inductance (volume) and increase in efficiency

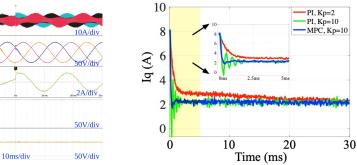

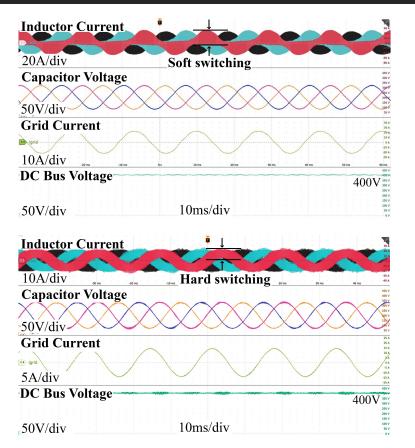

### Variable Frequency Critical Soft-Switching (VFCSS)

COLUMBIA | ENGINEERING The Fu Foundation School of Engineering and Applied Science

| 20A/div                | Sof | ft swi | tch   | ing | 1 | 6.6  |   | <br> | <br>  |      | -8      |

|------------------------|-----|--------|-------|-----|---|------|---|------|-------|------|---------|

| <b>Capacitor Volta</b> |     |        |       |     |   |      |   |      |       |      | 40      |

|                        |     |        |       |     |   | ~~~~ |   | <br> | <br>  |      | <br>21  |

| 50V/div                |     |        |       |     |   |      |   | <br> | <br>  |      | <br>1   |

| Grid Current           |     |        | 1     |     |   |      | 2 |      |       |      |         |

| larid-                 |     |        |       |     |   |      | 5 | <br> | <br>- |      | <br>- 1 |

|                        |     |        |       |     |   |      |   |      |       |      | 1       |

| 10A/div                |     |        | 20 15 |     |   |      |   |      |       | o us | 120     |

| 10A/div           | Hard switch                                                              | ing | 100 µs -2 | 00 µs  | -100 µs                                 |

|-------------------|--------------------------------------------------------------------------|-----|-----------|--------|-----------------------------------------|

| Capacitor Voltage |                                                                          |     |           |        | 45                                      |

| Capacitor voltage |                                                                          |     |           |        | 35                                      |

|                   |                                                                          |     | Linin     | hinini | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ |

| COT 7/ 1'         |                                                                          |     |           |        | 11                                      |

| 50V/div           |                                                                          |     |           |        | 10                                      |

| Grid Current      |                                                                          |     |           |        |                                         |

| Griu Current      |                                                                          |     |           |        |                                         |

| C4 larid          |                                                                          |     |           |        |                                         |

|                   |                                                                          |     |           |        |                                         |

| 5A/div            |                                                                          |     |           |        |                                         |

|                   |                                                                          |     |           |        |                                         |

| DC Bus Voltage    | ne (entroped a spectra da se de grades de grades de grades de la seconda |     |           |        | 40017                                   |

| 8                 |                                                                          |     |           |        | 400V                                    |

|                   |                                                                          |     |           |        | 25                                      |

| 50V/div           | 100us/div                                                                |     |           |        | 15                                      |

**51** | Transcending Disciplines, Transforming Lives, Educating Leaders

capacitances)

COLUMBIA | ENGINEERING The Fu Foundation School of Engineering and Applied Science

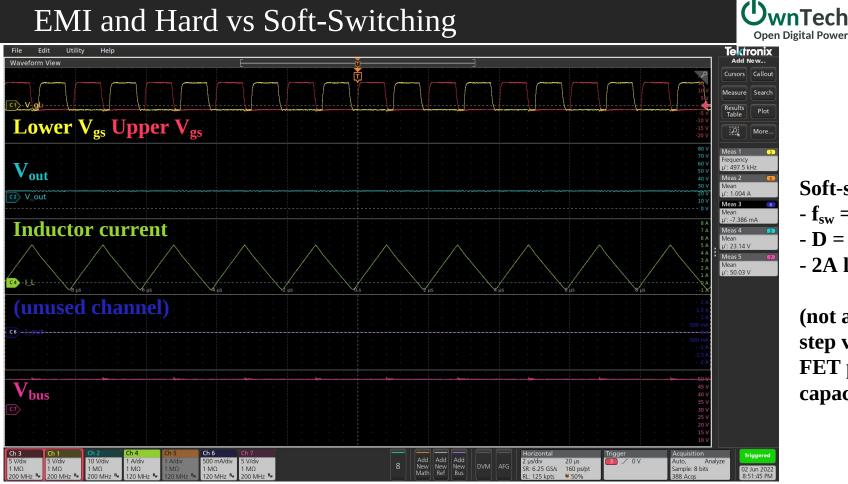

Soft-switching -  $f_{sw} = 500 kHz$ - D = 0.5 - 2A load

(not applying a step voltage to FET parasitic capacitances)

## Additional Coss Capacitance

### Additional C<sub>oss</sub> Capacitance

COLUMBIA | ENGINE

The Fu Foundation School of Engineering and Applied Science

- VFCSS incurs exclusively turn-off losses

- We can trade off turn-off switching energy with turn-on switching energy through additional Coss Capacitance

- This has the effect of slowing the switching transient time and reducing the  $V_{ds}$  I<sub>d</sub> overlap

CNrs

#### Additional Coss Capacitance

🚰 Columbia | Engineering

The Fu Foundation School of Engineering and Applied Science

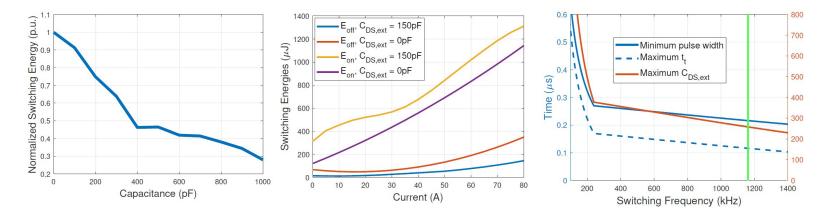

- The turn-off losses decrease with  $C_{ds,ext}$

- The turn-on losses have a proportionally higher increase with  $C_{ds,\text{ext}}$

- turn-on losses can be disregarded as VFCSS incurs only turn-off losses

- Switching transient time increases with  $C_{ds,ext}$ , necessitating an optimization process to balance the two

## Simultaneous Parameter Optimization for both Size and Efficiency

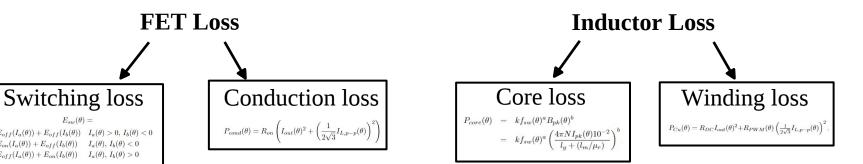

$P_{sw}(\theta) = f_{sw} E_{sw}(\theta)$

0 30 40 Drain to Source Current, L., (A)

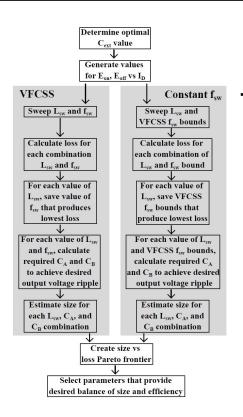

1) Develop a rigorous method for calculating loss as a function of circuit parameters

#### Adjustable circuit parameters:

- switching frequency range, inductance, switching device, additional  $C_{oss}$  capacitance

- it is often the case where loss in one mechanism is traded off for loss in another mechanism

- therefore, it is necessary to vary all parameters simultaneously and pick the set of optimal parameters for the application

CNrs

Columbia Engineering

The Fu Foundation School of Engineering and Applied Science

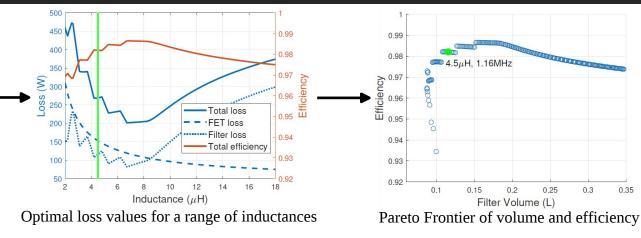

#### Parameter Optimization – Basic Efficiency Optimizatoin

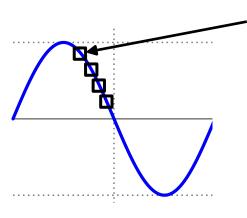

The operating point of an inverter changes with the phase of the output cycle

The optimization must also take place over the entire cycle of the grid

**a)** Loss at discrete points along the sine wave calculated for a given set of parameters

**b)** Set of parameters iterated, loss calculations repeated

**c)** Parameters that produce the lowest loss are plotted against a controlled parameter

Theoretical maximum efficiency Pareto Frontier

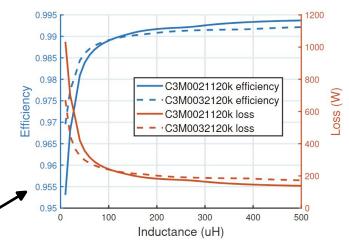

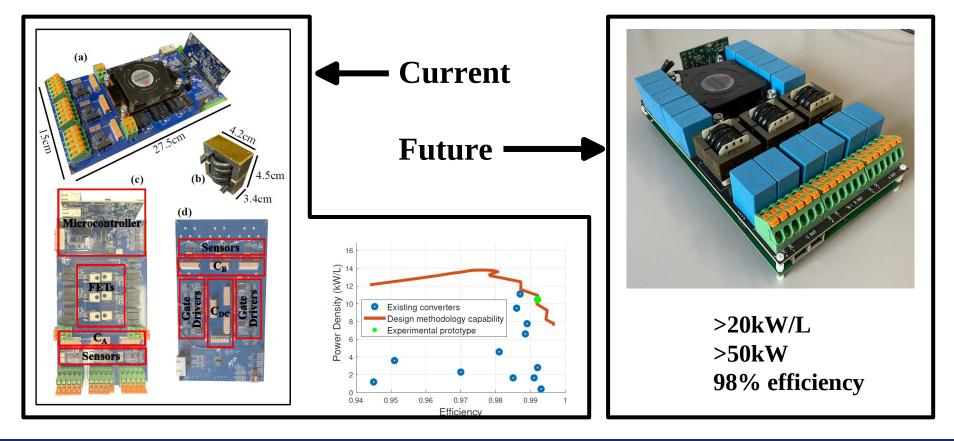

### Parameter Optimization – Advanced Efficiency and Size Optimization

- At each set of parameters the filter volume is estimated - plotting the filter volumes against the filter efficiencies results in a pareto front of volume vs efficiency

$$\frac{Y_L}{Y_L^*} = \left(\frac{E_L}{E_L^*}\right)^{\frac{3}{4}} = \left(\frac{0.5LI^2}{0.5L^*I^2}\right)^{\frac{3}{4}} = \left(\frac{L}{L^*}\right)^{\frac{3}{4}}$$

$$\frac{Y_C}{Y_C^*} = \left(\frac{E_C}{E_C^*}\right) = \left(\frac{0.5CV^2}{0.5C^*V^2}\right) = \left(\frac{C}{C^*}\right)$$

STATISTICS.

0.25

0.3

0.35

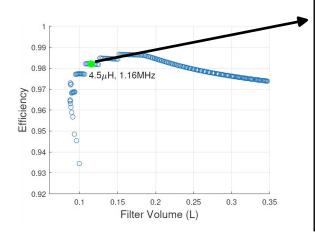

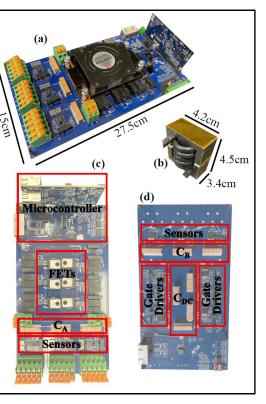

## Prototypes

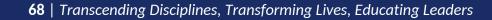

### Optimizing Size and Efficiency Simultaneously

- A desired operating point is chosen and experimental apparatus constructed

**Optimized converter parameters:**

- SiC CREE C3M0032120k

🚼 Columbia | Engineering

The Fu Foundation School of Engineering and Applied Science

- $50 kHz < f_{\rm sw} < 1.16 MHz$

- Inductance = **4.5**µ**H**

- 99.2% efficient

- 10.47kW/L

- 15kW

Prototypes

COLUMBIA | ENGINEERING The Fu Foundation School of Engineering and Applied Science

## Design Case of Transformerless Converter

Liwei Zhou

TRANSCENDING DISCIPLINES, TRANSFORMING LIVES

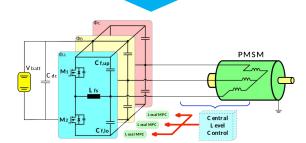

#### Design Case of Three-Phase Grid-Tied Inverter Control

Local MPC Estimator VF-CSS

VF-CSS

L ocal MPC Estimator

Local MPC Estimator VF-CSS

|Vbatt (━)

l=.

C entral

L evel

C ontrol

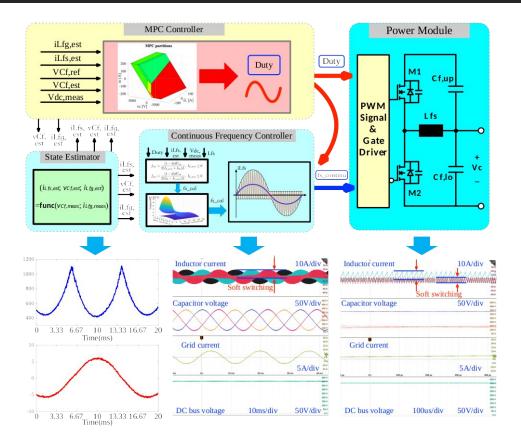

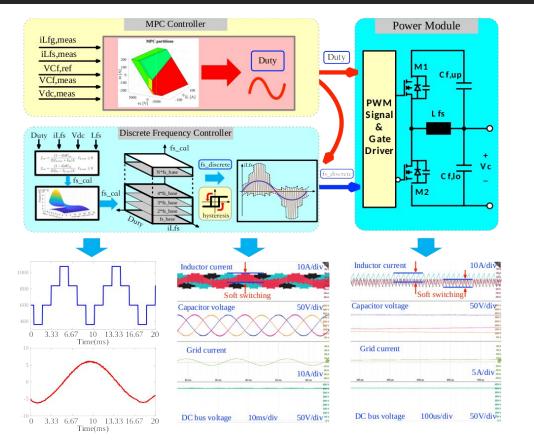

- VF-CSS: Variable-frequency critical-soft-switching to reduce the power losses and increase the power density.

- Modular MPC: Explicit MPC for per phase power module to improve the dynamic performance.

- State Estimator: Reduce the sensor cost and improve the anti-noise capability.

**64** | Transcending Disciplines, Transforming Lives, Educating Leaders

C f.up

C f.lo

L fs

M2 🛱 🕯

#### Holistic Control Diagram of Three-Phase Grid-Tied Inverter

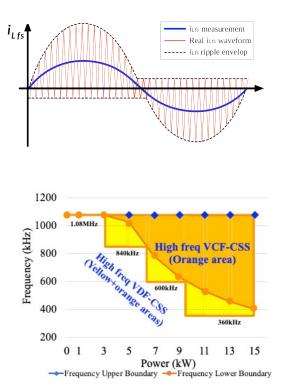

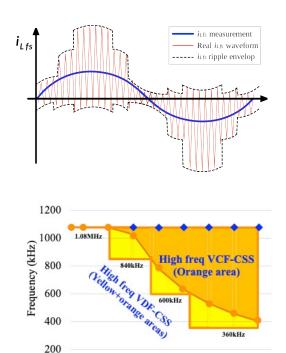

### Variable-Continuous-Frequency Critical-Soft-Switching (VCF-CSS)

### Variable-Discrete-Frequency Critical-Soft-Switching (VDF-CSS)

0

13 15

Power (kW) Frequency Upper Boundary Frequency Lower Boundary

#### Volume Reduction and Frequency Increase of Inductor Due to VF-CSS

Merits of the Designed Three-Phase Grid-Tied Inverter

COLUMBIA | ENGINEERING The Fu Foundation School of Engineering and Applied Science

[1] Board designed by Matthew Jahnes

# Zephyr-Based Implementation of Software Defined Power Electronics

Luiz Villa

TRANSCENDING DISCIPLINES, TRANSFORMING LIVES

#### Zephyr Based Software Defined Power Electronics

🚰 Columbia | Engineering

The Fu Foundation School of Engineering and Applied Science

#### **Application Layer:**

- A frontend for data visualization and firmware update

- Libraries provide functions for power and data

#### Interconnection Layer:

- A programmer/over the air links the application to the Zephyr based system for code compiling and update

- A communication middleware provides bi-directional data flow and mid-layer control

#### **Physical Layer:**

- Each module is composed of a digital and power hardware connected to a low-level communication bus

- Multiple control schemes can be implemented: Decentralized, Mid-level or frontend based

#### Downlink and Uplink

CN

- > The downlink flashes onto the digital hardware

- The uplink is done from a low-level bus to a communication system via a middleware

# Software Defined Reprogrammable System Design

TRANSCENDING DISCIPLINES, TRANSFORMING LIVES

# Understanding the contraints - Revisiting control methods

COLUMBIA | ENGINEE The Fu Foundation School of Engineering and Ap

The Fu Foundation School of Engineering and Applied Science

#### **Objective**

- Deduce the main constraints on the digital  $\geq$ power hardware

- 3 main control schemes cover 90% of use  $\geq$ cases

#### Voltage mode

Average measurements  $\geq$

#### **Current Mode**

Average and Peak Measurements  $\succ$

#### Voltage mode

Average and external measurements  $\geq$

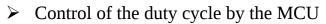

# Understanding the constraints - Voltage Mode Control

- Less Hardware intensive

- Average Measurement based control

- Can be done with non-specialized micro-controllers

- Precision in the Measurement is necessary

**CNrS**

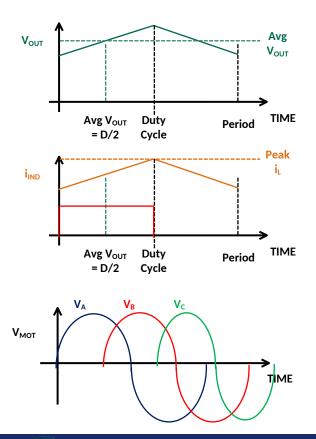

# Understanding the constraints - Voltage Mode Control

COLUMBIA | ENGINEERING The Fu Foundation School of Engineering and Applied Science

The Fu Foundation School of Engineering and Applied Science

- Control of the duty cycle by a  $\geq$ comparator

- Very hardware intensive  $\geq$

**i**IND

- Average and Peak Measurement based  $\geq$ control

- Provides safety againts current spikes  $\geq$ and overloads

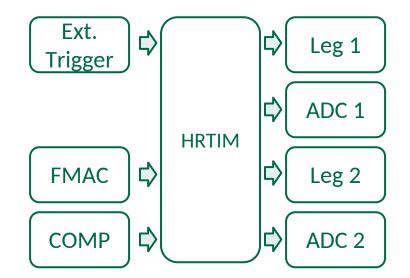

- **Requires a direct connection**  $\geq$ between the ADC, COMP and HRTIM

Duty

Cycle

Avg Vout

= D/2

CNrs

**75** | Transcending Disciplines, Transforming Lives, Educating Leaders

Period

TIME

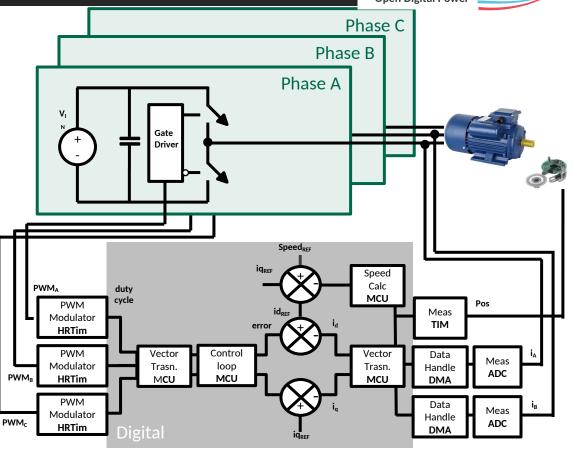

# Understanding the constraints - Voltage Mode Control

Open Digital Power

🔂 Columbia | Engineering

The Fu Foundation School of Engineering and Applied Science

$\overline{\Delta}$

- Control of the duty cycle by the MCU

- Very calculation intensive

- Requires handling many measurements

- Average control measurement based control

- Control bandwidth limited by the motor dynamics

- It may require external measurements

CNrs

Understanding the contraints - The digital power electronics stack

🔂 Columbia | Engineering

The Fu Foundation School of Engineering and Applied Science

#### **Critical real-time needs**

- ➢ Fast control tasks

- > Fast acquisition

- Fast communiation

- Very precise timers and PWMs

#### **Peripheral needs**

- Multiple triggers

- Multiple DMAs

- > ADC and PWM synchronization

- Dense and efficient Peripheral-to-Peripheral connection

#### **Communication Needs**

- Fast low-layer communication for decentralized control/synchronization

- Slow high layer communication for hierarchical/centralized control

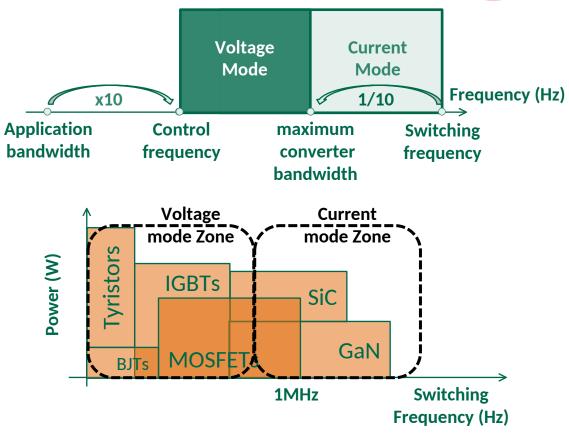

# Understanding the contraints - Digital Power Bandwidth Theory

## There are 2 constraints for controlling a

#### power converter

- The maximum bandwidth of a converter is 1/10 of its switching frequency

- The minimum frequency of the control is x10 of the application bandwidth

#### Voltage Mode lies in between

It is often associated with higher-order safety features for peak current

#### **Current Mode requires hardware** acceleration

## **Sensor Bandwidth**

- Voltage sensor = 10 x Application bandwidth

- Current sensor = 10 x switching frequency

Number of Switching legs is a complexity

factor

Switch Technology is linked with the choice of the Power SoC

CNrs

# Software Defined Power Hardware Design

TRANSCENDING DISCIPLINES, TRANSFORMING LIVES

# Zephyr Based SDPE Physical Layer

#### **Power Hardware Design**

- Hardware constraints and the iso-power curve theory

- > The choice of the number of legs

- The developed solution

#### Digital Module Design

- The implications of different control techniques on the digital SoC

- Digital hardware constraints and the digital control bandwidth theory

🔂 Columbia | Engineering

The Fu Foundation School of Engineering and Applied Science

The developed solution

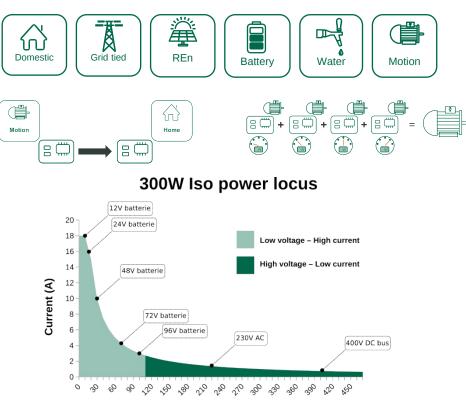

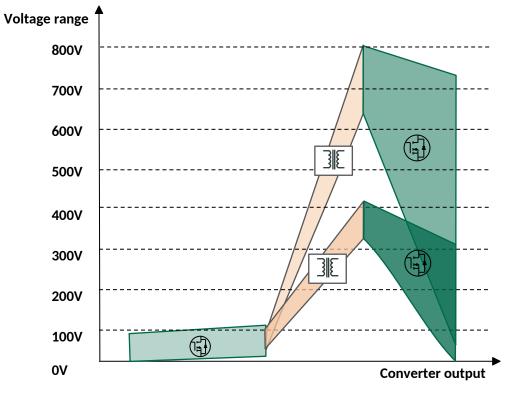

# Constraints for the sizing of the Power Hardware

COLUMBIA | ENGINEERING

#### **Reprogrammable functions**

- From application to conversion level

- Current bi-directional

- DC and AC Capabilities

#### Standard and Stackable Hardware

- Isolated digital board

- High Frequency for smaller modules

- Ergonomics is a key issue

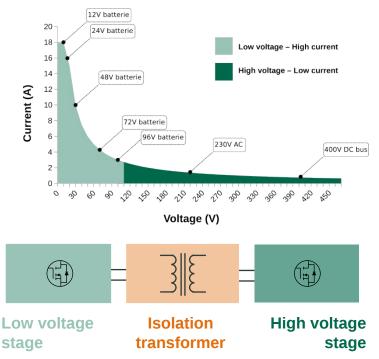

#### **Iso-Power Curve Theory**

- Low voltage and high current side

- High Voltage and low current side

Voltage (V)

CNrs

# **Open Digital Power**

COLUMBIA | ENGINEERING The Fu Foundation School of Engineering and Applied Science

The Fu Foundation School of Engineering and Applied Science

#### Splitting the locus into two

- Requires creating an isolation barrier  $\geq$

- Requires taking into account DC buses on  $\geq$ both sides

- Requires deciding how to size the LV and  $\geq$ HV modules in terms of voltage, power, cost, conversion function, flexibility and complexity

- The sizing of the isolation transformer is also  $\geq$ a key factor on the overall system

#### 300W Iso power locus

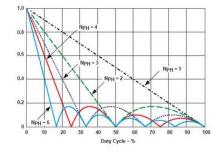

# Interleaving - Why interleaving?

Handling uncertainty in the

specifications

Power modules are designed for a restricted number of operation points

- A broader range of operation points requires finding a technique to ease the stress on the input/output filters

- Interleaving is the technique used by us to reach this goal

- But what is the right number of legs?

- What are the trade-offs that interleaving introduces?

Low side capacitor normalized current stress mode (2)

Two-leg synchronous buck interleaving (1)

COLUMBIA | ENGINEERING

High side capacitor normalized current stress buck mode (2)

(1)How to design a simple two-phase current sharing synchronous buck regulator

(2) Power Tips: When to choose multiphase

# Open Digital Power

## Looking at the possibilities

- Cases : 1 to 4 legs

- Evaluation: module level

|    | Digital power feasibility |                       |                             | Control c    | omplexity       | Topological merits |                  | Hardware<br>complexity |              | Topological flexibility |              | Modul<br>e<br>score |              |   |

|----|---------------------------|-----------------------|-----------------------------|--------------|-----------------|--------------------|------------------|------------------------|--------------|-------------------------|--------------|---------------------|--------------|---|

| #L | Digital<br>Power Soc      | Hwd<br>Ctrl V<br>mode | Hwd<br>Ctrl<br>Curr<br>mode | Mod.<br>Sync | Neutral<br>Ctrl | Isolat.<br>Mod     | Interlea<br>ving | Curr.<br>balanc.       | #<br>sensors | #<br>drivers            | # mod<br>1AC | # mod<br>3AC        | Leg<br>Usage |   |

| 1  | ++                        | ++                    | ++                          | -            | +               | DAHB               |                  | ++                     | 4 (++)       | 1 (++)                  | 2 ()         | 3()                 | ++           | 8 |

| 2  | +                         | +                     | +                           | +            | +               | DAB                | +                | -                      | 6 (+)        | 2 (+)                   | 1(++)        | 3()                 | ++           | 9 |

| 3  | +                         | +                     | -                           | ++           | -               | n/a                | ++               | -                      | 8 (-)        | 3 (-)                   | 1(++)        | 1(++)               | -            | 3 |

| 4  | -                         | -                     | -                           | ++           | ++              | DAB                | ++               | -                      | 10 ()        | 4 ()                    | 1(++)        | 1(++)               | +            | 3 |

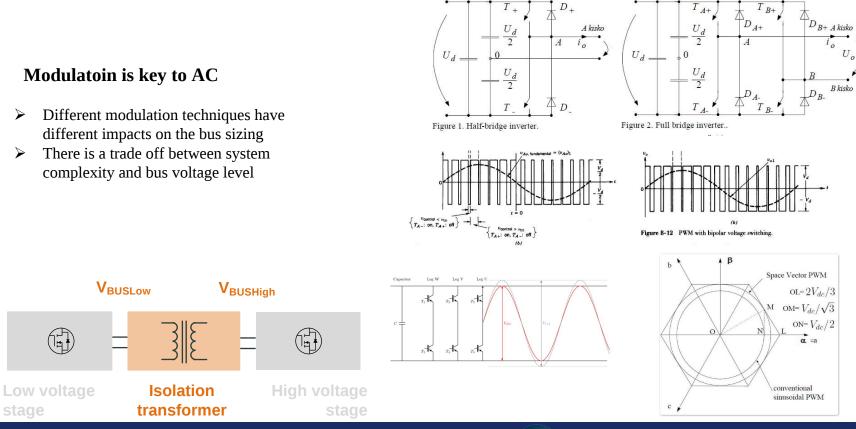

# DC Buses - Modulation impact oe DC Bus

$\geq$

$\geq$

COLUMBIA | ENGINEERING The Fu Foundation School of Engineering and Applied Science

#### Going up and coming back down

- Three phase topology are theoretically covering all the possible functions

- A three phase three leg AC inverter requires a V<sub>PEAK</sub> fo around 730V, meaning MOSFETs of 1200V lowering the efficiency of the high stage

- The isolation transformer is operated by a DAB or DAHB

- It must operate as closely as possible to its natural winding ratio.

# Constraints for the sizing of the Power Hardware

COLUMBIA | ENGINEERING The Fu Foundation School of Engineering and Applied Science

The Fu Foundation School of Engineering and Applied Science

# On the assembly level

- Cases : 1 to 4 legs  $\geq$

- Evaluation: assembly level  $\geq$

Gate Driver

|          | Relaxing Hw constraints                     |                      |                     |                     |                                                   |                      |                      |

|----------|---------------------------------------------|----------------------|---------------------|---------------------|---------------------------------------------------|----------------------|----------------------|

| # Legs   | High Side<br>Voltage<br>stress<br>reduction | Transformer<br>ratio | #modules<br>for 1AC | #modules<br>for 3AC | #modules<br>for isopower<br>/ stress<br>reduction | Unused leg<br>in 1AC | Mix & match<br>score |

| 1+DAHB+1 | +                                           | +                    | 4 (+ )              | 5 (-)               | 18 ()                                             | 0 (++)               | 2                    |

| 2+DAB+2  | ++                                          | +                    | 3 (++)              | 4 (+)               | 9 (-)                                             | 1 ()                 | 3                    |

| 3+DAB+3  |                                             | -                    | 3 (++)              | 3 (++)              | 3 (++)                                            | 1 ()                 | 1                    |

| 4+DAB+4  |                                             | -                    | 3 (++)              | 3( ++)              | 3 (++)                                            | 0 (++)               | 5                    |

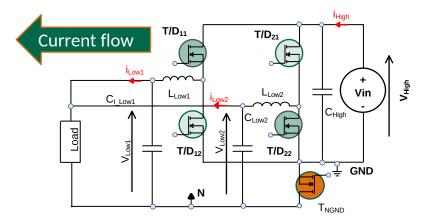

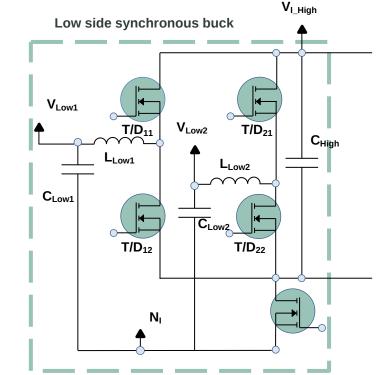

# Our Power Hardware Solution - 5 switches dual synchronous buck

COLUMBIA | ENGINEERING The Fu Foundation School of Engineering and Applied Science

| Variable                   | State                                  |

|----------------------------|----------------------------------------|

| T <sub>NGND</sub>          | ON                                     |

| Function                   | Buck                                   |

| $\mathbf{V}_{\mathrm{IN}}$ | $36V_{\text{DC}}$ to $48V_{\text{DC}}$ |

| V <sub>OUT</sub>           | $10V_{\text{DC}}$ to $14V_{\text{DC}}$ |

| Typical<br>Application     | Solar MPPT battery<br>charger          |

| Variable               | State                                  |

|------------------------|----------------------------------------|

| T <sub>NGND</sub>      | ON                                     |

| Function               | Boost                                  |

| $V_{\rm IN}$           | $24V_{DC}$                             |

| V <sub>OUT</sub>       | $48V_{\text{DC}}$ to $54V_{\text{DC}}$ |

| Typical<br>Application | Fuel cell Battery charger              |

# 5 switches dual synchronous buck - DC-DC independent mode operation

COLUMBIA The Fu Foundation School of

Engineering

The Fu Foundation School of Engineering and Applied Science

| Variable               | State                       |

|------------------------|-----------------------------|

| T <sub>NGND</sub>      | ON                          |

| Function               | Leg 1 Battery<br>Leg 2 Buck |

| $V_{\text{Source}}$    | $48V_{DC}$                  |

| $V_{\text{Battery}}$   | $24V_{DC}$                  |

| $V_2$                  | 12V <sub>DC</sub>           |

| Typical<br>Application | Solar Home system           |

| Variable                     | State                                |

|------------------------------|--------------------------------------|

| T <sub>NGND</sub>            | ON                                   |

| Function                     | Leg 1 Battery<br>Leg 2 Battery       |

| $\mathbf{V}_{\mathrm{High}}$ | Floating $V_{\text{DC}}$             |

| $V_1$                        | $24V_{DC}$                           |

| $V_2$                        | 12V <sub>DC</sub>                    |

| Typical<br>Application       | Peer-to-peer micro-<br>grid transfer |

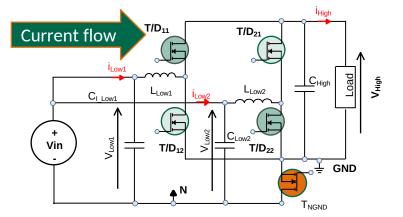

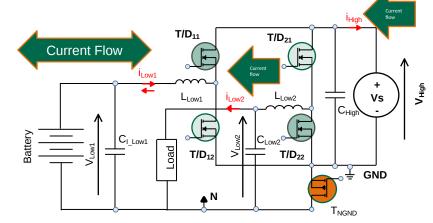

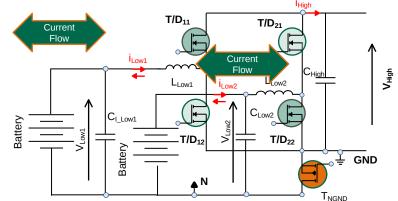

#### AAS CNRS 5 switches dual synchronous buck - DC-AC mode operation Open Digital Power Phase R Phase S **Current Flow** Phase T **İ<sub>High</sub>** Hiah Current Flow T/D<sub>11</sub> T/D<sub>11</sub> T/D<sub>21</sub> T/D<sub>21</sub> **Current Flow Current Flow** Low1 ILOW1 V <sub>High</sub> L<sub>Low1</sub> Vin L<sub>Low2</sub> Vin L<sub>Low2</sub> L<sub>Low1</sub> Low2 Low2 ۱ C<sub>High</sub> CHigh Λ Low2 Load Vour $V_{\mathsf{L}^{\mathsf{OW1}}}$ V<sub>Low1</sub> T/D12 T/D<sub>22</sub> Vour T/D<sub>12</sub> T/D<sub>22</sub> CI LOW1 CI LOW1 C<sub>Low2</sub> GND 🗄 GND Ν T<sub>NGND</sub> TNGND Variable Variable State State OFF T<sub>NGND</sub> T<sub>NGND</sub> OFF 3 phase Buck Inverter Function Function **Buck** Inverter $V_{IN}$ $110V_{DC}$ $V_{\text{IN}}$ $68V_{DC}$ 48.sin(wt) Vout 48.sin(wt) V<sub>OUT</sub> $48.\sin(wt+2\pi/3)$

Typical Application

Single phase AC inverter

Typical Application 48V

**CNrS**

48V motor control

COLUMBIA | ENGINEERING The Fu Foundation School of Engineering and Applied Science

48.sin(wt- $2\pi/3$ )

# 5 switches dual synchronous buck - Operation modes overview

| Convers<br>ion | Functi<br>on             | Vin                                          | Vout                   | Р   | Vmax                         | Use<br>Case                         |

|----------------|--------------------------|----------------------------------------------|------------------------|-----|------------------------------|-------------------------------------|

|                | Buck<br>interleav<br>ed  | $\mathrm{V}_{\mathrm{HIGH}}$                 | V <sub>LOW1/2</sub>    | 300 | 0.9<br>V <sub>HIGH</sub>     | Battery                             |

| DC-<br>DC      | Boost<br>interleav<br>ed | V <sub>LOW1/2</sub>                          | $V_{\rm HIGH}$         | 300 | $4*V_{LOW}$                  | Battery                             |

|                | Buck-<br>Boost           | V <sub>LOW1</sub><br>OR<br>V <sub>LOW2</sub> | $V_{LOW2} OR V_{LOW1}$ | 150 | 0.9*4*<br>V <sub>LOW</sub>   | Battery<br>to<br>Battery            |

|                | 1 phase                  | $\mathrm{V}_{\mathrm{HIGH}}$                 | V <sub>LOW1/2</sub>    | 300 | $V_{\rm HIGH}$               | Single<br>phase<br>motor<br>control |

| DC-<br>AC      | 2 phase -<br>2 boards    | $\mathrm{V}_{\mathrm{HIGH}}$                 | V <sub>LOW1/2</sub>    | 600 | $\mathrm{V}_{\mathrm{HIGH}}$ | Stepper<br>motor<br>control         |

|                | 3 phase -<br>3 boards    | $\mathbf{V}_{\mathrm{HIGH}}$                 | V <sub>LOW1/2</sub>    | 900 | V <sub>HIGH</sub> /2         | Brushle<br>ss<br>motor<br>control   |

COLUMBIA | ENGINEERING The Fu Foundation School of Engineering and Applied Science

# Software Defined Digital Hardware Design

TRANSCENDING DISCIPLINES, TRANSFORMING LIVES

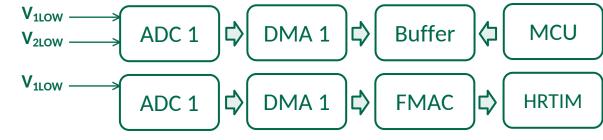

# **Digital Hardware - ADC Peripheral Constraints**

## > Reprogrammable ADC peripherals

- ADC mode of operation depends on the control method

- Flexibility in terms of data and control

- > Need to accelerate calculations

# > Multi-mode data acquisition

- Measurement scheme depends on control objectives of the application

- Application-level control may need intricate data measurements

- > Need for flexible channel allocation

Synchronous measurements for accurate power measures

Fast measurement for accelerated control

$V_{1LOW}$  .

ADC 1

#### Slow measurements for Telemetry

COLUMBIA | ENGINEERING The Fu Foundation School of Engineering and Applied Science

#### Reprogrammable HRTimer

- PWM depends on the power conversion function

- HRTimer must connect with other peripherals and provide triggers

- HRTimer must be able to ensure either Voltage or Current mode controls

- HRTimer must synchronize legs for interleaving and/or AC control

- The bandwidth of the HRTimer must be multiple orders of magnitude higher than the switching frequency

#### > Safety First

- HRTimers must be able to handle safety as well

- Current peak detection or other event driven shutdown must be provided via analog means

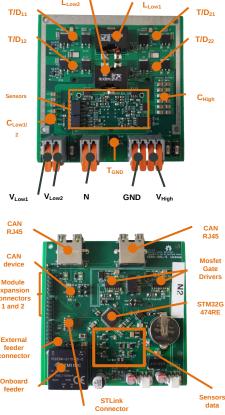

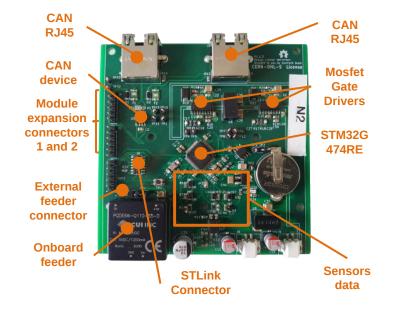

## Digital Hardware - Chosen Power SoC

| Peripheral | Details                                              |

|------------|------------------------------------------------------|

| HRTimer    | 13000 points at 200kHz                               |

| 2 ADCs     | Reassignable ADC<br>channels for flexible<br>control |

| 2 DMAs     | Flexible data handling                               |

| FMAC       | Filter for accelerated control calculations          |

| CORDIC     | Accelerated trigonometric functions                  |

| FPU        | Fast software math functions                         |

| Peripheral               | Details                                               |

|--------------------------|-------------------------------------------------------|

| Measurements             | $V_{Low1/2}$ , $i_{Low1/2}$ , $V_{High}$ , $i_{High}$ |

| CAN-based communication  | 2 RJ45 connectors to create daisy-chain CAN           |

| Isolated gate<br>drivers | PWM to power stage<br>driver                          |

| Expansion<br>connector 1 | USART, Rotary Encoder,<br>GPIOs                       |

| Expansion<br>connector 2 | SD Card module, Rotary<br>Encoder, GPIOs              |

| STLink Connector         | Programming and debugging                             |

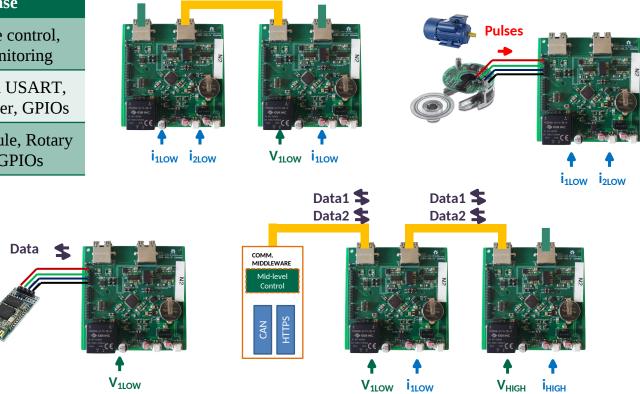

# Digital Hardware - Low-level communication bus use cases

COLUMBIA | ENGINEERING The Fu Foundation School of Engineering and Applied Science

| Function                          | Use case                                      | ← i <sub>LOW</sub>                                                      |

|-----------------------------------|-----------------------------------------------|-------------------------------------------------------------------------|

| CAN-Based communication           | Master-slave control,<br>System monitoring    |                                                                         |

| Expansion<br>connector 1          | Bluetooth via USART,<br>Rotary Encoder, GPIOs |                                                                         |

| Expansion<br>connector 2          | SD Card module, Rotary<br>Encoder, GPIOs      | i <sub>1LOW</sub> i <sub>2LOW</sub> V <sub>1LOW</sub> i <sub>1LOW</sub> |

| CURRENT<br>VOLTAGE<br>PWM<br>REF. | OTHER<br>DATA<br>MOD<br>Data                  | Data1<br>Data2                                                          |

# The interconnection and Application layers

TRANSCENDING DISCIPLINES, TRANSFORMING LIVES

# Zephyr Based SDPE Physical Layer

COLUMBIA | ENGINEERING

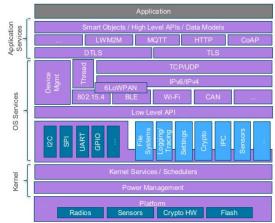

#### Leveraging an RTOS for P.E.

- Abstracting the hardware

- Creating drivers for the peripherals

#### **Communication Middleware**

- Low-level communication Bus

- Standardizing communication protocols

- A dedicated hardware

- > RTOS have stacks and natively implement abstraction from hardware

- Out-of-the-box IoT compatible communication stack

- > Driver-oriented programming and abstraction

- Low-level API abstraction possible

- Using RTOS modules to create Power-Electronics oriented abstraction

- Data Acquisition and handling also abstracted for easier control implementation

Open Digital Power

- > Open source real-time OS

- Vibrant Community participation

- Safety and Security built-in

- Cross-architecture with broad SoC and development board support

- Vendor Neutral Governance

- Permissively licensed Apache 2.0

- Complete, fully integrated, highly configurable, modular for flexibility

COLUMBIA | ENGINEERING The Fu Foundation School of Engineering and Applied Science

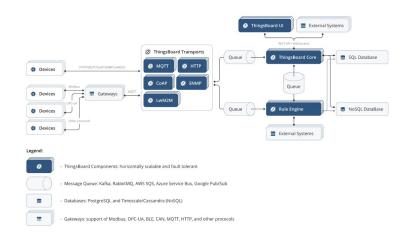

- Multi-purpose communication

- Low level synchronization

- High level data aggregation

- Data parsing and bi-directional flow

- Uplink data harvesting

- Downlink parameter update

- > Data treatment

- > Data aggregation and system diagnosis

- Flexible control architectures

- > Decentralized

- Hierarchical

- ➢ Centralized

COLUMBIA | ENGINEERING The Fu Foundation School of Engineering and Applied Science

ThingSet

- > Target agnostic data parsing system

- Possiblity of creating data structures

ESP32

- Low-cost and ubiquitous IoT solution

- Separated cores allow for data pre-treatment

Dedicated board

Open-Source ESP32 based solution compatible with CAN

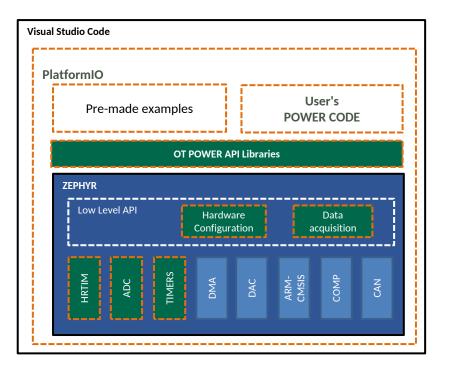

# Zephyr Based SDPE Physical Layer

## Leveraging an RTOS for P.E.

- Packaging software

- Leveraging abstraction

#### **Communication System**

Flexible frontend

COLUMBIA | ENGINEERING The Fu Foundation School of Engineering and Applied Science

The Fu Foundation School of Engineering and Applied Science

- VSCode outer envelope

- PlatformIO based usage  $\geq$

- Gitlab hosted Libraries

- Automatic handling of other 3rd party modules  $\geq$

- Low-Level API for abstracting the drivers  $\triangleright$

- In-House HRTIM driver  $\geq$

- Rewritten ADC driver for peripheral-to-peripheral connection  $\geq$

- In-house Timer module

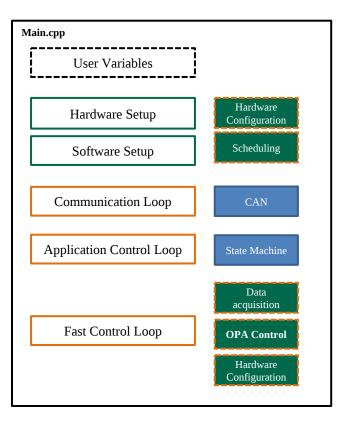

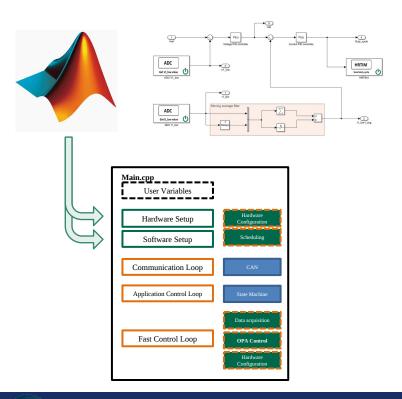

# Software Packaging and Ergonomics - Coding with C

- Single main code for "Arduino-like" experience

- Setup and Loop ergonomics

- Hardware and Software Setup

- Communication, Application and Fast Control Loop

**Open Digital Powe**

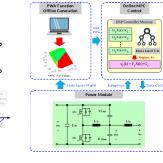

#### Software Packaging and Ergonomics - Coding with Matlab

COLUMBIA | ENGINEE The Fu Foundation School of Engineering and Ap

The Fu Foundation School of Engineering and App

- Matlab blocks can be generated to call the  $\geq$ abstraction layer modules

- $\geq$ Application code is automatically generated

- $\geq$ The code is automatically put in the folder tree

- $\geq$ The code is called from the application loop or the fast control loop

COLUMBIA | ENGINEERING The Fu Foundation School of Engineering and Applied Science

- Flexibility in the communication protocols

- Expansion with multiple devices

- > Data aggregation

- > Data treatment

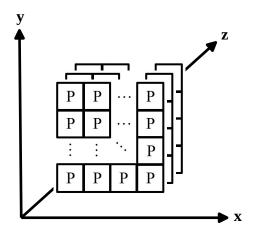

## **Design Case of Multi-Level Converter**

**Matthias Preindl**

## Motivation

- HVDC, automotive

- Improved power quality, lower switching voltages, reduction in EMI

#### At the cost of:

- complexity

- component quantities

#### Goal:

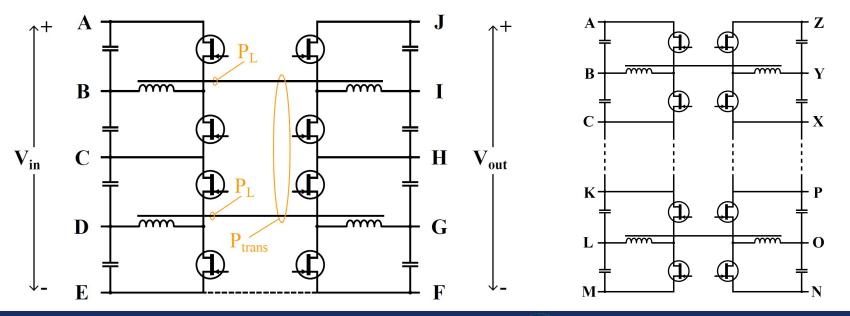

- Easily expandable and modular approach to power electronic conversion

- Linear component quantity and circuit complexity scaling with respect to number of levels

**a** new power electronics environment

Increase x ➡ increased current (parallel connection) Increase y ➡ increased voltage (series connection) Increase z ➡ increased number of outputs (multiphase connection)

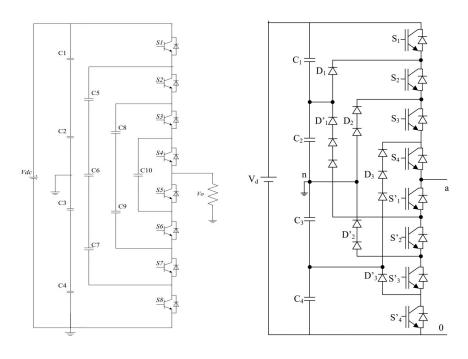

Flying capacitor topology [1]

Diode clamped topology [2]

Typical multilevel topologies do not fit this goal

- circuit connections change as number of levels increases

- component quantities do not scale linearly

- switching state control must be applied to the entire converter

# The MMC has linear component quantity and circuit complexity scaling

CNrs

- switching state control must be applied to the entire converter

- Challenging to maintain capacitor voltage balance in steady state

► DC/DC implementation difficult

🚼 Columbia | Engin

The Fu Foundation School of Engineering and A

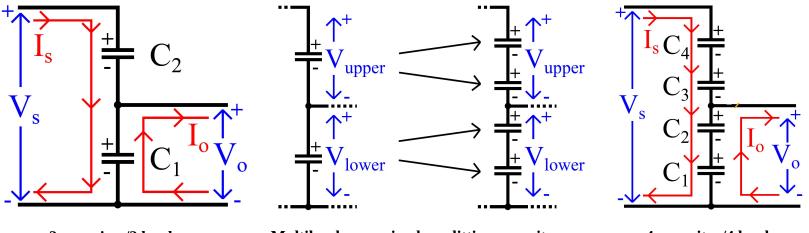

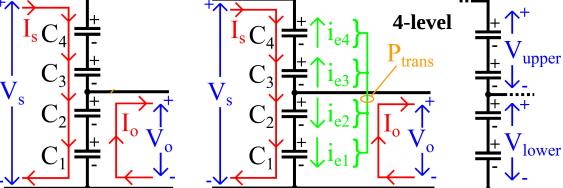

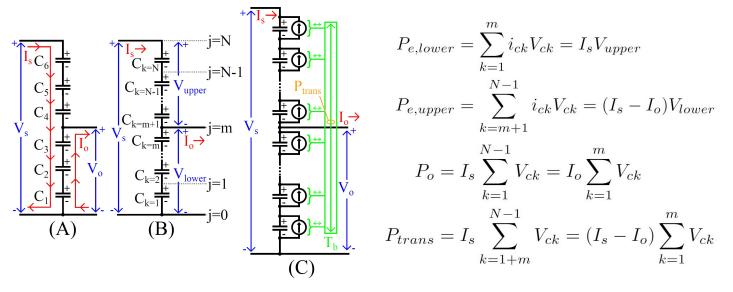

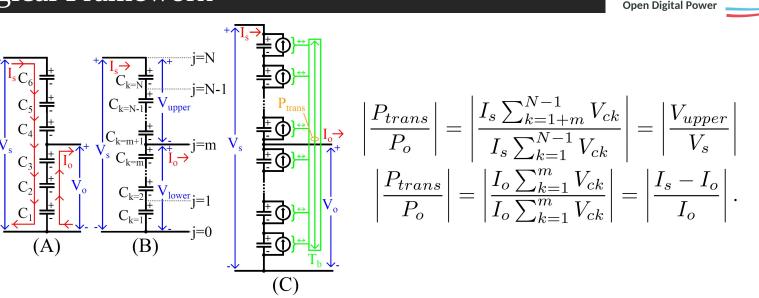

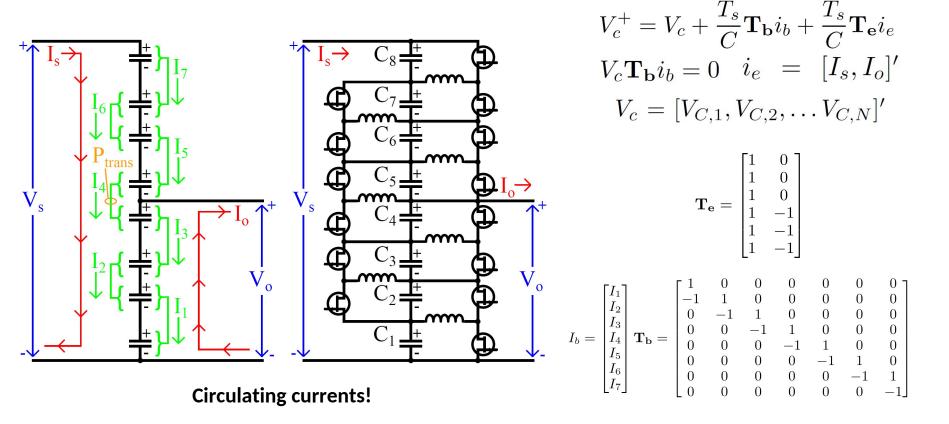

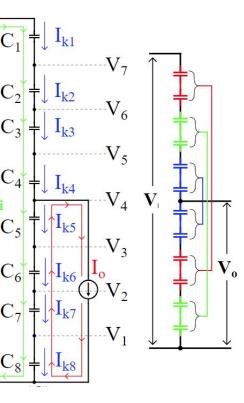

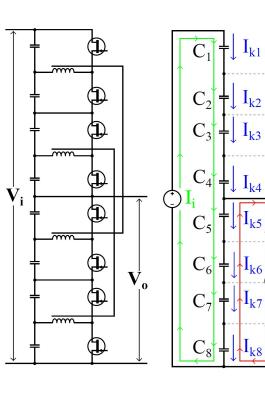

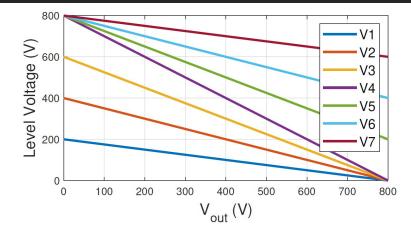

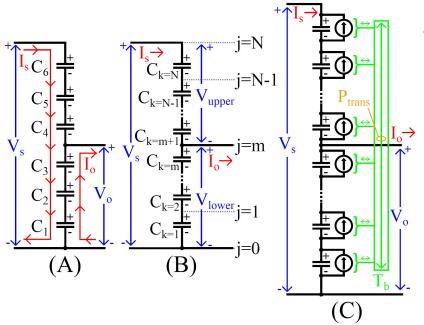

- We can build a multilevel topology around a center stack of capacitors

- Where each capacitor represents a voltage level

- And the input voltage is split along the series combination of these capacitors

2 capacitor/2 level

Multilevel expansion by splitting capacitors

CNrs

4 capacitor/4 level

This topology, as it is shown above, does not maintain capacitor voltage in steady state - For positive  $I_s$  and  $I_o$ , upper voltage will increase and lower voltage will decrease

🚼 Columbia | Enginei

The Fu Foundation School of Engineering and App

For capacitor voltage balance in steady state, all capacitor currents must equal zero:

- upper capacitors:  $I_{C,upper} = I_s$

- upper capacitors:  $I_{C,lower} = I_s - I_o$

These capacitor currents can be interpreted as excess powers within each set capacitors:

- set of upper capacitors: P<sub>e,upper</sub> = (V<sub>in</sub>-V<sub>o</sub>)I<sub>i</sub>

- set of upper capacitors:  $P_{e,lower} = V_o(I_i - I_o)$

**Given**  $P_{in} = P_{out}$ , it can be found that:  $P_{e,upper} = -P_{e,lower}$

Transferring excess powers between the upper set of capacitors and lower set of capacitors will result in a total cancellation of all excess powers

#### The excess powers do not depend on the number of levels

$$P_{e,C1} = V_{C1}(I_s - I_o)$$

$$P_{e,lower} = V_{lower}(I_s - I_o)$$

$$P_{e,C2} = V_{C2}I_s$$

$$P_{e,upper} = V_{upper}I_s$$

$$\begin{split} P_{e,C1} + P_{e,C2} &= (V_{C1} + V_{C2})(I_s - I_o) \\ P_{e,lower} &= V_{lower}(I_s - I_o) \\ P_{e,C3} + P_{e,C4} &= (V_{C3} + V_{C4})I_s \\ P_{e,upper} &= V_{upper}I_s \end{split}$$

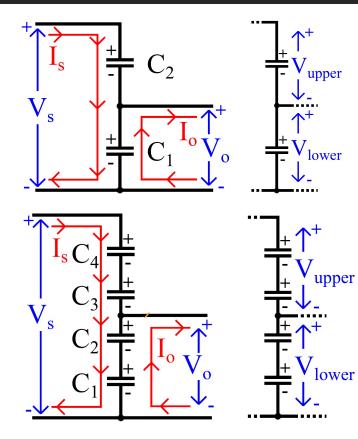

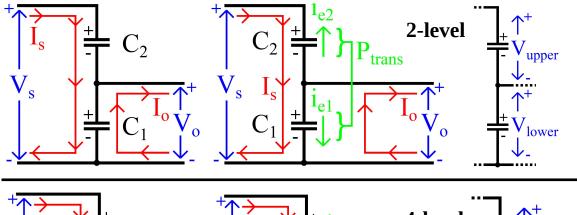

Because the excess powers do not depend on the number of levels:

- the amount of power  $P_{trans}$  that needs to be transferred between the upper and lower sets of capacitors does not change with the number of levels

- linear component stress scaling with number of levels

The excess powers are always less than the output power. This means that:

- the internal power transfer P<sub>trans</sub> required to maintain voltage balance in steady state is less than

CNrs

🚼 Columbia | Engin

The Fu Foundation School of Engineering and

$P_{o}$

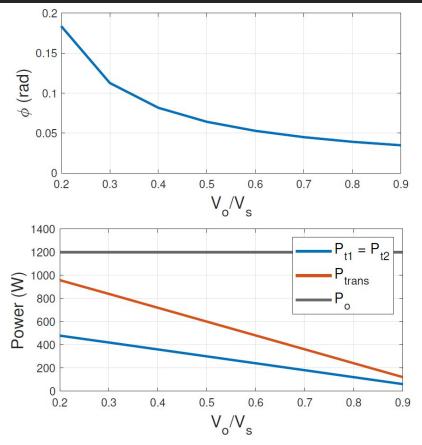

- P<sub>trans</sub> is a function of the conversion ratio

- This converter topology internally converts less power than it outputs

- a "differential" power converter

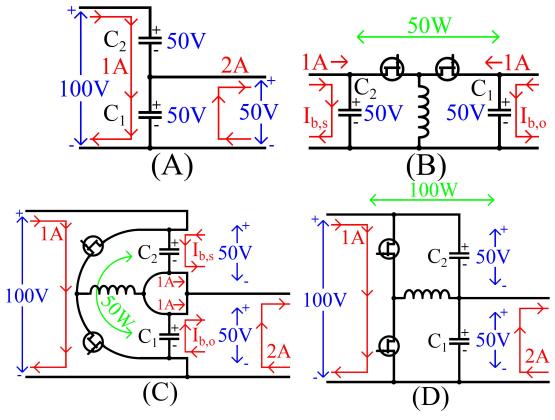

## Topology implementation (Sanity check)

🚼 Columbia | Engin

The Fu Foundation School of Engineering and Apr

We can use this topological framework to develop a hypothetical 100W buck converter from a 50W buck/boost converter

a) baseline 2-level converter made using the proposed topological framework

b) 50W buck/boost converter used to transfer power between upper and lower capacitors

c) connection of the 50W buck/boost converter

d) resulting 100W buck converter

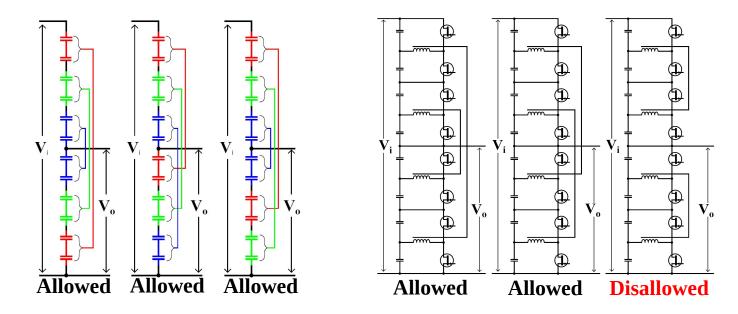

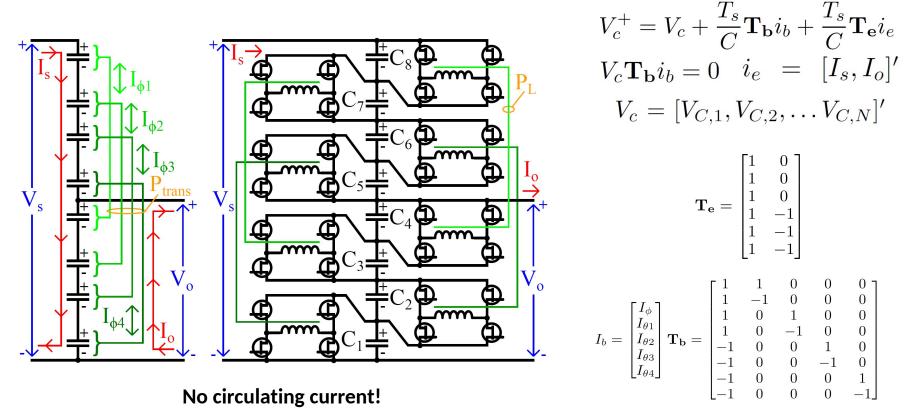

## Topology implementation – allowable links

There are allowable power transfer links – power must have a path to move from the upper set of capacitors to the lower set of capacitors

Fu Foundation School of Eng

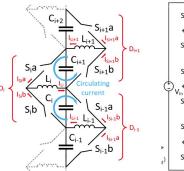

#### We can then develop a mathematical framework to accompany the topological framework

State space formulation :

$$V_c^+ = V_c + \frac{T_s}{C} \mathbf{T}_{\mathbf{b}} i_b + \frac{T_s}{C} \mathbf{T}_{\mathbf{e}} i_e$$

With constraint of:

$$V_c \mathbf{T}_{\mathbf{b}} i_b = 0$$

- represents how the internal capacitive balancing currents cannot add power into the system

Where:

- $V_c$  is vector of capacitor voltages  $V_c = [V_{C,1}, V_{C,2}, \dots, V_{C,N}]'$

- C is capacitance

- Ts is controller sample interval

- $i_e$  is a vector that contains the external currents  $I_i$  and  $I_o$   $i_e = [I_s, I_o]'$

- $-T_{e}$  is a connectivity matrix that represents which capacitors are affected by the external currents  $i_{e}$

CNrs

- $-T_{\rm b}$  is a connectivity matrix that represents the capacitive power transfer links

- -ib is a vector that denotes the amount of power shared across each link

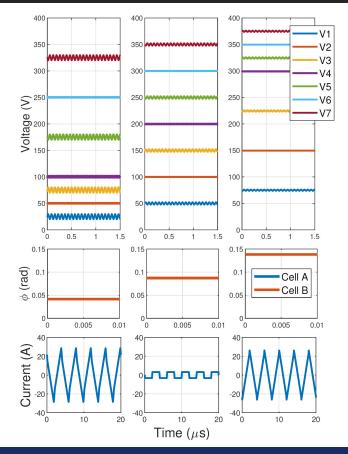

### Topology Implementation – Half Bridges

🔂 Columbia | Engineering

The Fu Foundation School of Engineering and Applied Science

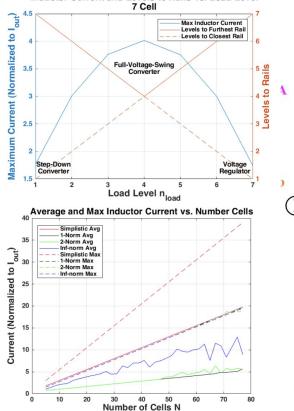

Topology Implementation – Half Bridges – Circulating

Inductor Current and Levels to Rails vs. Load Level

- $\begin{array}{c} & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & &$

- This is because the capacitors below the output node need current to support their voltage

This current comes from the upper capacitors, cascading through each module

- nonlinear component stresses with number of level

🚰 Columbia | Engineering

The Fu Foundation School of Engineering and Applied Science

## Topology Implementation – Dual Active Half Bridges

**123** | Transcending Disciplines, Transforming Lives, Educating Leaders

🚼 Columbia |

Engin

The Fu Foundation School of Engineering and Applied Science

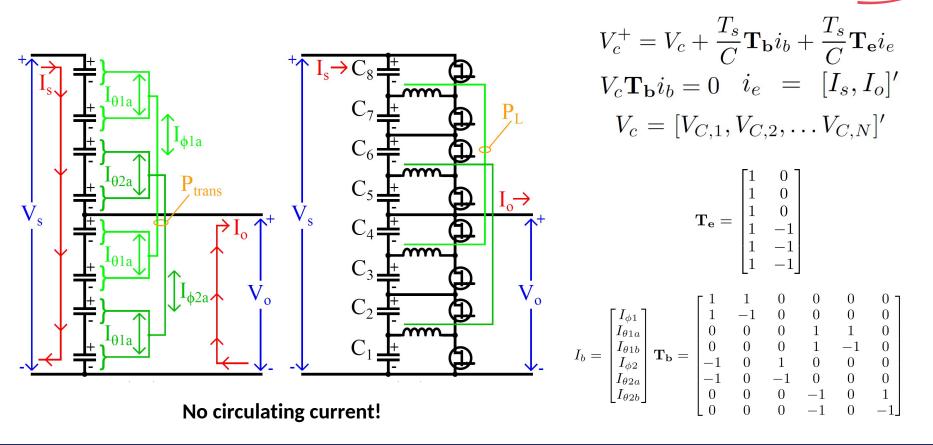

## Topology Implementation – Dual Active Half Bridges – Results

High-Fidelity Simulation transient results - C = 24uF - L = 2.5uF  $- f_{sw} = 200kHz$  - n = 1 - load = 100R $-V_{in} = 400V$

- all DAHBs operated with same parameters

- Duty cycle set to 0.5

$V_4$

$V_3$

$V_1$

- phase difference **φ** set to the same for both HBs

- PI control used to find required  $\phi$  to achieve desired V<sub>o</sub>

## Topology Implementation – Dual Active Half Bridges – Results

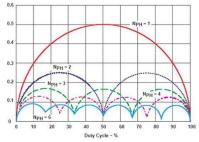

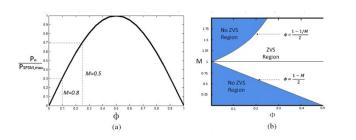

#### **High-fidelity simulation average results**

- same parameters as previous sweep

- Vin = 800V

- Constant output power over  $V_{\mbox{\scriptsize out}}$  sweep

- ideal voltage splitting maintained over the sweep

- $P_{\text{trans}}$  always less than  $P_{\text{o}}$

## Topology Implementation – Dual Active Full Bridges

🛟 Columbia | Enginee

The Fu Foundation School of Engineering and Applied Science

## Topology implementation – edge cases

Open Digital Power

🏶 Columbia | Engi

The Fu Foundation School of Engineering and Applied Science

- It is also allowable to mix and match capacitive power sharing techniques

- Any combination of methods can be used as long as all upper capacitor and all lower capacitors have a path to transfer power

- Isolated configurations can also be implemented

🚼 Columbia | Enginei

The Fu Foundation School of Engineering and App

#### - This multilevel topological framework is:

- easily expandable (more capacitors = more levels)

- has linear component quantity scaling with levels

- can have linear component stresses scalingwith levels (DAHB, DAFB)

- is fully balanced

- can operate bidirectionally

- has isolated and non-isolated variants

- can be used with advanced control methods

- can also be controlled with a single parameter ( $\varphi)$  to achieve the full output voltage range

## Conclusion

Matthias Preindl, Luiz Villa

TRANSCENDING DISCIPLINES, TRANSFORMING LIVES

🔂 Columbia | Engineering

The Fu Foundation School of Engineering and Applied Science

#### **Software-Defined Power Electronics:**

- ≻ Techniques: MPC, VFCSS.

- > Applications: Grid, motor, battery, solar, etc.

- > Hardware Optimization: High efficiency.

- ▶ Non-Isolated Topology: Low cost.

- > Multi-Level Converters: High voltage, low ripple.

COLUMBIA | ENGINEERING The Fu Foundation School of Engineering and Applied Science

The Fu Foundation School of Engineering and Applied Science

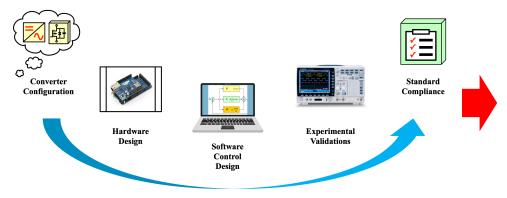

#### **Software-Defined Power Electronics:**

► Generalized design procedures.

- $\succ$  Reconfigurable architecture.

- $\succ$  Wide application interfaces.

- $\triangleright$  Redundancy with self-healing.

#### Generalized design procedures:

- Save repetitive design procedures.

- ≻ No hardware component redesign.

- ≻No software algorithm redesign.

CN

**Open Digital Power**

COLUMBIA | ENGINEERING The Fu Foundation School of Engineering and Applied Science

COLUMBIA | ENGINEERING The Fu Foundation School of Engineering and Applied Science

#### **Reconfigurable Architecture :**

- ➢ Feasible for various applications.

- ≻Extensible control functions.

- ≻ Random number of power modules.

COLUMBIA | ENGINEERING The Fu Foundation School of Engineering and Applied Science

#### **Redundancy with self-healing :**

- ≻ Auxiliary modules for redundancy.

- ≻ Timely monitoring power failure.

- Substitute for failed modules.

🎛 Columbia | Engineering

The Fu Foundation School of Engineering and Applied Science

# Choosing the starting point is really not easy

▶ Which Digital Power SoC ?

➤ Which Power Hardware ?

#### Interfaces are central

- Power SoC interfaces

- Software modules interfaces

- Communication protocols

# Everything is possible, but not always available

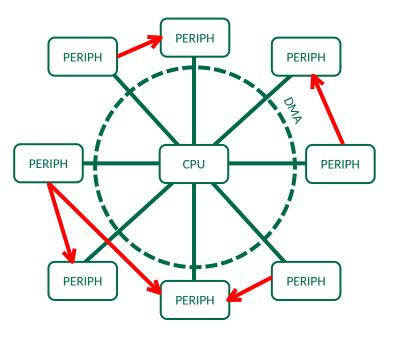

#### Conclusions - The Star and the Circle

- Power electronics have a very niche need of combining CPU flexibility and hardware acceleration

- Manufactures have solutions, but they require bare-metal coding

- ➢ Interfaces needed by SDPE

- > Peripheral-to-peripheral via DMA

- > Peripheral interconnection matrix

CNrs

COLUMBIA | ENGINEERING The Fu Foundation School of Engineering and Applied Science

- > The problem is complex and the market fragmented

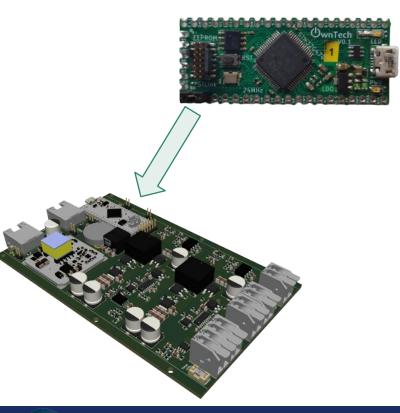

- > It seems important to separate the brains from the muscles

- Dedicated board for the SoC

- Feather footprintLeverages highly specialized peripherals

- Dedicated board for power

- 160mmx100mm footprint (Euroboard)

Or in industrial 19" rack..

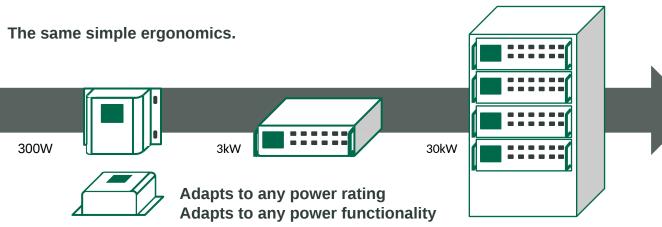

#### A standard module

- 300W per module

- Compact 100x100mm

form factor

- Around 100€

As a stand alone module..

#### Conclusions - Great impact is possible !

COLUMBIA | ENGINEERING The Fu Foundation School of Engineering and Applied Science