# TCAD modeling and simulation of self-limiting oxide growth and boron segregation during vertical silicon nanowire processing

Chiara Rossi, Jonas Müller, Peter Pichler, Pawel Piotr Michalowski, Guilhem Larrieu

#### ▶ To cite this version:

Chiara Rossi, Jonas Müller, Peter Pichler, Pawel Piotr Michalowski, Guilhem Larrieu. TCAD modeling and simulation of self-limiting oxide growth and boron segregation during vertical silicon nanowire processing. Materials Science in Semiconductor Processing, 2024, 174, pp.108217. 10.1016/j.mssp.2024.108217. hal-04639888

### HAL Id: hal-04639888 https://laas.hal.science/hal-04639888v1

Submitted on 9 Jul 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

ELSEVIER

Contents lists available at ScienceDirect

#### Materials Science in Semiconductor Processing

journal homepage: www.elsevier.com/locate/mssp

Full length article

### TCAD modeling and simulation of self-limiting oxide growth and boron segregation during vertical silicon nanowire processing

Chiara Rossi a,\*, Jonas Müller b, Peter Pichler a, Paweł Piotr Michałowski c, Guilhem Larrieu b

- <sup>a</sup> Fraunhofer Institute for Integrated Systems and Device Technology IISB, Erlangen, Germany

- b LAAS-CNRS, Université de Toulouse, Toulouse, France

- <sup>c</sup> Łukasiewicz Research Network Institute of Microelectronics and Photonics, Warsaw, Poland

#### ARTICLE INFO

## Keywords: TCAD process simulations Self-limiting thermal oxidation Boron segregation Silicon nanowires Gate-all-around nanowire field-effect transistor (GAA-NW-FET)

#### ABSTRACT

Thermal oxidation is a key step for the fabrication of vertical gate-all-around nanowire field-effect transistors (GAA-NW-FETs). It is used after the etching of nanopillars from the silicon substrate to further thin the nanowire diameter, remove the etching damage and have good control of the geometry. It can also be used to grow a gate oxide. Thermal oxidation of silicon nanowires is a self-limiting process. Self-limiting effects, which are due to the mechanical stress in the structure, need to be accurately modeled to obtain predictive simulations of nanowire geometry, and so of the GAA-NW-FET channel dimensions, after thermal oxidation. Moreover, boron segregation during thermal oxidation into the growing oxide results in a considerable dopant loss from the nanowire. Correct modeling of such effects is also paramount for the investigation and simulation of the electrical characteristics of nanowire transistors, especially for p-type junctionless GAA-NW-FETs. In this work, we present a comparison of 2D and 3D TCAD process simulations of the oxidation of silicon nanowires with experimental data. Based on that, we suggest novel sets of calibrated parameters for stress-dependent oxidation, relevant particularly for nanowire diameters below 60 nm, and for boron segregation.

#### 1. Introduction

Gate-all-around nanowire field-effect transistors (GAA-NW-FETs) are very promising candidates to obtain better power-performance metrics for advanced technology nodes [1], and therefore to meet the requirements of the Power-Performance-Area-and-Cost scaling roadmap that replaced Moore's law. GAA-NW-FETs provide improved gate control and show excellent short-channel immunity [2]. Vertical GAA-NW-FETs permit enhanced integration due to their 3D layout configuration, overcoming physical limitations resulting from 2D layout, such as contact placements and interconnect routing congestion [3-5]. Vertical nanowires fabricated by a top-down approach yield high-density arrays with very good reproducibility and shape control (position, diameter and pitch), using techniques that can be easily integrated into standard CMOS processes [6]. The top-down fabrication of silicon nanowires is based on the highly anisotropic plasma etching of planar substrates to obtain nanopillars, followed by a sacrificial thermal oxidation. Sacrificial thermal oxidation is a key process for the fabrication of nanowires in electrical devices, as it allows to shrink down the diameter, with a good control of the nanowire dimensions, structural variations, and cylindrical shape [7], while simultaneously removing residual surface damage caused by the etching process [8].

Particularly in industrial environments, Technology Computer Aided Design (TCAD) methods are widely used to explore, model and optimize semiconductor fabrication processes and devices, as they reduce development times and cost and help to obtain optimal processes and devices [9]. Thermal oxidation, due to its important role in controlling the final nanowire diameter, is a crucial step in TCAD simulations of GAA-NW-FETs fabrication process and must be correctly modeled to allow a full exploitation of the predictive power of TCAD tools. The challenge lays therein that the oxidation of vertical silicon nanowires is a self-limiting process: oxide growth slows down with increasing time and decreasing size [10]. Self-limiting effects are due to the mechanical stress in the nanostructures [10,11], arising from the higher volume occupied by the formed silicon oxide with respect to the consumed silicon (volume expansion by 125% [12]). In particular, the stress normal to the silicon-silicon oxide interface (compressive to the growing new oxide) reduces the surface reaction rate, whereas the stress in the oxide, in particular the high compressive hydrostatic pressure in the vicinity of the interface, reduces the diffusivity of the oxidant [11,13]. Works in literature have addressed self-limiting oxidation for different oxidation temperatures and times and different nanostructure sizes. Some of them have reported that the oxidation

<sup>\*</sup> Correspondence to: DPIA, University of Udine, Udine, Italy. E-mail address: chiara.rossi@uniud.it (C. Rossi).

is limited by the surface reaction [7,14,15], others explained it by a reduced diffusivity of the oxidants [16–19]. Another peculiar aspect of nanowire oxidation is that the resulting silicon nanowires were reported to have a circular cross-section [7,12,13,20], despite the well-known orientation dependence of silicon oxidation [10,21]. The physical origin of the circular cross-section is still debated and various explanations have been proposed. Uematsu et al. [12] suggested that the rounded shape is mainly caused by the stress-induced reduction of the oxide viscosity, whereas other authors proposed that it is due to the edge effect [22,23], i.e. the larger oxidation energy barrier of Si–Si bonds at the edge of a surface.

Thermal oxidation of silicon deeply affects the doping distribution in the nanowire due to dopant segregation into the growing oxide and self-interstitial injection into the silicon, especially for p-type dopants [24,25]. This effect is more pronounced in 3D nanostructures with respect to bulk devices. In silicon nanowires, in fact, the injected self-interstitials cannot diffuse efficiently into the bulk, and this results in increased dopant diffusion and segregation loss. Moreover, the resupply of dopants in the nanowire from the bulk is limited by the elongated device geometry. Modeling the resulting doping distribution is paramount for understanding and optimizing the electrical properties of the devices, especially for junctionless GAA-NW-FETs, which are most commonly employed thanks to their reduced fabrication complexity [26]. Accordingly, like self-limited oxidation effects, boron segregation must be correctly modeled to allow predictive electrical simulations of the resulting device [27].

In this work, we present TCAD process simulations of the thermal oxidation of nanowires, including self-limiting effects, using Sentaurus Process of Synopsys [28], version U-2022.12. Simulation results, namely nanowire diameters and doping distributions, are compared to experimental results of structures fabricated at LAAS-CNRS and measured with scanning electron microscopy (SEM) and secondary ion mass spectrometry (SIMS) techniques, as described in Section 2. Simulations using Sentaurus Process with the default parameters provided in the *AdvancedCalibration U-2022.12* file [29] could not predict the final diameters of thin and thick nanowires at the same time sufficiently well and could not assess accurately enough the resulting boron concentration in the nanowires. The calibration work carried out to extend the validity of the model provided in Sentaurus Process in the *AdvancedCalibration U-2022.12* file [29], is presented in Section 3.

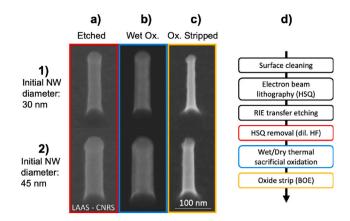

#### 2. Experimental results

The modeling work is based on experimental data obtained from the sacrificial oxidation of nanowires performed at LAAS-CNRS. The nanowires were fabricated by a top-down approach, employing 4-inch (1 0 0) silicon wafers. Two different types of p-doped wafers with either high or low resistivity, corresponding to a boron concentration of about  $10^{13}~\text{cm}^{-3}$  and  $3\cdot 10^{19}~\text{cm}^{-3}$  (3.7  $\cdot 10^{19}~\text{cm}^{-3}$  for wafer A and  $2.7 \cdot 10^{19} \text{ cm}^{-3}$  for wafer B), respectively, were used. The process flow for the nanowire fabrication (schematically summarized in Fig. 1.d) starts with the patterning of an array of circular nanopillars of negative resist by electron beam lithography [30,31]. The array is then transferred onto the silicon substrate by anisotropic reactive ion etching (RIE), obtaining vertical nanowires with a height of 210 nm and diameters in a range from 20 nm to 100 nm. The cleaned nanowires are then oxidized. Two different oxidation conditions were used: wet thermal oxidation at 850 °C for 5 min and dry thermal oxidation at 860 °C for 66 min. In both cases, the oxidant gas is added only during the set oxidation phases while the heat-up and cool-down occurs under nitrogen atmosphere. These two oxidation processes had been fine-tuned to yield the same oxide thickness on planar samples and resulted in similar oxide thicknesses on nanowires with comparable initial diameters. Fig. 1 reports SEM micrographs of nanowires with different initial diameters (30 nm in Fig. 1.1 and 45 nm in Fig. 1.2) after RIE (a), sacrificial wet oxidation (b) and oxide stripping (c). The

Fig. 1. (a) SEM micrographs of nanowires after RIE, with a diameters of 30 nm (1) and 45 nm (2). (b) SEM micrographs of nanowires after sacrificial wet oxidation. (c) SEM micrographs of nanowires after oxide stripping. (d) Scheme of the process flow for nanowire fabrication.

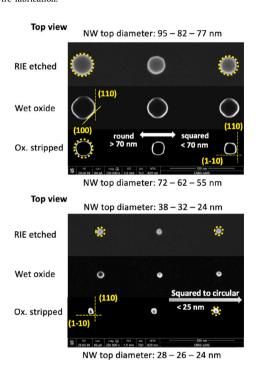

Fig. 2. SEM micrographs (top view) of selected nanowires after RIE, sacrificial wet oxidation and oxide stripping.

nanowires show a good geometrical uniformity in the mid-section and SEM measurements revealed an almost constant nanowire diameter along the height, except for the top and bottom part, as it can be seen in Fig. 1. Fig. 2 reports the SEM micrographs of the top view of selected nanowires during processing. It can be seen that initially round nanowires after RIE etching present a faceted oxide growth, indicating an enhanced oxidation rate in the < 110> direction. After removal of the oxide layer, large nanowires show a circular shape whereas nanowires with diameter between 70 nm and 30 nm have a square shape with visible facets corresponding to the (110) and (1-10) planes. Regarding the smallest nanowires (diameter < 30 nm), while these planes seem to be present in some cases, the shape becomes increasingly circular when the diameter decreases. However, it is not possible to formulate conclusive remarks about the size-dependence of the shape due to the overall small dimensions. It has to be noted that the top view SEM micrographs primarily present the circumference of the nanowire head formation, which exceeds the diameter of the main

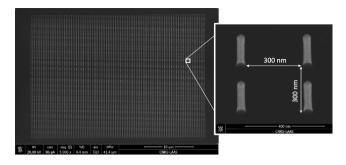

Fig. 3. SEM micrograph of an array of nanowire for SIMS measurements after wet thermal oxidation.

nanowire, as it can be seen in Fig. 1. It is thus possible that only the top part of the nanowire is *square* shaped whereas the mid and bottom-sections could vary to some degree from the observed shapes.

Extensive SEM measurements of the nanowire diameters (in the mid-section) have been performed for the entire size range of the fabricated structures. The measured final nanowire diameters, i.e. after sacrificial oxidation, as a function of the respective initial nanowire diameter, i.e. after RIE and before oxidation, will be shown below in Section 3.1.

The wet thermal oxidation was performed on both high-resistivity and low-resistivity wafers while dry thermal oxidation was only performed on low-resistivity wafers. As expected from literature [32,33], boron doping in the considered range, and for the considered oxidation temperatures, does not noticeably affect the oxidation rates. Accordingly, the two datasets for wet oxidation with the different doping concentrations were considered together without distinction for modeling.

To evaluate the boron segregation during oxidation, SIMS measurements of doping profiles were performed along the length of the nanowires after selected oxidation of samples fabricated from lowresistivity wafers. The SIMS approach used here was recently developed to overcome the limitations of standard SIMS techniques for doping measurements in 3D structures [34]. Large arrays of  $100 \times 100$ nanowires were fabricated as described above. For a complete assessment of boron segregation during all oxidation processes of the full GAA-NW-FET device fabrication, selected nanowires were further dry oxidized, after the first sacrificial wet oxidation (725 °C for 20 min, used for gate oxide growth), and characterized. An exemplary SEM micrograph of a full-scale nanowire array for SIMS measurements after wet thermal oxidation is shown in Fig. 3. Any oxide layer has been stripped before embedding the nanowires in an organic resist matrix, required for the SIMS measurements as described in [34], in order to measure the remaining dopant concentration in the nanowires. The measured boron concentrations along the nanowires will be shown below in Section 3.2.

#### 3. TCAD simulations and model calibration

#### 3.1. Nanowire dimensions and shape after oxidation

For the 2D and 3D simulation of the sacrificial oxidation of the nanowires, the continuum simulator of Sentaurus Process was used. Following the concept of Deal and Grove [35], the program considers the diffusion of oxidant species from the gas—oxide interface through the existing oxide to the oxide—silicon interface where they react with the silicon to form new oxide. In 1D, assuming a stationary flow of the oxidant species, the growth rate of the oxide layer is described by the Deal—Grove law:

$$\frac{dx_{ox}}{dt} = \frac{B}{2x_{ox} + A} \tag{1}$$

Eq. (1) has two limiting solutions. For short oxidation times, the oxide growth

$$x_{ox} \cong \frac{B}{A}(t+\tau) \tag{2}$$

proceeds linearly with time with the linear rate constant B/A.  $\tau$  corresponds to a shift in time to take an initial oxide thickness into account. For long times, the oxide growth

$$x_{ax}^2 \cong Bt$$

(3)

becomes parabolic with the parameter *B* being referred to as parabolic rate constant.

It can be shown that B is proportional to the diffusivity of the oxidant and B/A is practically proportional to the reaction rate of the oxidant species with the silicon atoms [35]. The parameters B and B/Aare temperature dependent and in Sentaurus Process are described by Arrhenius functions [28]. The pre-exponential factors of the Arrhenius functions of B and B/A, referred to as B0 and BA0, and the activation energies (BW and BAW) can be calibrated using experimental data. Several additional models are included in Sentaurus Process to model effects that are relevant particularly in 2D and 3D oxidation setups. The orientation dependence is accounted for by having three different reaction rates for different orientations ( $k_{(100)}$ ,  $k_{(110)}$  and  $k_{(111)}$ ). The model for stress-dependent oxidation couples the oxidant diffusivity and the reaction rate to the local stress field through the definition of activation volumes, namely  $V_D$  and  $V_k$ . The activation volume  $V_D$ is a bulk property defined in the oxide and controls the impact of the hydrodynamic stress on the oxidant diffusivity. The activation volume  $V_{k}$  is an interface property and controls the impact on the reaction rate of the normal stress at the reaction front [11]. Additional models for trap-dependent oxidation, doping dependent oxidation, etc. are also included but are not detailed here, as they will not be employed in this work.

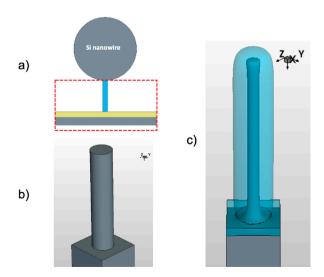

The initial structure in our simulations is a silicon nanowire, constructed in two fashions: as a 2D structure, i.e. a circular cross-section of a silicon nanowire as depicted in Fig. 4.a, or as a 3D structure, i.e. a cylindrical vertical silicon nanowire on a silicon substrate, as depicted in Fig. 4.b. For the 2D case, the structural support, in the red dashed box, is needed due to the limitations in the boundary conditions of Sentaurus Process: a planar substrate (a wafer) is always needed, a self-standing circular structure cannot be defined. Simulations of wet and dry thermal oxidation steps, according to the experimental process

Fig. 4. Left: initial structures constructed in Sentaurus Process and used as input for oxidation simulations: (a) 2D circular silicon nanowire; (b) 3D cylindrical vertical silicon nanowire on a silicon substrate. Right: (c) 3D nanowire after simulation of sacrificial oxidation.

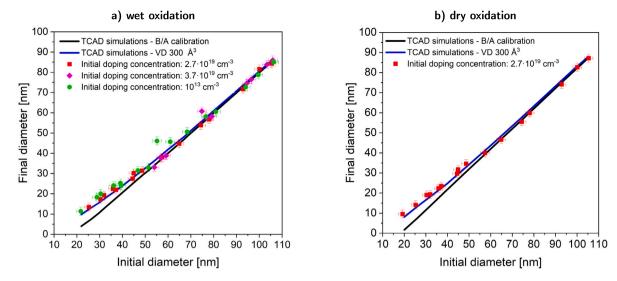

Fig. 5. Simulation results of final nanowire diameter after (a) wet thermal oxidation and (b) dry thermal oxidation, as a function of initial nanowire diameter before oxidation, using calibrated B/A parameters and the default stress-dependent oxidation model from  $AdvancedCalibration\ U-2022.12$  (black solid line) and using calibrated B/A parameters and calibrated activation volume  $V_D$  (blue solid line). Simulation results are compared to experimental measurements, reported with symbols.

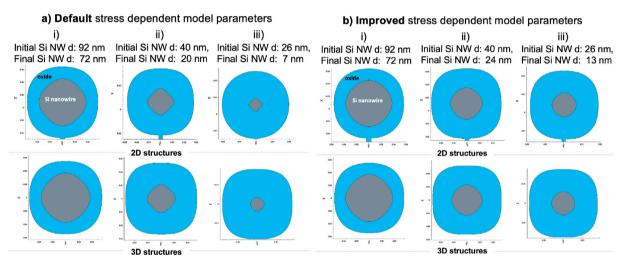

Fig. 6. Simulated shape of nanowires with different initial diameters after wet sacrificial oxidation simulation in Sentaurus Process, using (i) the default stress-dependent oxidation model from AdvancedCalibration U-2022.12 and (ii) the calibrated stress-dependent oxidation model, for the 2D and 3D case (the cross-section at half nanowire height is shown).

conditions described in Section 2, were performed on these 2D and 3D structures, varying the initial nanowire diameters in the range of the fabricated nanowires, i.e. from 20 nm to 100 nm. The simulations were initially performed using default parameters for the oxidation models from Sentaurus Process AdvancedCalibration U-2022.12 [29]. All the simulations were performed enabling orientation dependence, doping dependence and stress dependence of oxidation. A suitably fine mesh has been employed for the nanowire to allow a correct reproduction of the nanowire diameter and shape after oxidation including computation of mechanical stress. For 2D structures, the plane strain assumption is used, i.e. the strain in the third direction is assumed to be zero. Simulations of the 3D structures give comparable results to 2D structures: the difference between the computed nanowire diameter values in 2D and 3D (cross-section of the vertical nanowire at half height) is always lower than 1 nm. We can thus conclude that the plane strain assumption can be used in 2D simulations for our case (it has to be noted that the nanowire height of 210 nm in this case is much higher than the diameter). On the other side, 3D structures are particularly useful to simulate the oxidation at the bottom and at the top of the nanowire, where the diameter of the silicon nanowires becomes slightly higher, as it can be seen in Fig. 4.c and also in the SEM micrographs in Fig. 1.c, due to increased stress.

The simulated nanowire diameters have been calculated from the area of the silicon nanowire (cross-section at mid-height for the 3D case) using the area formula of a circle, and are compared to the experimental data in Fig. 5 for wet and dry oxidation. Starting from the default parameters of the Sentaurus Process Advanced Calibration, in a first step, the BA0 parameters for the exposed orientations in the nanowires (< 100> and < 110>) were multiplied by the same factor to fit the measured final diameters for the nanowires with initial diameters exceeding 60 nm. The resulting black lines are denoted "TCAD simulations - B/A calibration" in both figures. As it can be seen, the curves describe the experiments in this range very well. For thinner initial diameters, however, the data deviates from these lines and follows lines with a smaller slope. We will further on refer to thick nanowires when addressing nanowires with initial diameters higher than 60 nm and thin nanowires when addressing nanowires with initial diameters lower than 60 nm. The calibrated pre-exponential factors of the B/A parameters are reported in Table 1. The respective shapes of selected nanowires after oxidation are shown in Fig. 6.a for three different initial diameters as well as for the 2D and 3D cases (cross-section at half height). The results in Fig. 6.a refer to the case of wet oxidation-dry oxidation gives similar results (not shown). For the thin diameters, 2D and 3D simulations results in slightly different shapes, even though the resulting

**Table 1**Set of calibrated parameters.

|     | BA0 <sub>&lt;100&gt;</sub> | BA0<110>   | $V_D$              |

|-----|----------------------------|------------|--------------------|

| wet | 0.09 cm/s                  | 0.125 cm/s | 300 Å <sup>3</sup> |

| dry | 0.28 cm/s                  | 0.392 cm/s | 300 $Å^{3}$        |

diameter values are comparable. It can be seen that TCAD simulations predict an almost circular shape only for the thick nanowires. The simulated shape of the silicon nanowire becomes more *squared* as the diameter decreases. Based on the simulation, it thus appears that the orientation dependence is the predominant effect governing the shape of smallest nanowires. This, however, represents the opposite trend of what is observed experimentally.

When going to the regime of thin nanowires, we note that a change in the B/A parameter just leads to a rigid shift of the whole line but not to a change of the slope. The smaller oxidation rate for such initial diameters is a clear confirmation of the self-limited oxide growth reported in literature. To improve the agreement between simulation and experiment for the entire range of nanowire diameters, we performed a calibration work focusing on the stress-dependent oxidation model in Sentaurus Process by varying the activation volumes  $V_k$  and  $V_D$ . Changes in  $V_k$  also resulted in rigid shifts of the black curves and not in the desired decrease of the slopes for low diameter values. However, calibrating the value of  $V_D$ , it was possible to obtain the desired trend and a value of  $V_D = 300 \text{ Å}^3$  (see also Table 1) was found to fit both the wet and dry oxidation regimes best. The respective simulation results, denoted "TCAD simulations — VD 300 Å3" in Fig. 5.a and Fig. 5.b, agree well with the experimental data for the entire range of nanowire diameters. Fig. 6.b reports the shapes of the nanowires after wet sacrificial oxidation using the improved model. Again, similar results are obtained for dry oxidation (not shown). It can be seen that the resulting shape is rather circular for thick and thin nanowires. We can conclude that the stress has an important effect on the establishment of the circular shape of the nanowire during oxidation: even though the oxidation initially proceeds faster in the < 110> direction as compared to the < 100> direction, the faster oxidation will also lead to higher compressive stress and to a reduced oxidant diffusion so that the orientation-enhanced oxidation is significantly reduced. In the end, the nanowires will assume a more circular shape than without the self-limiting effects.

#### 3.2. Boron concentration in nanowires after oxidation

Full 3D TCAD simulations of thermal oxidation were also utilized to predict the boron loss from the silicon nanowires into the growing oxide. Exchange of boron between silicon and oxide is taken into account by the three-phase model implemented in Sentaurus Process on the basis of the work by Lau et al. [36], and Oh and Ward [37]. It considers an interface layer in between the silicon and silicon dioxide phases which is modeled as a  $\delta$ -layer with a constant concentration of traps, partly filled with dopants. The traps are coupled by rate equations to the silicon and oxide phases. The model parameters are the trapping rate  $T_{Si}$  of boron atoms from silicon, the emission rate  $E_{Si}$  to silicon, the trapping rate  $T_{Ox}$  from the oxide, the emission rate  $E_{Ox}$  to the oxide and the trap density. In all simulations, the full stress-dependent oxidation model with the novel set of calibrated parameters presented in Section 3.1 was used.

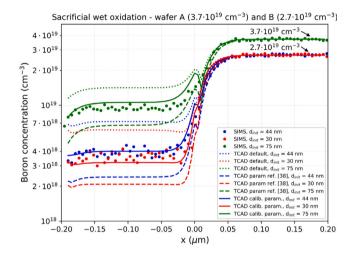

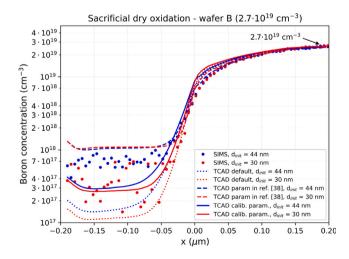

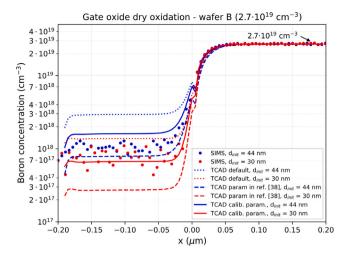

The resulting boron concentration after thermal oxidation was measured in selected nanowires with high initial doping concentrations by SIMS as described in Section 2. In a first step, the boron profiles were compared to TCAD simulation results using the segregation model parameters from the *AdvancedCalibration U-2022.12*. The results can be found in Figs. 7–9. For both the experiment and the simulation, the reported boron concentrations corresponds to the mean concentration in a slide perpendicular to the main axis of the nanowire. The abscissa

gives the vertical position along the nanowire height direction (axis x in Fig. 4.c) with the origin at the top surface of the substrate (nanowire–substrate interface). Fig. 7 refers to the sacrificial wet oxidation step (850 °C for 5 min) for samples fabricated on wafers with slightly different initial doping, i.e. wafer A with 3.7  $\cdot 10^{19}$  cm<sup>-3</sup> and wafer B with 2.7  $\cdot 10^{19}$  cm<sup>-3</sup>, respectively. Fig. 8 reports the results of the sacrificial dry oxidation (860 °C for 66 min) on samples from wafer B. In this case, SIMS measurements have more noise due to the low number of residual boron atoms in the silicon nanowires. Finally, Fig. 9 shows results for the dry oxidation process used for gate oxide growth (725 °C for 20 min), which is performed after the sacrificial wet oxidation and wet oxide stripping of nanowires from wafer B. TCAD simulations were also performed using another set of calibrated

Fig. 7. Average boron concentration in the nanowire cross-section disk, as a function of vertical position along the nanowire height direction (axis x in Fig. 4.c) after sacrificial wet oxidation (850 °C for 5 min). Wafer A ( $d_{init}$  = 75 nm) has an initial boron concentration of 3.7 ·10<sup>19</sup> cm<sup>-3</sup> and wafer B ( $d_{init}$  = 30, 45 nm) has an initial boron concentration of 2.7 ·10<sup>19</sup> cm<sup>-3</sup>. SIMS measurements are shown with symbols, TCAD simulations using default segregation model parameters from *AdvancedCalibration U-2022.12* with dotted lines, TCAD simulations using calibrated parameters from [38] with dashed lines and TCAD simulations with novel calibrated parameters (Table 2) with calibrate

**Fig. 8.** Average boron concentration in the nanowire cross-section disk, as a function of vertical position along the nanowire height direction (axis x in Fig. 4.c) after sacrificial dry oxidation (860 °C for 66 min).

**Fig. 9.** Average boron concentration in the nanowire cross-section disk, as a function of vertical position along the nanowire height direction (axis x in Fig. 4.c) after gate dry oxidation (725 °C for 20 min, performed after the sacrificial wet oxidation and wet oxide stripping).

parameters for the three-phase segregation model, described in [38], that provided very good results in determining threshold voltages found to be particularly sensitive to boron segregation, namely for transistors fabricated in a power MOS process technology involving both n-type and p-type doping in the channel. The simulation results using these parameters are plotted with dashed lines in Figs. 7-9. TCAD simulations with default AdvancedCalibration U-2022.12 parameters and parameters from Ref. [38] provide good results close to the bulk part of the structures, i.e. for x > 0, whereas they have lower accuracy for the estimation of boron concentration in the nanowires. For wet sacrificial oxidation, simulations with default parameters overestimate the concentration and simulations with parameters from [38] underestimate the concentration. Similar results are found for the simulations of a subsequent gate dry oxidation (after wet oxidation simulation and oxide stripping) in Fig. 9. It has to be noted that the starting boron concentration in the nanowire is already wrongly obtained from the previous simulation of the sacrificial oxidation, as we can see in Fig. 7. For the case of sacrificial dry oxidation, there is an opposite trend: simulations with default parameters calculate a lower concentration whereas simulations with parameters from [38] overestimate the measured values. Finally, Figs. 7-9 report in solid lines results of TCAD simulations using a novel set of calibrated parameters, listed in Table 2, which has been developed in this work. Using this set of parameters, it is possible to predict more accurately the measured boron distribution in the nanowire, preserving the good accuracy in the bulk part. Boron segregation during wet oxidation is very well simulated. Also, the final boron concentration in the nanowire after gate dry oxidation (Fig. 9) matches the SIMS data. Finally, better results, compared to the simulations with existing parameters sets presented before, are obtained for the sacrificial dry oxidation case, even though the accuracy is not as good as for the wet oxidation case.

**Table 2**Set of calibrated parameters.

|                              | Boron                                  |

|------------------------------|----------------------------------------|

| $T_{Si}$ (cm <sup>3</sup> s) | $8 \cdot 10^{-14} \cdot e^{-2.33/kT}$  |

| $E_{Si}$ (cm <sup>3</sup> s) | $4 \cdot 10^{-14} \cdot e^{-2.2/kT}$   |

| $T_{Ox}$ (cm <sup>3</sup> s) | $1.6 \cdot 10^{-12} \cdot e^{-2.5/kT}$ |

| $E_{Ox}$ (cm <sup>3</sup> s) | $2 \cdot 10^{-14} \cdot e^{-2.44/kT}$  |

#### 4. Conclusion

In this work we have studied, by means of TCAD simulations, the thermal oxidation of silicon nanowires, a crucial step in the process flow for the fabrication of GAA-NW-FETs. We have investigated selflimiting effects and boron segregation in the growing oxide with the objective to accurately predict the final silicon nanowire diameter and the resulting doping concentration at the end of the thermal oxidation steps, which are two key parameters that determine the electrical behavior of junctionless GAA-NW-FETs. Simulations were done with Sentaurus Process of Synopsys [28]. First of all, the accuracy of simulation results using the parameters provided in the AdvancedCalibration U-2022.12 file [29] was assessed and the models to be improved were identified. Regarding the determination of the nanowire diameters after thermal oxidation, a calibration work was performed to extend the validity of the stress-dependent oxidation model to nanowires with small diameter (i.e. initial nanowire diameters lower than 60 nm and final nanowire diameters after oxidation lower than 40 nm) which were not correctly simulated with the existing model. For this range of diameters, in fact, there is an enhancement of self-limiting effects and the simulated diameters of silicon nanowires after oxidation underestimate the measured data. We showed that by calibrating the stress-dependent oxidant diffusivity model, we can improve the simulation results and reproduce the measured diameters in the full range of considered values. Moreover, process simulations with the new parameter set also predicted the correct circular nanowire shape, despite the orientation dependence of silicon oxidation. In fact, while for large nanowire diameters a circular shape can be correctly obtained in TCAD simulations with the default model parameters in AdvancedCalibration U-2022.12, for thin nanowires the circular shape is obtained only with the here presented calibrated parameters. This result suggests that the stress in the oxide plays a decisive role in the physical origin of the cylindrical shape. Simulation of doping loss in nanowires after thermal oxidation due to boron segregation into the growing oxide was also addressed. The simulated resulting boron segregation in the nanowire was compared to experimental results obtained with a novel SIMS approach, described in [34]. Three-phase segregation model parameters from AdvancedCalibration U-2022.12 and from Ref. [38] were used and compared. A novel set of calibrated parameters was developed to obtain a more accurate prediction of boron concentration inside the silicon nanowires.

#### CRediT authorship contribution statement

Chiara Rossi: Conceptualization, Data curation, Formal analysis, Investigation, Methodology, Software, Visualization, Writing – original draft. Jonas Müller: Data curation, Investigation, Methodology, Writing – review & editing. Peter Pichler: Conceptualization, Funding acquisition, Project administration, Resources, Supervision, Validation, Writing – review & editing. Paweł Piotr Michałowski: Data curation, Investigation, Methodology, Funding acquisition, Resources, Writing – review & editing. Guilhem Larrieu: Funding acquisition, Resources, Supervision, Validation, Writing – review & editing.

#### **Declaration of competing interest**

The authors declare the following financial interests/personal relationships which may be considered as potential competing interests: Co-author guest editor of Special Issue "Materials engineering for advanced semiconductor devices" of Materials Science in Semiconductor Processing - P.P. If there are other authors, they declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper.

#### Data availability

Data will be made available on request.

#### Acknowledgments

The research leading to these results has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No. 871813 MUNDFAB. This work was partly supported by LAAS-CNRS micro and nanotechnologies platform, a member of the Renatech french national network.

#### References

- [1] A. Veloso, T. Huynh-Bao, P. Matagne, D. Jang, G. Eneman, N. Horiguchi, et al., Nanowire & nanosheet FETs for ultra-scaled, high-density logic and memory applications, Solid-State Electron. 168 (2020) 107736, http://dx.doi.org/10.1016/j.sse.2019.107736.

- [2] K.H. Yeo, S.D. Suk, M. Li, Y.-Y. Yeoh, K.H. Cho, K.H. Hong, et al., Gate-all-around (GAA) twin silicon nanowire MOSFET (TSNWFET) with 15 nm length gate and 4 nm radius nanowires, in: 2006 International Electron Devices Meeting, 2006, pp. 1–4, http://dx.doi.org/10.1109/IEDM.2006.346838.

- [3] N. Singh, A. Agarwal, L. Bera, T. Liow, R. Yang, S. Rustagi, et al., High-performance fully depleted silicon nanowire (diameter /spl les/ 5 nm) gateall-around CMOS devices, IEEE Electron Device Lett. 27 (5) (2006) 383–386, http://dx.doi.org/10.1109/LED.2006.873381.

- [4] W. Lu, P. Xie, C.M. Lieber, Nanowire transistor performance limits and applications, IEEE Trans. Electron Devices 55 (11) (2008) 2859–2876, http://dx.doi.org/10.1109/TED.2008.2005158.

- [5] A. Veloso, E. Altamirano-Sánchez, S. Brus, B.T. Chan, M. Cupak, M. Dehan, et al., Vertical nanowire FET integration and device aspects, ECS Trans. 72 (4) (2016) 31, http://dx.doi.org/10.1149/07204.0031ecst.

- [6] G. Larrieu, X.-L. Han, Vertical nanowire array-based field effect transistors for ultimate scaling, Nanoscale 5 (2013) 2437–2441, http://dx.doi.org/10.1039/ C3NR33738C

- [7] P.-F. Fazzini, C. Bonafos, A. Claverie, A. Hubert, T. Ernst, M. Respaud, Modeling stress retarded self-limiting oxidation of suspended silicon nanowires for the development of silicon nanowire-based nanodevices, J. Appl. Phys. 110 (3) (2011) http://dx.doi.org/10.1063/1.3611420.

- [8] G. Larrieu, Y. Guerfi, X. Han, N. Clément, Sub-15nm gate-all-around field effect transistors on vertical silicon nanowires, Solid-State Electron. 130 (2017) 9–14, http://dx.doi.org/10.1016/j.sse.2016.12.008.

- [9] B. Bold, An industrial perspective of technology CAD for advanced CMOS technologies, Microelectron. Eng. 34 (1996) 65–66, http://dx.doi.org/10.1016/ S0167-9317(96)00023-8.

- [10] D.-B. Kao, J. McVittie, W. Nix, K. Saraswat, Two-dimensional thermal oxidation of silicon I. Experiments, IEEE Trans. Electron Devices 34 (5) (1987) 1008–1017, http://dx.doi.org/10.1109/T-ED.1987.23037.

- [11] D.-B. Kao, J. McVittie, W. Nix, K. Saraswat, Two-dimensional thermal oxidation of silicon - II. Modeling stress effects in wet oxides, IEEE Trans. Electron Devices 35 (1) (1988) 25–37, http://dx.doi.org/10.1109/16.2412.

- [12] M. Uematsu, H. Kageshima, K. Shiraishi, M. Nagase, S. Horiguchi, Y. Takahashi, Two-dimensional simulation of pattern-dependent oxidation of silicon nanostructures on silicon-on-insulator substrates, Solid-State Electron. 48 (6) (2004) 1073–1078, http://dx.doi.org/10.1016/j.sse.2003.12.019.

- [13] J. Fan, R. Huang, R. Wang, Q. Xu, Y. Ai, X. Xu, et al., Two-dimensional self-limiting wet oxidation of silicon nanowires: Experiments and modeling, IEEE Trans. Electron Devices 60 (9) (2013) 2747–2753, http://dx.doi.org/10.1109/TED.2013.2274493.

- [14] H. Heidemeyer, C. Single, F. Zhou, F.E. Prins, D.P. Kern, E. Plies, Self-limiting and pattern dependent oxidation of silicon dots fabricated on silicon-on-insulator material, J. Appl. Phys. 87 (9) (2000) 4580–4585, http://dx.doi.org/10.1063/1. 272105

- [15] X.-L. Han, G. Larrieu, C. Krzeminski, Modelling and engineering of stress based controlled oxidation effects for silicon nanostructure patterning, Nanotechnology 24 (49) (2013) 495301, http://dx.doi.org/10.1088/0957-4484/24/49/495301.

- [16] F.-J. Ma, S.C. Rustagi, G.S. Samudra, H. Zhao, N. Singh, G.Q. Lo, et al., Modeling of stress-retarded thermal oxidation of nonplanar silicon structures for realization of nanoscale devices, IEEE Electron Device Lett. 31 (7) (2010) 719–721, http: //dx.doi.org/10.1109/LED.2010.2047375.

- [17] H.I. Liu, D.K. Biegelsen, F.A. Ponce, N.M. Johnson, R.F.W. Pease, Self-limiting oxidation for fabricating sub-5 nm silicon nanowires, Appl. Phys. Lett. 64 (11) (1994) 1383–1385, http://dx.doi.org/10.1063/1.111914.

- [18] H. Cui, C.X. Wang, G.W. Yang, Origin of Self-Limiting Oxidation of Si Nanowires, Nano Lett. 8 (9) (2008) http://dx.doi.org/10.1021/nl8011853.

- [19] M. Liu, P. Jin, Z. Xu, D.A. Hanaor, Y. Gan, C. Chen, Two-dimensional modeling of the self-limiting oxidation in silicon and tungsten nanowires, Theor. Appl. Mech. Lett. 6 (5) (2016) 195–199, http://dx.doi.org/10.1016/j.taml.2016.08.002.

- [20] F.-J. Ma, S.C. Rustagi, H. Zhao, G.S. Samudra, N. Singh, K.D. Budhaaraju, et al., Modeling of stress-retarded orientation-dependent oxidation: shape engineering of silicon nanowire channels, in: 2009 IEEE International Electron Devices Meeting, IEDM, 2009, pp. 1–4, http://dx.doi.org/10.1109/IEDM.2009.5424306.

- [21] C. Gonzalez, J. McVittie, A study of trenched capacitor structures, IEEE Electron Device Lett. 6 (5) (1985) 215–218, http://dx.doi.org/10.1109/EDL.1985.26102.

- [22] S. Ye, K. Yamabe, T. Endoh, Precise fabrication of uniform sub-10-nm-diameter cylindrical silicon nanopillars via oxidation control, Scr. Mater. 198 (2021) 113818, http://dx.doi.org/10.1016/j.scriptamat.2021.113818.

- [23] S. Ye, T. Endoh, Edge effect in the oxidation of three-dimensional nano-structured silicon, Mater. Sci. Semicond. Process. 93 (2019) 266–273, http://dx.doi.org/10. 1016/j.mssp.2019.01.023.

- [24] A.S. Grove, O. Leistiko Jr., C.T. Sah, Redistribution of acceptor and donor impurities during thermal oxidation of silicon, J. Appl. Phys. 35 (1964) 2695–2701, http://dx.doi.org/10.1063/1.1713825.

- [25] N. Fukata, S. Ishida, S. Yokono, R. Takiguchi, J. Chen, T. Sekiguchi, et al., Segregation behaviors and radial distribution of dopant atoms in silicon nanowires, Nano Lett. 11 (2) (2011) 651–656, http://dx.doi.org/10.1021/nl103773e.

- [26] J.-S. Yoon, T. Rim, J. Kim, M. Meyyappan, C.-K. Baek, Y.-H. Jeong, Vertical gate-all-around junctionless nanowire transistors with asymmetric diameters and underlap lengths, Appl. Phys. Lett. 105 (10) (2014) http://dx.doi.org/10.1063/ 1.4895030.

- [27] C. Rossi, A. Burenkov, P. Pichler, E. Bär, J. Müller, G. Larrieu, Performance of vertical gate-all-around nanowire p-MOS transistors determined by boron depletion during oxidation, Solid-State Electron. 200 (2023) 108551, http://dx. doi.org/10.1016/j.sse.2022.108551.

- [28] Sentaurus process of synopsys TCAD, User Guide, release U-2022.12, 2022, https://www.synopsys.com/manufacturing/tcad.html.

- [29] Advanced Calibration for Process Simulation, User Guide, Version U-2022.12., 2022, https://www.synopsys.com/manufacturing/tcad.html.

- [30] X.-L. Han, G. Larrieu, E. Dubois, Realization of vertical silicon nanowire networks with an ultra high density using a top-down approach, J. Nanosci. Nanotechnol. 10 (11) (2010) 7523–7527, http://dx.doi.org/10.1166/jnn.2010.2841.

- [31] Y. Guerfi, F. Carcenac, G. Larrieu, High resolution HSQ nanopillar arrays with low energy electron beam lithography, Microelectron. Eng. 110 (2013) 173–176, http://dx.doi.org/10.1016/j.mee.2013.03.055.

- [32] B.E. Deal, M. Sklar, Thermal oxidation of heavily doped silicon, J. Electrochem. Soc. 112 (4) (1965) 430. http://dx.doi.org/10.1149/1.2423562.

- [33] E.A. Irene, D.W. Dong, Silicon oxidation studies: The oxidation of heavily Band P-doped single crystal silicon, J. Electrochem. Soc. 125 (7) (1978) 1146, http://dx.doi.org/10.1149/1.2131638.

- [34] P.P. Michałowski, J. Müller, C. Rossi, A. Burenkov, E. Bär, G. Larrieu, P. Pichler, Secondary ion mass spectrometry quantification of boron distribution in an array of silicon nanowires, Measurement 211 (2023) 112630, http://dx.doi.org/10. 1016/j.measurement.2023.112630.

- [35] B.E. Deal, A.S. Grove, General relationship for the thermal oxidation of silicon, J. Appl. Phys. 36 (12) (1965) 3770, http://dx.doi.org/10.1063/1.1713945.

- [36] F. Lau, L. Mader, C. Mazure, C. Werner, M. Orlowski, A model for phosphorus segregation at the silicon-silicon dioxide interface, Appl. Phys. A 49 (1989) 671–675, http://dx.doi.org/10.1007/BF00616992.

- [37] Y.-S. Oh, D.E. Ward, A calibrated model for trapping of implanted dopants at material interface during thermal annealing, in: International Electron Devices Meeting 1998. Technical Digest (Cat. No.98CH36217), 1998, pp. 509–512, http: //dx.doi.org/10.1109/IEDM.1998.746409.

- [38] S. Koffel, A. Burenkov, M. Sekowski, P. Pichler, D. Giubertoni, M. Bersani, et al., On an improved boron segregation calibration from a particularly sensitive power MOS process, Phys. Status Solidi C 11 (1) (2014) 12–15, http://dx.doi.org/10.1002/pssc.201300152.