## Optimization of the elaboration of insulating layers for the gate structures and the passivation of MIS-HEMT transistors on GaN

Richard Meunier

## ► To cite this version:

Richard Meunier. Optimization of the elaboration of insulating layers for the gate structures and the passivation of MIS-HEMT transistors on GaN. Electronics. Université Paul Sabatier - Toulouse III, 2016. English. NNT: 2016TOU30150. tel-01376016

## HAL Id: tel-01376016 https://laas.hal.science/tel-01376016v1

Submitted on 4 Oct 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### Université Fédérale

**Toulouse Midi-Pyrénées**

en vue de l'obtention du

## DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE

## Délivré par :

Université Toulouse 3 Paul Sabatier (UT3 Paul Sabatier)

Présentée par

## **Richard MEUNIER**

Soutenue le mercredi 22 juin 2016

# Optimization of the elaboration of insulating layers for the gate structures and the passivation of MIS-HEMT transistors on GaN

*(Optimisation de l'élaboration de couches isolantes pour les structures de grille et la passivation de transistor MIS-HEMTs sur matériau GaN)*

Directeurs de thèse :

M. Frédéric MORANCHO – Professeur des Universités, Université Toulouse 3

M. Alphonse TORRES – Ingénieur CEA-LETI

## Membres du Jury

| M. Yvon CORDIER         | Directeur de Recherche CNRS, CNRS-CRHEA           | Rapporteur  |

|-------------------------|---------------------------------------------------|-------------|

| Mme Marie-Paule BESLAND | Directrice de Recherche CNRS, IMN Jean Rouxel     | Rapporteur  |

| M. Farid MEDJDOUB       | Chargé de Recherche CNRS, IEMN                    | Examinateur |

| M. Gaëtan TOULON        | Ingénieur, EXAGAN                                 | Examinateur |

| M. Alain CAZARRÉ        | Professeur des Universités, Université Toulouse 3 | Examinateur |

## Table of contents

| A | cknov | wledgn  | nents                                                                                           | i   |

|---|-------|---------|-------------------------------------------------------------------------------------------------|-----|

| G | enera | d Intro | oduction                                                                                        | iii |

| 1 | Gal   | N for p | ower electronics : state of the art and context                                                 | 1   |

|   | 1.1   | Power   | electronics and devices $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 1   |

|   |       | 1.1.1   | Needs and demands of the market, specifications, theory VS                                      |     |

|   |       |         | reality                                                                                         | 1   |

|   |       | 1.1.2   | Limits of silicon                                                                               | 3   |

|   |       | 1.1.3   | Wide band gap materials                                                                         | 5   |

|   |       | 1.1.4   | Figures of merit of semiconductors for power application                                        | 9   |

|   | 1.2   | Place   | of GaN in power electronics                                                                     | 11  |

|   |       | 1.2.1   | Generalities on GaN and crystal structure                                                       | 12  |

|   |       | 1.2.2   | GaN properties                                                                                  | 13  |

|   |       |         | 1.2.2.1 Electric properties                                                                     | 13  |

|   |       |         | 1.2.2.2 Physico-chemical properties                                                             | 18  |

|   |       | 1.2.3   | The AlGaN/GaN heterostructure                                                                   | 19  |

|   |       |         | 1.2.3.1 Spontaneous and piezoelectric polarization                                              | 21  |

|   |       |         | 1.2.3.2 Bidimensional electron channel                                                          | 23  |

|   |       | 1.2.4   | Models and formation mechanisms                                                                 | 26  |

|   | 1.3   | Conte   | xt of Ph.D.                                                                                     | 31  |

|   | 1.4   | Conclu  | usion                                                                                           | 33  |

| 2 | The   | Meta    | l Insulator Semiconductor structure on GaN                                                      | 35  |

|   | 2.1   | Preser  | ntation of the structure                                                                        | 35  |

|   |                | 2.1.1    | Principle of operation                                                  | 35 |

|---|----------------|----------|-------------------------------------------------------------------------|----|

|   |                | 2.1.2    | The metal-semiconductor junction                                        | 37 |

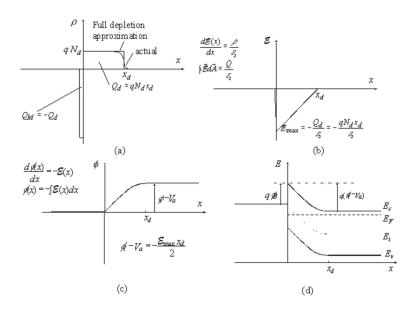

|   |                |          | 2.1.2.1 Full depletion approximation                                    | 37 |

|   |                |          | 2.1.2.2 Full depletion analysis                                         | 38 |

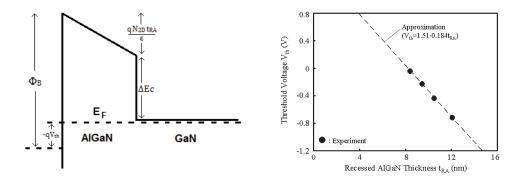

|   |                | 2.1.3    | HEMT and MIS-HEMT threshold voltage                                     | 41 |

|   | 2.2            | Dielec   | trics on GaN and AlGaN                                                  | 45 |

|   |                | 2.2.1    | MIS on GaN and AlGaN                                                    | 46 |

|   |                | 2.2.2    | Surface contamination and interface states density                      | 48 |

|   | 2.3            | Gate r   | recess etching                                                          | 50 |

|   |                | 2.3.1    | Principle                                                               | 50 |

|   |                | 2.3.2    | Threshold voltage increase                                              | 51 |

|   | 2.4            | Conclu   | usion                                                                   | 52 |

| 3 | Dev            | vice rea | alization                                                               | 55 |

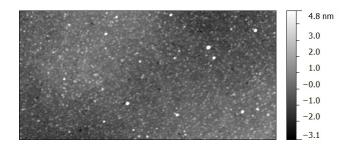

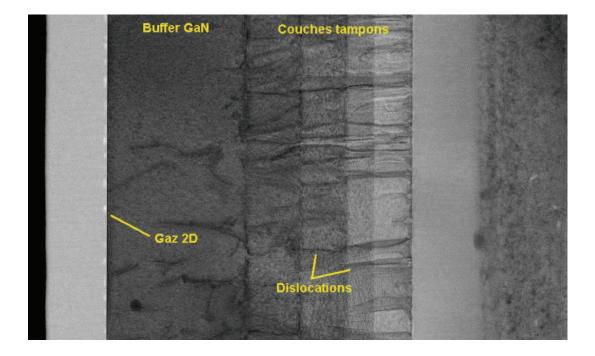

|   | 3.1            | Origin   | and characteristics of the material                                     | 55 |

|   | 3.2            | Surfac   | e conditioning                                                          | 57 |

|   |                | 3.2.1    | Chemical treatments                                                     | 57 |

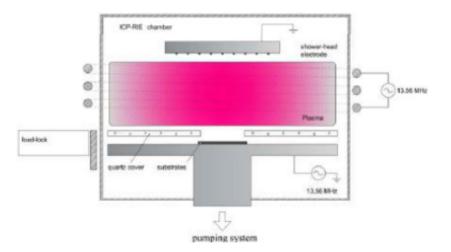

|   |                | 3.2.2    | Plasma treatments                                                       | 58 |

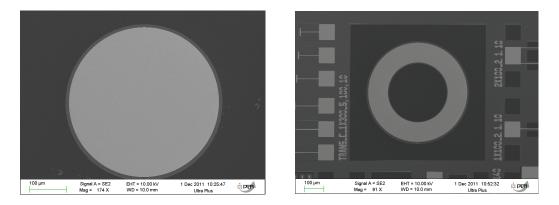

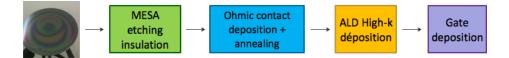

|   | 3.3            | MIS-H    | IEMT and capacitance fabrication                                        | 59 |

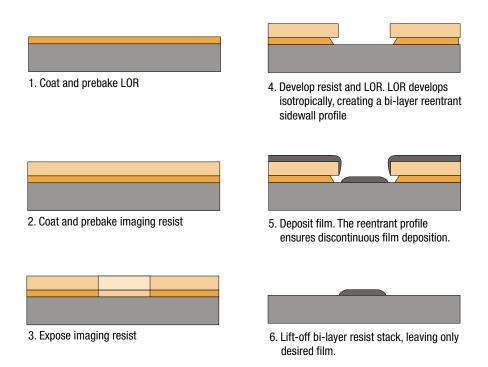

|   |                | 3.3.1    | Process flow                                                            | 60 |

|   |                | 3.3.2    | Encountered difficulties and adopted solutions                          | 61 |

|   |                | 3.3.3    | MESA etching insulation                                                 | 63 |

|   |                | 3.3.4    | Metallization and ohmic contact                                         | 63 |

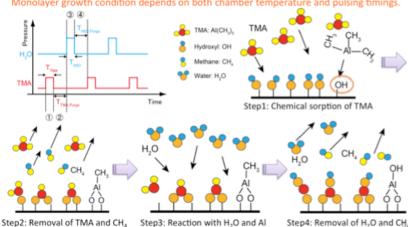

|   |                | 3.3.5    | High- $\kappa$ dielectric deposition and in-situ $N_2$ plasma treatment | 64 |

|   |                | 3.3.6    | Gate metal deposition                                                   | 65 |

|   | 3.4            | Option   | nal process : recess etching below gate                                 | 66 |

|   | 3.5            | Conclu   | usion                                                                   | 67 |

| 4 | $\mathbf{Res}$ | ults ar  | nd discussions                                                          | 69 |

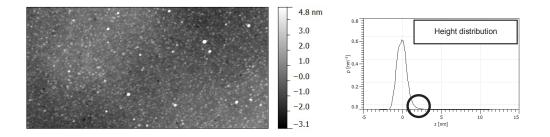

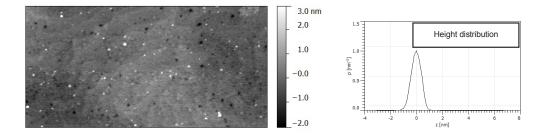

|   | 4.1            | Surfac   | e treatments and their characterization                                 | 69 |

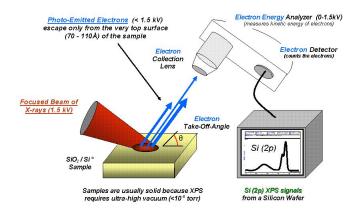

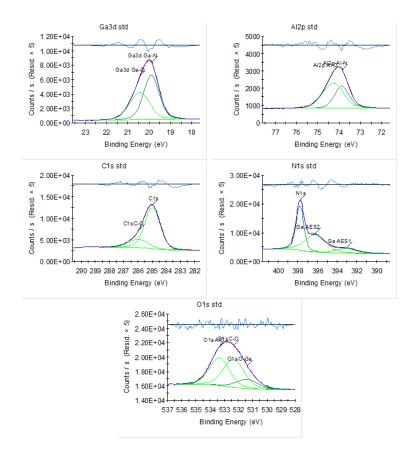

|   |                | 4.1.1    | X-Ray Photo-electron Spectroscopy                                       | 70 |

|   |                |          | 4.1.1.1 Principle                                                       | 70 |

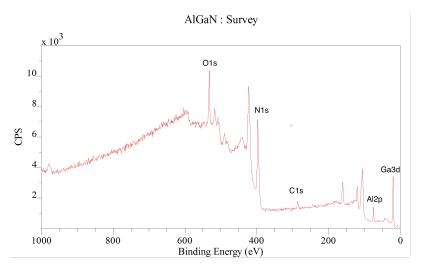

|   |                |          | 4.1.1.2 Application to the AlGaN surface                                | 73 |

|   |                | 4.1.2    | Chemical treatments                                                     | 74 |

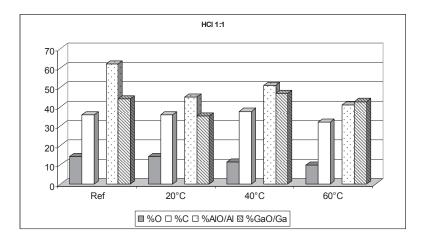

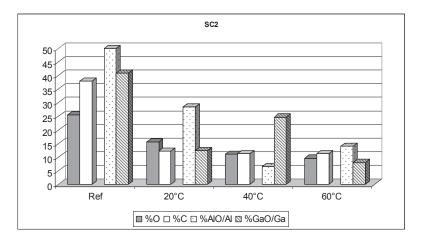

|     |        | 4.1.2.1 HCl and SC2 treatments $\ldots \ldots \ldots \ldots \ldots 74$                                                                                        |  |  |  |  |  |  |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

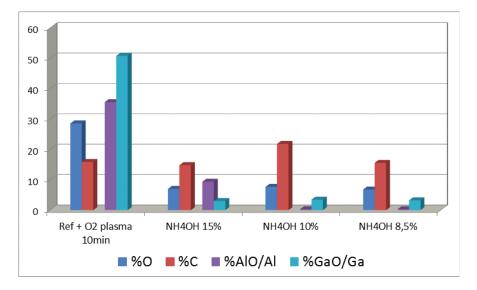

|     |        | 4.1.2.2 $NH_4OH$ and $SC1$                                                                                                                                    |  |  |  |  |  |  |

|     | 4.1.3  | .1.3 Plasma treatments                                                                                                                                        |  |  |  |  |  |  |

|     |        | 4.1.3.1 Oxygen plasma                                                                                                                                         |  |  |  |  |  |  |

|     |        | 4.1.3.2 Nitrogen containing plasma 81                                                                                                                         |  |  |  |  |  |  |

|     | 4.1.4  | Surface treatments conclusion                                                                                                                                 |  |  |  |  |  |  |

| 4.2 | Schott | tky gate devices                                                                                                                                              |  |  |  |  |  |  |

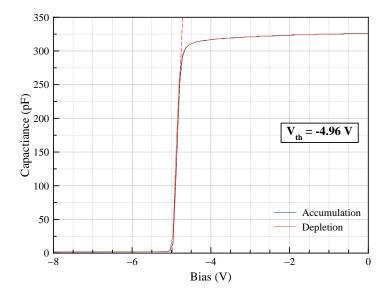

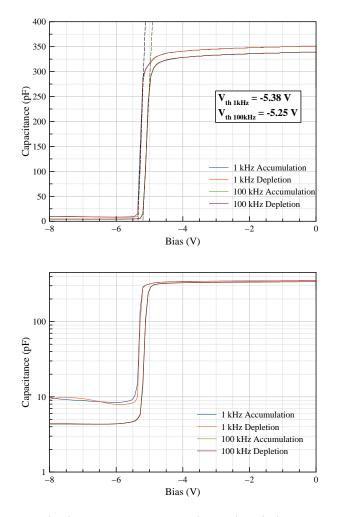

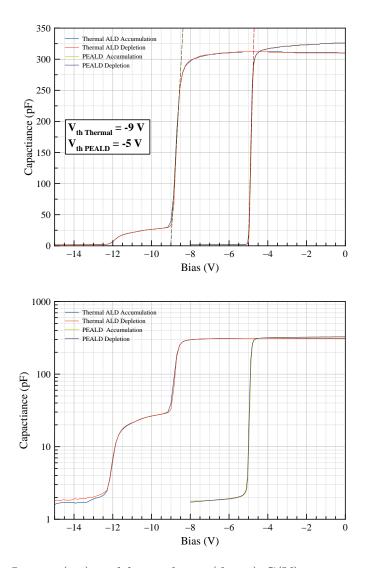

|     | 4.2.1  | C(V) results                                                                                                                                                  |  |  |  |  |  |  |

| 4.3 | MIS s  | tructures                                                                                                                                                     |  |  |  |  |  |  |

|     | 4.3.1  | Thermal ALD structures                                                                                                                                        |  |  |  |  |  |  |

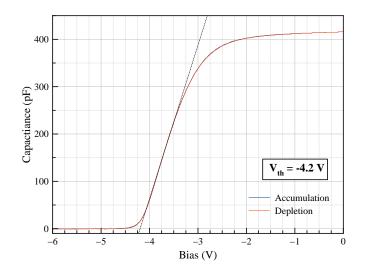

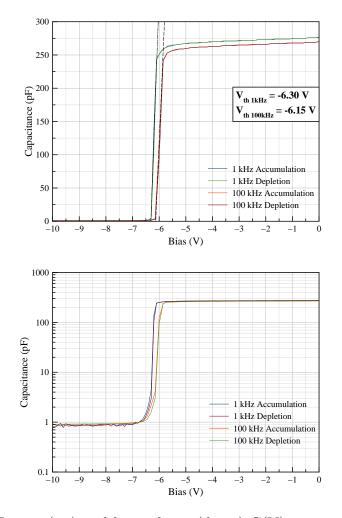

|     |        | $4.3.1.1  C(V) \text{ results} \dots \dots$             |  |  |  |  |  |  |

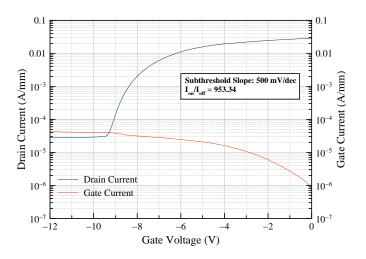

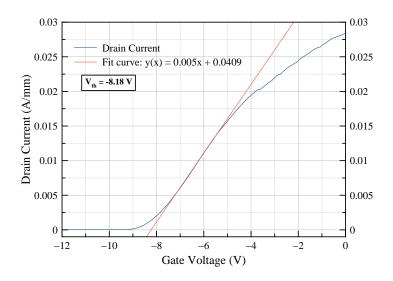

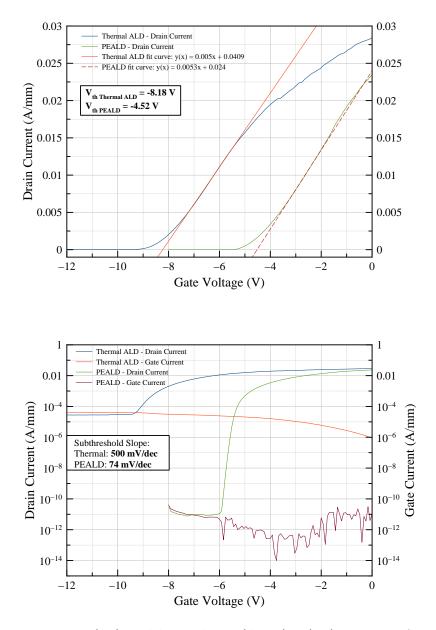

|     |        | 4.3.1.2 $I_d(V_g)$ results on circular transistor with $L_g=100\mu m$ 91                                                                                      |  |  |  |  |  |  |

|     | 4.3.2  | PEALD structures                                                                                                                                              |  |  |  |  |  |  |

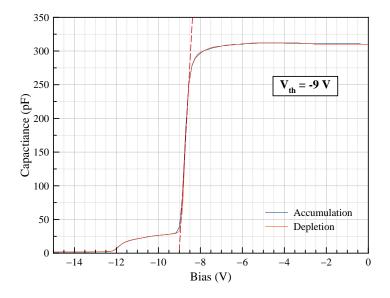

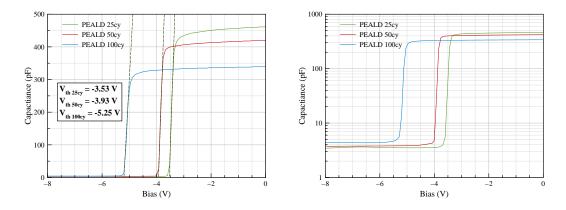

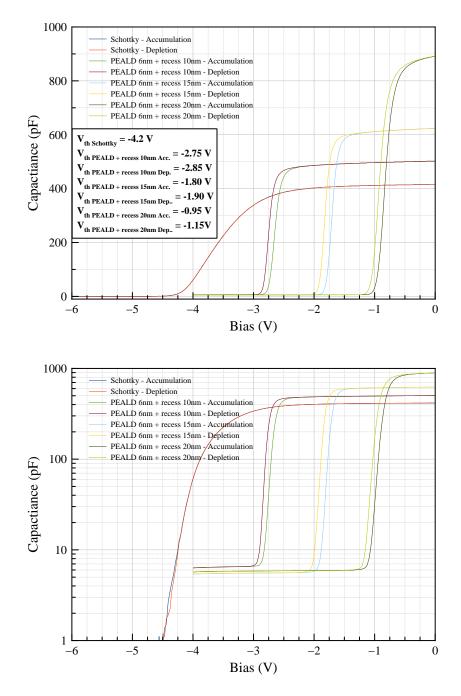

|     |        | $4.3.2.1  C(V) \text{ results} \dots 93$                                                          |  |  |  |  |  |  |

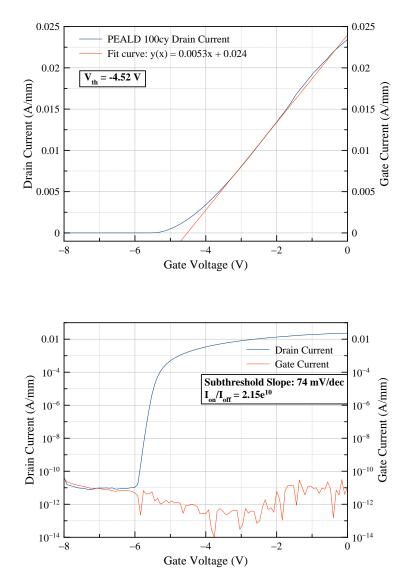

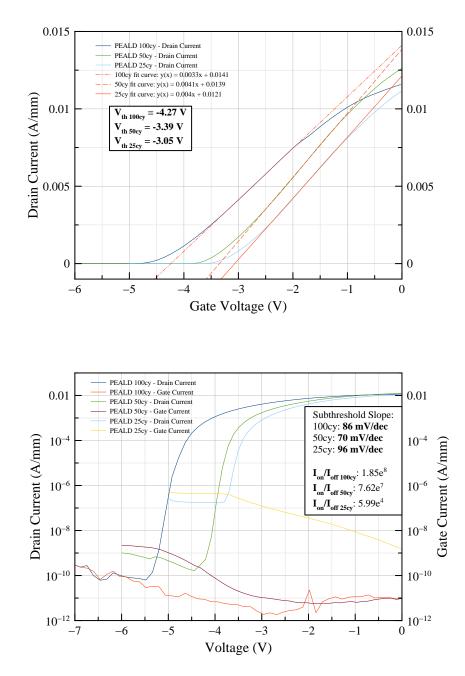

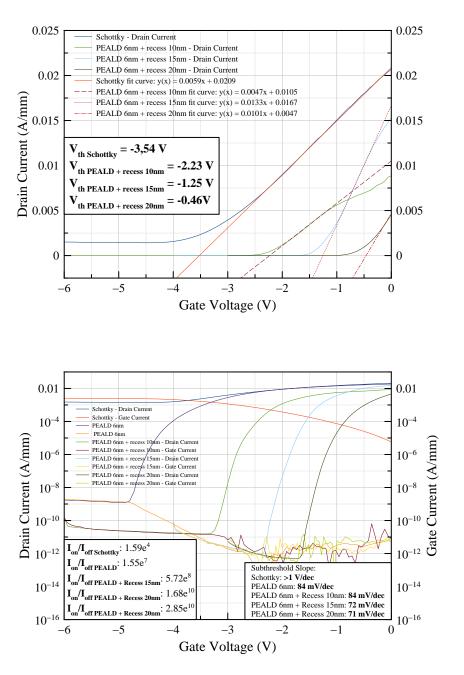

|     |        | 4.3.2.2 $I_d(V_g)$ results on circular transistor with $L_g=100\mu m$ 99                                                                                      |  |  |  |  |  |  |

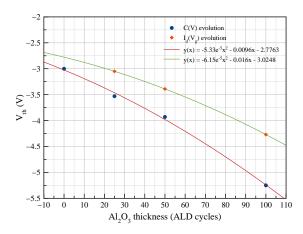

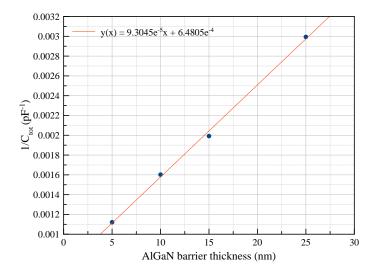

| 4.4 | Influe | nce of the dielectric thickness                                                                                                                               |  |  |  |  |  |  |

|     | 4.4.1  | C(V) results                                                                                                                                                  |  |  |  |  |  |  |

|     | 4.4.2  | $I_d(V_g)$ results on circular transistor with $L_g=100\mu m$ 103                                                                                             |  |  |  |  |  |  |

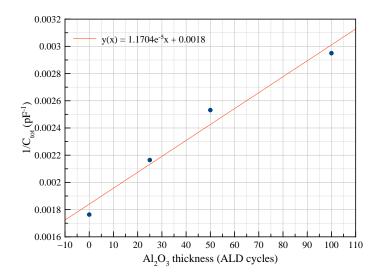

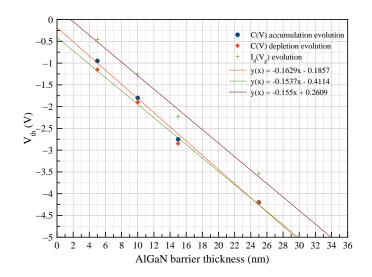

|     | 4.4.3  | Threshold voltage evolution                                                                                                                                   |  |  |  |  |  |  |

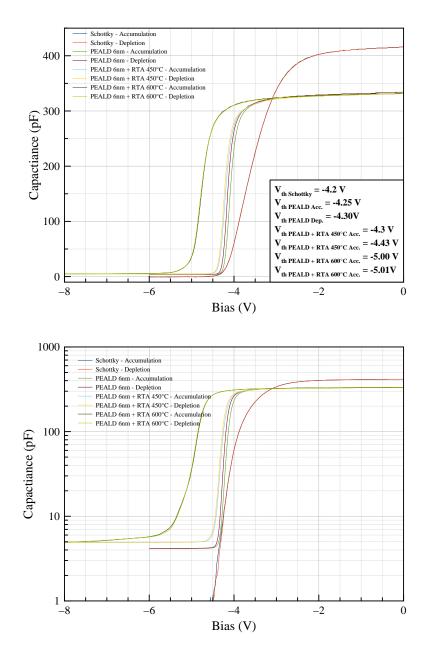

| 4.5 | Influe | nce of post-deposition thermal treatment                                                                                                                      |  |  |  |  |  |  |

|     | 4.5.1  | C(V) results                                                                                                                                                  |  |  |  |  |  |  |

|     | 4.5.2  | $I_d(V_g)$ results on circular transistor with $L_g=100\mu m$ 109                                                                                             |  |  |  |  |  |  |

| 4.6 | Super  | iority of PEALD over thermal ALD                                                                                                                              |  |  |  |  |  |  |

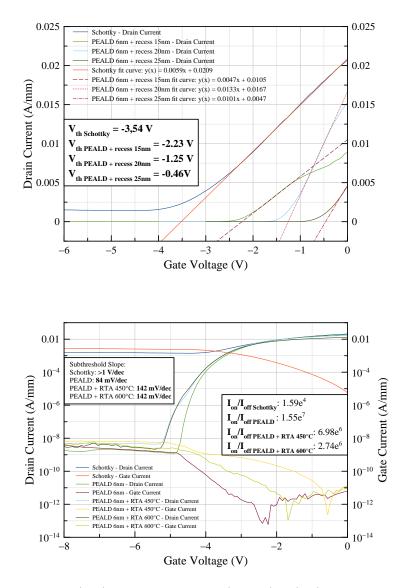

| 4.7 | Norma  | ally-Off architecture : MIS structure with partial or full AlGaN                                                                                              |  |  |  |  |  |  |

|     | recess | etching                                                                                                                                                       |  |  |  |  |  |  |

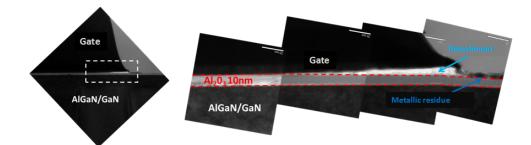

|     | 4.7.1  | Gate Recess Etching 119                                                                                                                                       |  |  |  |  |  |  |

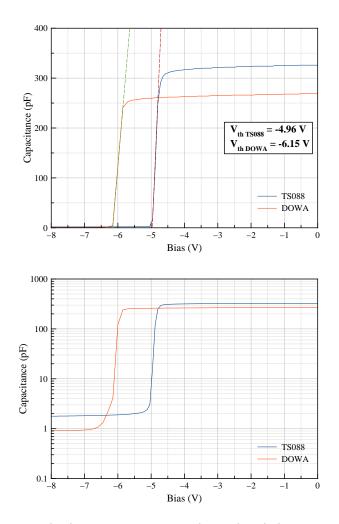

|     |        | 4.7.1.1 $C(V)$ Results $\ldots \ldots \ldots$ |  |  |  |  |  |  |

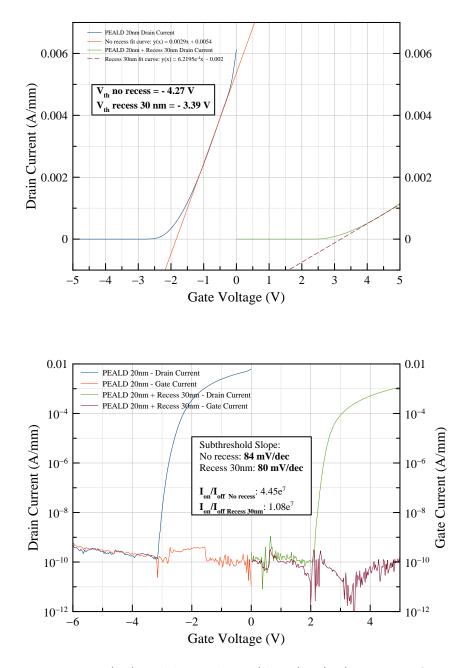

|     |        | 4.7.1.2 $I_d(V_g)$ results on circular transistor with $L_g=100\mu m$ 122                                                                                     |  |  |  |  |  |  |

|     |        | 4.7.1.3 Threshold voltage evolution                                                                                                                           |  |  |  |  |  |  |

|     | 4.7.2  | AlGaN Full-recess etching below gate                                                                                                                          |  |  |  |  |  |  |

| 4.8 | Conclu | usion $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $127$                                                                                             |  |  |  |  |  |  |

|     |        |                                                                                                                                                               |  |  |  |  |  |  |

## General conclusion

129

| Perspectives | 133 |

|--------------|-----|

| Bibliography | 134 |

## Acknowledgments

First and foremost I would like to thank the CEA-Leti and the LAAS-CNRS for allowing me to do my PhD under their care and supervision. I would like especially to thank the LC2E laboratory and all its members in CEA-Leti, where I had the chance to do the entirety of my thesis under the supervision of Mr. Alphonse TORRES. Regarding LAAS-CNRS, I would like to thank the professor and supervisor of my work, Pr. Frédéric MORANCHO who supported me continuously during all my research. It was a great pleasure and privilege to work with all these competent and kind scientists and researchers.

Still in CEA-Leti, I would like to acknowledge the PTA (Plateforme de Technologie Amont) and the CIME (Centre Interuniversitaire de MicroElectrnoique), which offered me the possibility and necessary formations to work on their equipment. A special thanks goes to all the members of those two clean rooms which assisted me during my PhD and provided with invaluable knowledge, help and advice.

I would also like to thank the III-V Lab which provided me with some very good quality material and services, which greatly contributed to the success of my work and my obtaining great results.

This section could not be complete without thanking Dr. Yvon CORDIER and Dr. Marie-Paule BESLAND which agreed to be my reviewers, and were very kind and comprehensive all throughout the correction process. Acknowledgments go as well to the other members of my jury, Mr. Farid MEDJOUB and Mr. Gaëtan TOULON, and its president Pr. Alain CAZARRÉ.

Last but not least, a special thanks goes to my family, friends and CEA co-PhD students who supported, encouraged and assisted me all along my PhD research. They have been a tremendous support during those years, and I consider myself very lucky to have them in my life. The last word goes to my companion, Julie RANDRIANARISOA, without whom I could never have come as far as I am now. Her love and infallible support is greatly responsible for me completing this PhD, and I will always be grateful for her being at my side.

So again, to all these great peoples and institutions : thank you very much!

## General Introduction

Throughout the  $20^{th}$  century, humanity has thrived like it never had before, mostly through the use of fossil fuels and their derivatives. Whether it be for transportation, energy production or synthetic products, most of the world and its industry as we know it now would not have been, and still could not be possible without the use of oil and gas. However, as we now entered the  $21^{st}$  century, we also realize the dire impacts this had on our environment. Greenhouse gas levels have never been as high as they are now, and  $CO_2$  emission has become one if not the major concern in ecology throughout the world. But despite the growing global awareness of the problem, energetic needs are constantly rising due to economic growth of emerging countries and world population growth, with International Energy Agency estimations predicting that electricity consumption throughout the world could rise by 75% in less than 25 years (according to Areva). And with the rapid decay of fossil fuels reserves, we could soon be confronted with one of the major challenges humanity has ever faced. As a consequence, innovation in the energy domain has become one of the main research focus this last years. The advent of solar and wind technology paved the way for new possibilities in terms of clean energy production, and hybrid or fully electrical technologies have recently made leaps in terms of performance and sustainability.

Parallel and directly linked to the development of those various "green" technologies, energy conversion has now become one of the cornerstones for the improvement of electrical performances and consumption. As electronic devices become more and more complicated, energy conversion systems have multiplied and are often the guarantors of an optimal functioning. Generally referred to as power electronics, they are most of the time constituted of semiconductors like power transistors, which can in turn be directly linked to losses in circuits. With more than 10% of the produced energy being lost in the conversion process [1], improving those systems has become mandatory for a better, cleverer and more economical way of managing energy.

Largely dominated by silicon based components, the semiconductor industry is now gradually faced with a growing need for evolution, particularly in the power industry. While they have greatly contributed towards circuits performance optimization, Si based technologies are now arriving at maturity and their further growth has become limited by the intrinsic properties of the material. As such, it becomes necessary for a new generation of components to appear in order to push back the limits defined by actual technology. As such, large band gap material appear as one of the go-to solutions, their physical properties largely surpassing the ones of silicon or this particular application. Recent years studies have notably been marked by the arrival of incredible like gallium nitride GaN and silicon carbide SiC. Furthermore, recent developments in heteroepitaxy of GaN on Si allowed to combine the efficiency of improved performance with low cost production on large scale wafers (200 mm). It thus marked a real rupture with silicon components and became a very serious candidate for future generations of power converters.

However, despite its appealing properties and general scientific consensus on its potential, GaN on Si technology is still being confronted with many challenges that hinder its developments and slows its market introduction. This is particularly true for high bias (>1000 V) and high current (> 100 A) applications where quality of the material and robustness of technology are primordial. It is precisely in this context that this Ph.D. is inscribed, through the study and development of one of the key technological steps that comes into play for the fabrication of a MIS-

HEMT (Metal Insulator Semiconductor - High Electron Mobility Transistor). The present work will be mostly focused on the insulating step of the process, with the main objective of improving the electrical behavior of the transistor through gate leakage reduction while reducing interface states density. This manuscript is the culmination of three years of studies and experimentation and is divided in four chapters.

**Chapter 1 :** This chapter will first focus on describing the properties of a power converter should have in order for them to respond to the needs and demands of the current market, and highlight why there is a need for wide band gap materials in today's industry. It will then assess the place of GaN in power electronics through the study of its properties, and expose the reasons why it is becoming a key player.

**Chapter 2**: Focused on the Metal Insulating Semiconductor on GaN, this second chapter will review the different equations responsible for the unique and peculiar behavior of transistors made on an AlGaN/GaN heterostructures. As it is the main subject of the present study, the major focus will then be on the introduction of the insulating layer and the impact it will have on the MIS-HEMT's electrical properties. Also, and though it was at first not intended to be realized during this Ph.D., the influence of the gate recess etching on the threshold voltage increase will also be described in the last part of the chapter.

**Chapter 3**: This chapter will describe all the different technological steps I put in place and performed during my Ph.D. First, I will describe the surface conditioning processes that were studied. In a second time, I will expose all the process flow that was used in order to achieve the completion of functional MIS-HEMT structures, through the creation of diodes and circular transistors in particular. Lastly, I will detail the optional process of recess etching below the gate that I could implement inside the devices' elaboration **Chapter 4**: This final chapter will be the heart of the present study, where the results of my work will be presented and commented upon. In a first part, surface treatments and their characterization will be the main topic, with an emphasis on the results obtained through X-ray Photo-electron Spectroscopy. The rest of the chapter will then review all the electrical results that were obtained through the study of Schottky gate devices and fully functional MIS-HEMT structures. Capacitance C(V) and gate current  $I_d(V_g)$  measurements will be at the center of those results. They will assess the impact of the insulating layer deposition method, how results evolve depending on its thickness, and how post deposition thermal treatment might have an influence. Last but not least, I will present how a partial or full gate recess etching impacted electrical properties and helped to achieve a normally-off architecture.

# GaN for power electronics : state of the art and context

## 1.1 Power electronics and devices

## 1.1.1 Needs and demands of the market, specifications, theory VS reality

The ever growing demand of energy is one of tomorrow's greatest challenge if we want to keep the standards as they are today. Despite our efforts, the demand for electricity keeps to increase, and is expected to do so more than any other resources in future years. With a growth of 2.5% each year, levels of demand and

production of electricity should be twice as large in 2013 as they were in 2006.

The technology using power electronics is the key to regulating energy flux between the power source and the devices. In every system needing electricity to operate, it is responsible for reliability, stability and efficiency of the way in which the energy is spent. And whether it be for personal computers and domestic appliances, or for transportation and heavy industry, global semiconductor market in this particular domain is accountable for more than 50 billions of dollars in 2010 alone. Optimization of power management requires components able to sustain high voltage and current levels, at high frequencies and high temperature, with low losses in conduction as well as commutation.

Power electronics is the technology that concerns energy conversion. With less than 50 years of existence, it still is a young technology but has known a great and rapid development in recent years, due to the fact that more than 15% of produced electrical energy needs some kind of conversion. It is a technology that is based on commutation electronics, and takes advantage of the properties of a perfect switch : it does not dissipate any energy, whether it is perfectly closed (null resistance, no bias between source and drain) or perfectly opened (infinite resistance, no current going through). When associated with different filtering elements, it is thus theoretically possible to modify voltage and/or current, without any losses. Unfortunately, reality does not match theory yet and losses are still unavoidable because of the physical components which are part of power switches. However, the increasing efficiency in the devices and the overall size, weight and cost reduction allowed the generalization of power electronics components in domains where losses must be kept to a minimum, in order to reduce heating and achieve high yield performances. The automotive market is a perfect example where such technology will play a key role in future developments. In the coming 20 years, it is expected that cars will evolve from fully thermal to fully electric while going through intermediate hybrid states. The energy management in these new kind of engines is becoming more and more challenging and will require sophisticated electronic modules such as power converters in order to sustain optimum functioning regimes.

#### 1.1.2 Limits of silicon

Today, silicon is the core material used in most semiconductor technologies. It is at the foundation of modern electronics as we know them and can be found in a large majority of components. But with the rapidly increasing demand in power electronics, the microelectronics industry is now confronted with the intrinsic limits of silicon.

As stated earlier, power components play the role of switches with two different states :

- an on-state, where specific resistance  $R_{ON}$  must be as low as possible. We sometimes use  $R_{ON} \cdot S$ , S being the active surface of the power component, in order to introduce a notion of volume and cost.

- an off-state, where the voltage with stand must be as high as possible until breakdown voltage  $V_{BD}$  is reached.

Both characteristics are closely related to the lowly doped layer (epitaxial layer in most cases), which plays a double role : it ensures the voltage withstand in the off-state, and has an important resistive effect in the on-state. We thus have the following relation :

$$R_{ON} \cdot S(\Omega \cdot cm^2) = \alpha \cdot V_{BD}^\beta \tag{1.1}$$

where  $\alpha$  and  $\beta$  are two positive and real constants. This equation defines the limits of silicon : the value of the specific on-state resistance cannot be inferior to a value related to the bias we want the power component to sustain.

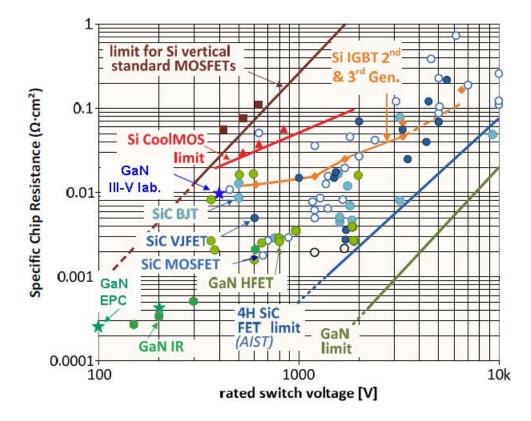

If we look at figure 1.1, we can see the silicon limits and how they fare comparatively to large band gap materials and different architectures.

FIGURE 1.1 – Specific chip resistance  $R_{on}$  in function of rated switch voltage for different materials.

We can see that there is a large zone where silicon components cannot grant the needed characteristics, even with complex architectures such as IGBTs for instance. And if we want to comply with the power increase, it has become necessary in silicon technology to increase the size of the components. However, this does not represent a viable solution since the size increase will lead to higher energy losses, especially in commutation, and that does not agree with the current market tendency where size reduction and high energy efficiency are of the utmost importance. It is thus capital to develop a new and innovative technology based on compatible materials for us to overcome those limitations.

#### 1.1.3 Wide band gap materials

In this context where silicon is no longer an option, the emergence of wide band gap materials is regarded as the most promising solution in the power electronics industry. With operating constraints such as high temperatures (300-700 K) and high voltage ( $\geq 600$  V), silicon carbide (SiC), gallium nitride (GaN) and diamond are the most promising candidates to date. Compared to silicon, they present the advantage of working on a large scale of temperatures, a high breakdown electric field and a high electron saturation velocity.

Having a large band gap (around 3 eV) will reduce the thermoionic carrier formation, which, if to high, can change the nature of the semiconductor. Those carriers are formed following an Arrhenius law,  $n = n_0 e^{-E_a/kT}$ , where  $E_a$  is the activation energy, k the Boltzmann constant and T the temperature. In the case of semiconductors, the activation energy is the gap energy  $E_g$ . This explains why large band gap materials are preferable for high temperature uses, since the higher  $E_g$  will be, the lower the influence of temperature becomes.

And furthermore, critical breakdown field in semi-conductor materials is directly related to their band gap energy [2, 3]. So the higher the band gap, the higher the breakdown field is, which allows these materials to have exceptional voltage withstands.

Table 1.1 shows the main electrical characteristics of conventional and wide band gap semiconductors.

|                                                                                                                                              | Conventional semiconductors |                    | Large band gap<br>semiconductors |                     |                      |                      |

|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------|----------------------------------|---------------------|----------------------|----------------------|

|                                                                                                                                              | Silicon                     | GaAs               | 6H-SiC                           | 4H-SiC              | GaN                  | Dia-<br>mond         |

| $\begin{array}{c} \text{Gap energy} \\ E_g \ (\text{eV}) \end{array}$                                                                        | 1.12                        | 1.43               | 3.03                             | 3.26                | 3.39                 | 5.45                 |

| Electron<br>mobility $\mu_n$<br>$(\text{cm}^2 \cdot \text{V}^{-1} \cdot \text{s}^{-1})$                                                      | 1450                        | 6500               | 850                              | 980                 | 1250                 | 2000                 |

| Hole mobility $\mu_p$<br>(cm <sup>2</sup> · V <sup>-1</sup> · s <sup>-1</sup> )                                                              | 450                         | 400                | 101                              | 115                 | 35                   | 2000                 |

| $\begin{array}{c} \text{Critical} \\ \text{breakdown} \\ \text{field } E_c \\ (\text{MV} \cdot \text{cm}^{-1}) \end{array}$                  | 0.3                         | 0.4                | 2.5                              | 3                   | 3.3                  | 10                   |

| Intrinsic carrier density $n_i$ (cm <sup>-3</sup> )                                                                                          | $1. \times 10^{10}$         | $2. \times 10^{6}$ | $2. \times 10^{-6}$              | $8. \times 10^{-9}$ | $1. \times 10^{-10}$ | $1. \times 10^{-27}$ |

| $\begin{array}{c} \text{Thermal} \\ \text{conductivity } \lambda \\ (W \cdot \text{cm}^{-1} \cdot \text{K}^{-1}) \end{array}$                | 1.412                       | 0.455              | 4.9                              | 4.9                 | 1.3                  | 20                   |

| Relative permitivity $\epsilon_r$                                                                                                            | 11.8                        | 13.1               | 9.66                             | 10.1                | 9.5                  | 5.7                  |

| $ \begin{array}{c} \mbox{Electron} \\ \mbox{saturation} \\ \mbox{velocity } \nu_{sat} \\ (\times 10^7 \ {\rm cm \cdot s^{-1}}) \end{array} $ | 1                           | 1                  | 2                                | 2                   | 2.2                  | 2.7                  |

TABLE 1.1 – Electrical properties of conventional and wide band gap semiconductors.

Of all the different materials, diamond exhibits the best overall properties for power applications, followed by gallium nitride which is also a good candidate for optoelectronics and power due to its direct gap and its breakdown electric field 10 times that of silicon. However, it has the smallest thermal conductivity, compared to the other materials.

With three different crystalline structures available, silicon carbide is also a good candidate for power electronics. With an hexagonal atomic structure, 4H-SiC and 6H-SiC are only differing by their mobility which is isotropic in the first and super to the anysotropic one in the last. 3C-SiC has the highest electron mobility and saturation velocity because of reduced phonon scattering resulting from the higher symmetry of its cubic atomic structure.

All those materials have a higher breakdown field compared to silicon and are able to sustain a voltage roughly 10 times superior. Consequently, for the same voltage withstand, a component made from wide band gap material can be made with a thickness 10 times inferior, or with a doping a 100 times higher in the drift section (lowly doped layer) than that of a typical  $PN^-$  junction. For this typical kind of junction, the breakdown voltage is directly related to the critical breakdown electric field following this relation :

$$V_{BD}(V) = \frac{\epsilon_0 \cdot \epsilon_r \cdot E_c^2}{2 \cdot q \cdot N_d} \tag{1.2}$$

where  $\epsilon_0$  and  $\epsilon_r$  are respectively the void and the semiconductor permittivity, q is the electron elementary charge,  $N_d$  the doping level in the N<sup>-</sup> region and  $E_c$  the critical breakdown field.

Specific on resistance can be given by this equation [4]:

$$R_{ON} \cdot S(\Omega \cdot cm^2) = \frac{27 \cdot V_{BD}^2}{8 \cdot \epsilon_0 \cdot \epsilon_r \cdot \mu_n \cdot E_c^2}$$

(1.3)

where  $\mu_n$  is the electron mobility.

Figure 1.2 shows the superiority of wide band gap materials overs silicon.

FIGURE  $1.2 - R_{on}$  versus breakdown voltage for Si, SiC and GaN, with their respective limit[5].

For a unipolar component presenting specific on-resistance below 1  $\Omega \cdot \text{cm}^2$ , limits of silicon is around 1 kV whereas wide band gap semiconductors allow the fabrication of components able to sustain more than 10 kV. For advanced power applications, only those materials are able to cope with the needed specifications as can be seen in figure 1.1).

Again, diamond is the material presenting the best electrical and thermal properties. With its low intrinsic carrier concentration, it is thus able to sustain high temperatures. However, its fabrication process is still at an early stage and conditions to achieve the production of diamond are still hard to meet. Furthermore, if we limit ourselves to the previous equations, we do not take into account technological aspects which can have an important role, such as changing the mobility through the use of doping, which is a very difficult process to implement in diamond.

Compared to diamond and GaN, SiC is the material presenting the most advanced technology, with actual power devices being commercialized. The JFET on SiC transistor is right now the most advanced power switch, being able to perform at temperatures up to 300 °C. However, the high price of large SiC diameter substrates and associated epitaxies (around a 100 times higher than silicon) makes it a debatable solution in terms of economical concerns.

## 1.1.4 Figures of merit of semiconductors for power application

In order to compare the possible power electonics performance of different materials, some commonly known figure of merit are liste in Table 1.2. The numbers in this table have been normalized in repect to Si, and le larger the number, the better the material's performance in the corresponding category. We can notice that SiC polytypes and GaN have similar figures of merit, which implies similar performances. Diamond's figure of merit are at least 40 to 50 times more than any other semiconductor in the table.

| Material | Si  | GaAs | 6H-SIC | 4H-SiC | GaN    | Diamond   |

|----------|-----|------|--------|--------|--------|-----------|

| JFM      | 1.0 | 1.8  | 277.8  | 215.1  | 215.1  | 81,000    |

| BFM      | 1.0 | 14.8 | 125.3  | 223.1  | 186.7  | 25,106    |

| FSFM     | 1.0 | 11.4 | 30.5   | 61.2   | 65.0   | 3,595     |

| BSFM     | 1.0 | 1.6  | 13.1   | 12.9   | 52.5   | 2,402     |

| FPFM     | 1.0 | 3.6  | 48.3   | 56.0   | 30.4   | 1,476     |

| FTFM     | 1.0 | 40.7 | 1470.5 | 3424.8 | 1973.6 | 5,304,459 |

| BPFM     | 1.0 | 0.9  | 57.3   | 35.4   | 10.7   | 594       |

| BTFM     | 1.0 | 1.4  | 748.9  | 458.1  | 560.5  | 1,246,711 |

TABLE 1.2 – Main figure of merit for wide bandgap semiconductors compared with Si [6]

**JFM** Johnson's figure of merit is a measure of the ultimate high frequency capability of the material. More specifically, it is the product of the charge carrier saturation velocity in the material and the electric breakdown field under same conditions, first proposed by A. Johnson of RCA in 1965.

$$JFM = \frac{v_{sat}E_{BD}}{2\Pi} \tag{1.4}$$

where  $v_{sat}$  is the saturation velocity and  $E_{BD}$  is the electric field at which impact ionization initiates breakdown. Unfortunately, this figure of merit is difficult to determine experimentally as both  $v_{sat}$  and  $E_{BD}$  are intrinsic properties of a device, although easily found from simulation.

**BFM** Baliga's figure of merit is a measure of the specific on-resistance of the drift region of a vertical FET [7]. The BFM is useful in order to compare different semiconductor materials in high power voltage applications. It takes into account the barriers mobility and the dielectric permittivity of the material, as well as its critical electric field. It is expressed as :

$$BFM = \varepsilon_r \mu_n E_c^3 \tag{1.5}$$

It is mainly used for low frequency applications where conduction losses are predominant. It gives an appreciation in terms of voltage sustaining capability.

**FSFM** This is the FET switching speed figure of merit.

**BSFM** This is the bipolar switching speed figure of merit.

**FPFM** This is the FET power handling capacity figure of merit.

**FTFM** This is the FET power switching product figure of merit.

**BPFM** This is the bipolar power handling capacity figure of merit.

**BTFM** This is the bipolar switching product figure of merit.

## **1.2** Place of GaN in power electronics

Gallium was discovered in 1875 in France by Lecoq de Boisbaudran through the spectroscopy analysis of the zincblende from Pierrefitte in the French Pyrénées. Discovered around 1920, gallium nitride GaN crystal was first studied in the seventies but was then abandoned due to synthesis difficulties. In the nineties, under the influence of Japanese research groups, great progress was achieved in synthesizing the crystal. In 1997 and 2000, the development of a new prototype of MBE (molecular beam epitaxy) for Research and Development (R&D) allowed to grow nitride materials such as GaN. Because of its direct gap, it was first used for optoelectronic devices. Later on, its mobility and its high electron saturation velocity was used for designing HEMT (high electron mobility transistors) structures for high frequency (HF) application, and high temperature and high voltage applications were possible thanks to its high breakdown field. Until then, difficulties with high levels of P doping, resulting in device resistance being too important, represented a great challenge for HF bipolar technologies. However, work is still under progress in order to solve the inherent problems associated with technological process :

- GaN does not exist in liquid phase, which makes it difficult to obtain bulk GaN substrates. To date, epitaxy is realized on sapphire, silicon carbide or silicon substrates through metal organic chemical vapor deposition (MOCVD) in order to reduce fabrication costs. The choice of the substrate is based on a compromise between price, performances and device reliability;

- thermal oxidation, which is largely used in the silicon MOS and CMOS industry, is not possible on GaN due to the poor quality of the native oxide;

- P type doping is still a problem;

- despite the fact that it is now possible to produce high quality material on 200 mm silicon substrates, defect density remains very high;

Nowadays, silicon IGBTs and thyristors are the only available options for high voltage applications (1 - 10 kV), but it is expected that GaN unipolar components (HEMTs and MOSFETs) could replace those devices. This could lead to higher frequencies, higher voltages and higher temperatures of operation. However, GaN thermal conductivity is relatively low which poses problems to evacuate heat during conception of the devices. Nonetheless, it remains much cheaper than diamond and far more adapted to doping.

#### **1.2.1** Generalities on GaN and crystal structure

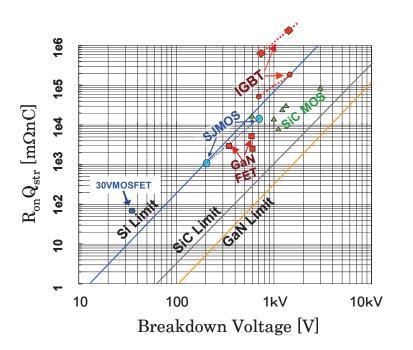

Gallium nitride (GaN) is part of the nitride III-N family which is composed of boron-nitride (BN), aluminum-nitride (AlN) and indium-nitride (InN). They can crystallize under a cubic or hexagonal form, but the hexagonal phase is the most stable we can achieve through standard growing conditions. Those two structures are zinc blende (cubic) and wurtzite (hexagonal) which can be seen in figure 1.3.

FIGURE 1.3 – GaN cubic Zinc Blende (left) and hexagonal Wurtzite (right) structure.

The latter is the one being used in laboratory for GaN layers epitaxy due to its metastable nature, which presents numerous crystalline properties suitable to the elaboration of heterojunctions. Table 1.3 shows the crystal parameters of both structures.

|                   | Cubic c-GaN                   | Hexagonal h-GaN                                                |

|-------------------|-------------------------------|----------------------------------------------------------------|

| Lattice parameter | $a_{300K} = 4.511 \text{\AA}$ | $a_{300K} = 3.188 \text{\AA}$<br>$a_{300K} = 5.185 \text{\AA}$ |

TABLE 1.3 – Lattice parameters for GaN crystalline structures.

The c/a ratio of the GaN lattice is very close to the  $\sqrt{8/3}$  theoretical value for a perfect hexagonal structure. We can thus assume that gallium atoms are in lowly distorted tetrahedral sites.

#### 1.2.2 GaN properties

#### **1.2.2.1** Electric properties

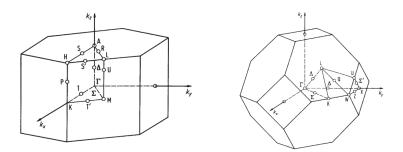

GaN is a semiconductor presenting a direct band gap, which means that the conduction band minimum ( $E_c$ ) and the valence band maximum ( $E_v$ ) are at an almost identical value on the diagram representing the energy E relatively to the wave vector k. For GaN, this point is located at the  $\Gamma$  point, center of the Brillouin zone (k = 0). The first Brillouin zones and the band structures in the major direction are represented in figure 1.4.

FIGURE 1.4 – GaN cubic Zinc Blende (left) and hexagonal Wurtzite (right) structure and their Brillouin zones.

Hexagonal and cubic structures have a band gap of 3.43 eV and 3.20 eV respectively at 300 K. Those values rise with temperatures, as described in the following equation :

$$E_g = E_0 - \frac{a \cdot T^2}{T+b} \tag{1.6}$$

where  $E_0 = 3.47$  eV, a = 0.599 meV.K<sup>-1</sup> and b = 880 K. This formula gives us a gap of 3.424 eV for hexagonal GaN at a 300 K temperature. This energy is to be compared to the 4H-SiC value of 3.240 eV and the Si value of 1.103 eV at 300 K obtained through the same calculation. This band gap energy is directly related to the breakdown field, which we will take into account later on. A wide band gap is generally associated to a low intrinsic carrier concentration, but non intentionally doped GaN is always n-type doped and electronic density can vary from  $10^{16}$ to  $10^{19}$  at.cm<sup>-3</sup> depending on the growing conditions. However those values are not very accurate since defects in the GaN structure will contribute to obtain higher values, while compensation phenomenons, located at deep energy levels, can contribute to the general lowering of these values. Hall measurements allow more precise and reliable way to obtain accurate values for the density and donor activation energy depending on temperature. The activation energy is related to the carrier concentration and given by the following equation :

$$E_a(N_d) = E_a(N_d = 0) - \delta \cdot N_d^{1/3}$$

(1.7)

where  $\delta$  is the shield constant in GaN (2.4x10<sup>-8</sup> eV.cm<sup>-1</sup>). For a doping level of  $3x10^{17}$  at.cm<sup>-3</sup>, we have an activation energy of 17 meV. Beyond  $3x10^{18}$  at.cm<sup>-3</sup>, activation energy becomes null and electronic density does not decrease with temperature, which corresponds to a metallic behavior (semiconductor beyond the Mott transition).

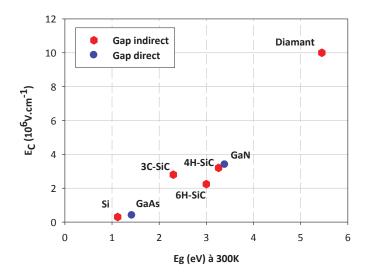

As stated earlier, another very important characteristic in power electronics is the breakdown electric field since this parameter will directly influence the maximum bias sustainable by the component. The higher its value, the easier it will be to elaborate devices with high doping levels and reduced size, with the beneficial properties such as a lower on-resistance. The theoretical breakdown field in GaN is compared to the one of other semiconductors in figure 1.5

FIGURE 1.5 – Critical breakdown fields for different semiconducting materials with a doping concentration of  $10^{16}$  cm<sup>-3</sup> depending on their gap (at 300 K)[8]

We can see that large band gap materials have superior breakdown field compared to materials such as silicon or gallium-arsenide. Diamond's critical breakdown field (around 10 MV.cm<sup>-1</sup> at 300 K) is theoretically a hundred times higher than silicon's, while at 3.4 MV.cm<sup>-1</sup>, gallium-nitride's is eleven times higher.

As stated previously, breakdown electric field and bang gap energy are tightly related by the following formula :

$$E_C \propto E_q^{3/2} \tag{1.8}$$

According to this relation, we can see that the higher the gap, the higher the theoretical breakdown field will be, as shown on figure 1.5. This also means that the critical field will decrease as temperature rises.

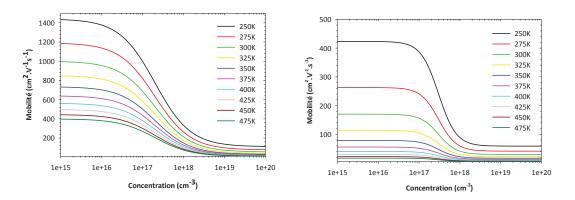

Last but not least of the electric parameters is the electron mobility. Under the influence of an electric field, charge carriers (electrons and holes) will migrate in the material, and the mean free path without interaction will set the movements of those carriers in the crystal. Generally wrote as  $\mu$ , the mobility will be under the direct influence of any modifications in the lattice, such as those induced by temperature rising or doping. Those dependency can be calculated by the following formula :

$$\mu = \mu_{min} \left(\frac{T}{300}\right)^{\beta} + \frac{\mu_{max} \left(\frac{T}{300}\right)^{\alpha} - \mu_{min} \left(\frac{T}{300}\right)^{\beta}}{1 + \left(\frac{N_{tot}}{N_{ref}}\right)^{\gamma}}$$

(1.9)

where T is the temperature, N the carrier concentration,  $\alpha$ ,  $\beta$  and  $\gamma$  parameters directly related to the semiconductor considered. Table 1.4 shows those values for GaN.

| Carriers  | $\mu_{min}$<br>(cm <sup>2</sup> .V <sup>-1</sup> .s <sup>-1</sup> ) | $\mu_{max}$ ) (cm <sup>2</sup> .V <sup>-1</sup> .s <sup>-1</sup> ) | $\stackrel{\rm N_{ref}}{\rm (cm^{-3})}$ | α  | β    | $\gamma$ |

|-----------|---------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------|----|------|----------|

| Electrons | 55                                                                  | 1000                                                               | $2x10^{17}$                             | -2 | -3.8 | 1        |

| Holes     | 30                                                                  | 170                                                                | $3x10^{17}$                             | -5 | -3.7 | 2        |

TABLE 1.4 – Minimum and maximum carrier mobility in GaN and associated calculation parameters [8].

If we now look at figure 1.6, we can trace the evolution of the electron and hole mobility for temperature ranging from 150 K to 475 K for different carrier concentration.

The first thing we can notice here is that mobility will decrease inversely proportional to the doping of the semiconductor. For a low concentration, we can also see that temperature has a large impact on mobility. For a carrier density around  $10^{16}$  cm<sup>-3</sup>, GaN mobility is around 900 cm<sup>2</sup>.V<sup>-1</sup>.s<sup>-1</sup> at 300 K, which is very similar to the one of 3C-SiC. However, hole mobility is around 170 cm<sup>2</sup>.V<sup>-1</sup>.s<sup>-1</sup>, which is 4 times more important than in 3C-SiC, but also 4 times lower than silicon's.

FIGURE 1.6 – Electron (left) and hole (right) mobility depending on carrier concentration as calculated using equation 1.8.

| Semiconductor | Electron mobility<br>( $cm^2.V^{-1}.s^{-1}$ ) at<br>300K | Hole mobility<br>$(cm^2.V^{-1}.s^{-1})$ at<br>300K |

|---------------|----------------------------------------------------------|----------------------------------------------------|

| GaN           | 900                                                      | 170                                                |

| 3C-SiC        | 900                                                      | 40                                                 |

| 4H-siC        | 750                                                      | 115                                                |

| Si            | 1360                                                     | 600                                                |

| GaAs          | 8500                                                     | 400                                                |

Those values are reported in Table 1.5

TABLE 1.5 – Carrier mobility in semiconductors at 300K.

The main difference between the mobility in GaAs and GaN is related to the difference in the effective mass of the carriers, which is higher in GaN, but this apparent superiority of GaAs over GaN is not valid anymore under a high electric field. In fact, III-V semiconductors band structure is peculiar and under those conditions, the variation of mobility is non-linear and not continuously increasing as is the case in other semiconductors. At 200 kV/cm for GaN, there is an overspeed peak which induces a higher electron velocity. As a consequence, saturation velocity is reached a lot later, which is why GaN can be used at high voltages.

#### 1.2.2.2 Physico-chemical properties

One particular property of the GaN crystal, when growing along the 0001 direction (which is the most common) perpendicular to the c plane, is that it is polarized. And since the structure does not present any inversion center, (0001) and  $(000\overline{1})$  directions are not identical. In consequence, those two directions define different types of surface, which are the Ga(0001) face and the N(000 $\overline{1}$ ) face.

Associated to this macroscopic polarization comes a piezoelectric polarization. Though the origin and orientation of both polarizations are identical, the direction of the piezoelectric one changes depending on the strains in the epitaxial layer.

The electric field generated by the global polarity could be problematic for optoelectronic devices since the recombination of carriers in quantum wells will diminish, thus lowering the LEDs efficiency. However for FETs (Field Effect Transistors) and HEMTs (High Electron Mobility Transistors) architectures, the high electric field will be highly beneficial, especially for the formation of a 2D electron gas on which we will come back later on. Regarding fabrication processes, the different nature in the faces will influence the behavior of GaN regarding thermal treatments, cleanings or metal adherence during deposition.

Regarding thermal properties, GaN thermal conductivity is  $1.3 \text{ W.K}^{-1}.\text{cm}^{-1}$  but depends on crystal quality. In a power electronics domain where large heat dissipation is necessary, it represents the capacity of the material to transfer a certain quantity of heat per time constant  $(1 \text{ W} = 1 \text{ J.s}^{-1})$  and per surface unity under a temperature gradient. Thermal conductivity of GaN is relatively close to the one of silicon  $(1.5 \text{ W.K}^{-1}.\text{cm}^{-1})$ . It is however 3 times higher than GaAs and sapphire conductivity, but 3 to 4 times lower than SiC depending on the polytype. Ideally, this value has to be as high as possible for power electronics since non dissipated heat will generate a rise in the component temperature, which translates into a lowering of the mobility and thus of the global electric performances of the components.

Another key parameter is the thermal dilatation coefficient which gives an infor-

mation on how the material will dilate or contract depending on the temperature. This is a parameter to keep in mind when choosing the base substrate material for growth during hetero-epitaxy. Table 1.6 gives the thermal values for different semiconductor materials.

|        | Thermal conductivity                                    |                                        | atation coefficient       |

|--------|---------------------------------------------------------|----------------------------------------|---------------------------|

|        | $(W.K^{-1}.cm^{-1})$ (x10 <sup>-6</sup> K <sup>-1</sup> |                                        | $0^{-6} \mathrm{K}^{-1})$ |

|        |                                                         | $\Delta \mathbf{a}/\mathbf{a} _{300K}$ | $\Delta a/a_{900K}$       |

| h-GaN  | 1.3                                                     | 5.59                                   | 5.11                      |

| Si     | 1.5                                                     | 2.6                                    | 4.2                       |

| 3C-SiC | 4.9                                                     | 3.8                                    | 4.8                       |

| GaAs   | 0.5                                                     | 5.73                                   | 6                         |

TABLE 1.6 – Theoretical values for thermal conductivity and thermal dilatation coefficient in semiconductors [9, 10, 11].

#### 1.2.3 The AlGaN/GaN heterostructure

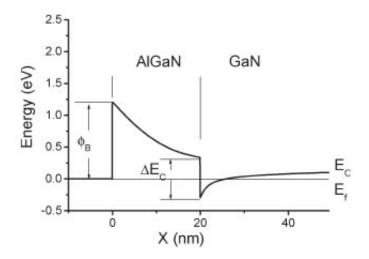

As stated earlier, one of the major applications in power devices for which GaN is considered among the best materials, is the creation of HEMT structures. Compared to traditional MESFET (Modulation Electron Surface Field Effect Transistor), the HEMT is able to bypass the problem of electron transportation in highly doped environment, which presents many restrictive phenomenons regarding electronic performances, especially for mobility. The main principle behind the high mobility transistor is to create a bidimensional electron gas (2DEG) using an AlGaN/GaN heterojunction, which band diagram is represented in figure 1.7.

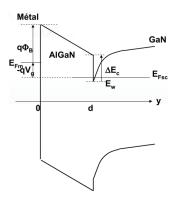

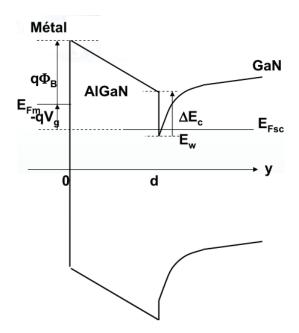

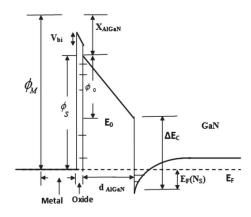

FIGURE 1.7 – Band diagram for the AlGaN/GaN heterostructure, with  $E_f$  the Fermi level energy,  $E_C$  the conduction band energy and  $\Phi_B$  the Schottky barrier height.  $\Delta_{EC}$  is the energy difference between the AlGaN and GaN respective conduction bands [12].

By choosing the right material, we can create a localized potential drop of the conduction band below the Fermi level and confine the carriers in a quantum well. The resulting potential and associated band diagram are thus directly related to the band gap of each semiconductor and their respective doping levels. The electron exchange between the two materials allow Fermi levels alignment and, as in a PN junction, a space charge appears.

The resulting well in GaN is a high electron density region with an excellent mobility, since it is free of any impurity. Electrons can move freely between source and drain along the heterojunction in a bidimensional space. Despite the restrictive aspect of the 2DEG, electron concentration in such structures can achieve very high levels, up to  $2 \times 10^{13}$  cm<sup>-2</sup>. It is important to notice that this value is referenced as a unit of surface and not volume.

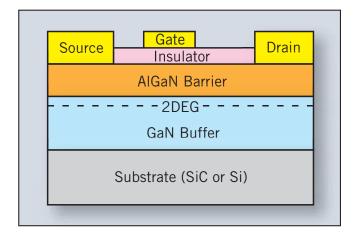

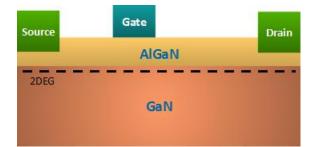

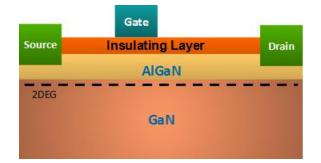

The HEMT structure represented in figure 2.2 presents a typical heterojunction between the GaN buffer layer and the AlGaN barrier. In this transistor, gate modulation is achieved by applying negative voltages which allows to deplete more or less the bidimensional channel between the gate and the drain. This kind of operation is referred to as depletion transistor or normally-on.

FIGURE 1.8 – Schematics of a typical AlGaN/GaN HEMT with and insulation layer.

#### 1.2.3.1 Spontaneous and piezoelectric polarization

One of the specifications of the HEMT structure based on GaN is that there is no need to dope the barrier layer, in our case AlGaN, in order to obtain a high electron density in the potential well (as opposed to GaAs for example). Electric fields are indeed already present in the AlGaN/GaN heterojunction and they will allow the formation of a high density bidimensional electron gas. Those electric fields are the consequence of 2 types of polarization : spontaneous and piezoelectric polarization.

**Spontaneous polarization** Without being under the influence of any mechanical constraint, the crystalline structure of GaN presents a spontaneous polarization. It is the result of the non-superposition of the barycenters of the negative and positive charges in the crystal (electrons and holes respectively). It is also present in AlGaN and generates an electric field around 3 MV/cm.

**Piezoelectric polarization** The piezoelectric polarization is, as its name indicates, explained by the piezoelectric effect : because of the lattice mismatch between the AlGaN and GaN layers, the resulting mechanical constraint induces and electric field of around 2 MV/cm. This value is influenced by the Al percentage and thus the induced deformation in the crystalline structure. The vectorial sum between both types of polarization in the AlGaN/GaN heterostructure results in the apparition of positive fixed charges at the interface on the AlGaN side, as shown in figure 1.9 :

FIGURE 1.9 – AlGaN/GaN structure piezoelectric polarization process

Supposing GaN is not constrained, it is possible to precisely calculate the surfacic charge density that is generated depending of the x in  $Al_xGa_{1-x}$  [13] :

$$|\sigma(x)| = |P_{PE}(Al_x Ga_{1-x}N) + P_{SP}(Al_x Ga_{1-x}N) - P_{SP}(GaN)|$$

(1.10)

$$|\sigma(x)| = |2\frac{a(0) - a(x)}{a(x)}(e_{31}(x) - e_{33}(x)\frac{C_{13}(x)}{C_{33}(x)}) + P_{SP}(x) - P_{SP}(0)|$$

(1.11)

with : - the lattice constant  $a(x) = (-0.077x + 3.189)10^{-10} \text{ m}$  - elastic constants  $C_{13}(x) = (5x + 103) \text{ GPa}$  and  $C_{33}(x) = (-32x + 405) \text{ GPa}$  - piezoelectric constants  $e_{13}(x) = (-0.11x - 4.49) \text{ C.m}^{-2}$  and  $e_{33}(x) = (0.73x - 0.73) \text{ C.m}^{-2}$  - spontaneous polarization  $P_{SP}(x) = (-0.052x - 0.029) \text{ C.m}^{-2}$

The electric field resulting from these positive charges will induce the accumulation of compensatory mobile negative charges, the electrons, at the interface on the GaN side. As a consequence, we can deduce that the maximum theoretical electron density in the channel will be limited by the polarization charge density  $\sigma(x)$  (assuming all the charges are compensated).

Using non-doped semiconductors combined with the quantum confinement phenomenon will reduce electronic interactions in order to maintain maximum electron mobility in the channel (2000 cm<sup>-2</sup>/V.s) highly superior to the mobility in doped bulk GaN. There resides all the HEMT interest for microwave applications.

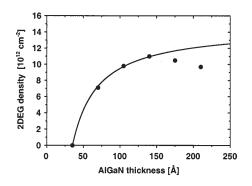

#### 1.2.3.2 Bidimensional electron channel

The 2D electron gas is located in the GaN region of the AlGaN/GaN interface. As stated earlier, it is achieved through the heterojunction between AlGaN and GaN, giving birth to a high surface density of electrons. The density of carriers in the 2DEG is subject to changes depending on the growth conditions, namely the Al content. The best way to increase it is to put more aluminum in the AlGaN barrier layer. However, beyond 30% of Al, the channel resistance increases significantly due to a diffusion of the alloy or interface roughness. Furthermore, the gate leakage current may increase as well with the Al concentration, which could lead to premature gate breakdown. The introduction of an AlN layer between AlGaN and GaN can counterbalance those effects , but will also generate instabilities at the gate contact level[14]. It has indeed been reported that gate transistor with an AlN layer is unstable through direct polarization after a current stress of 5 mA/mm, whereas AlN free transistors were able to sustain 100 mA/mm without instability [15]. Those perturbations are attributed to a high barrier height sensibility regarding the AlN thickness. A little variation of the AlN thickness may generate high currents locally when a small direct polarization is applied to the gate. The control of the AlN layer is thus capital if we want to achieve reliable structures for power devices.

The creation of an electron channel in the GaN layer is due to the formation of a potential well at the AlGaN/GaN interface. In order to understand his phenomenon, it is necessary to study the band structure at the AlGaN/GaN heterojunction. At the junction of 2 semiconductors, an electron diffusion will take place and, because of the difference in electronic affinity between the 2 materials, the electrons in AlGaN have a larger potential energy than those in GaN. The free electrons in AlGaN will thus spread towards GaN and accumulate at the interface. This diffusion will stop once thermodynamical equilibrium is achieved, that is to say when the Fermi levels of both materials are aligned.

$$E_{FAlGaN} = E_{FGaN} \tag{1.12}$$

As shown in figure 1.10, a discontinuity of the conduction band and the Al-GaN/GaN interface appears and provokes the formation of a triangular potential well in GaN because of the band curving, with or without achieving the equilibrium state. Carriers will then accumulate in this well and will be responsible for the conduction phenomenon in the transistor. Since they are confined on a very

small thickness, the electrons will form the so-called 2D electron gas which is the transistor's channel. Under the influence of an electric field, electrons will transit through this channel from the source to the drain of the transistor.

FIGURE 1.10 – AlGaN/GaN heterojunction.

Once the device is realized, the transistor effect will be assured by the Schottky gate contact : by applying a negative voltage on the gate, the space charge region at the metal/semiconductor junction will rise, and beyond a certain value, a diminution of the electrons concentration in the channel will occur. The transistor presents a "Normally-ON" behavior, which means it conducts current when no gate voltage is applied.

The discontinuity in the conduction band represents around 70% of the forbidden gap energy difference between the 2 materials and is directly related to the aluminum content of the AlGaN layer [13].

$$\Delta E_C = 0.7 [E_q(x) - E_q(0) \tag{1.13}$$

where :

$$E_g(x) = x \cdot E_g(AlN) + (1-x) \cdot E_g(GaN) - x \cdot (1-x)1.0eVs$$

(1.14)

$$E_g(x) = x \cdot 6.13eV + (1-x) \cdot 3.42eV - x \cdot (1-x)1.0eVs \tag{1.15}$$

#### **1.2.4** Models and formation mechanisms

While it is admitted that this electrical compensation phenomenon is at the origin of the 2D electron gas formation, its creation mechanisms are still poorly known, especially when it comes to the origin of the electrons. The most commonly admitted hypothesis is of a high charge density at the AlGaN barrier surface which neutralizes polarization charges and is the source of the electron gas. Multiple studies have been conducted in order to determine the natures of those surface states and different models have been investigated.

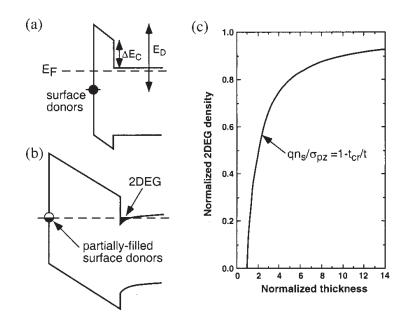

First model: single donor level In this particular model, we only consider one state of surface energy  $E_D$  below the conduction band [16]. This state is considered as a donor state : electrically neutral when occupied, and positively charged when it has lost its electron. If the level is deep enough, it will be positioned initially under the Fermi level and the 2D gas will be empty :  $n_{SURF} = n_S = 0$  ( $n_S$  being the surface charge density in the 2DEG). While increasing the barrier thickness, the surface potential will rise due to the constant polarization electric field. Upon reaching a critical thickness  $t_{CR}$ , the donor level will reach the Fermi level and electrons will start to migrate from the occupied states of the surface to the empty states in the well in order to create the 2DEG. Upon doing so, the positive surface states will compensate the negative polarization charges at the surface and the electrons in the 2DEG will neutralize the positive charges at the interface. As long as all the surface states are not empty, the surface barrier height remains constant  $(E_F = E_D)$ . This is what is called "Fermi level pinning" and is illustrated in figure 1.11. More electrons will migrate when the AlGaN increases and as such, the global electric field will tend to decrease.

FIGURE 1.11 – Energy diagram of the AlGaN/GaN illustrating the one donor surface level model where the AlGaN thickness is (a) inferior and (b) superior to the critical thickness. (c) is the 2D electron density calculation depending on the AlGaN barrier thickness, for a one donor level model [16].

The Poisson equation allows to calculate the critical thickness  $t_{CR}$ :

$$t_{CR} = \frac{(E_D - \Delta E_C) \cdot \epsilon}{q \cdot \sigma} \tag{1.16}$$

where q is the elementary charge and  $\sigma$  the polarization charges.

Supposing every electron coming form the AlGaN surface compensates a polarization charge at the AlGaN/GaN interface, we can deduce the following relation :

$$Q = \sigma - n_S \tag{1.17}$$

with Q the polarization charges which are not compensated by the electrons contributing to the electric field.

But since the electric field is directly related to the sum of the electric charges at the interface, we can precisely calculate the electron density of the 2DEG depending on the AlGaN electric field and the layer's thickness :

$$n_S = \frac{\sigma}{q} - \frac{\epsilon}{dq^2} (E_D + E_F - \Delta E_C) \tag{1.18}$$

where d is the AlGaN barrier thickness and  $E_F$  the Fermi energy given by [13] :

$$E_F = E_0 + \frac{\pi h^2}{m^*} n_S \tag{1.19}$$

where  $E_0$  is the energy of the first level formed in the quantum well between the 2 semiconductors :

$$E_0 = \left(\frac{9\pi h q^2}{8\epsilon_0 \sqrt{8m^*}} \frac{n_s}{\epsilon}\right)^{2/3}$$

(1.20)

If we neglect the rise of the Fermi level in the channel, the 2DEG becomes :

$$qn_S = \sigma(1 - \frac{t_{CR}}{t}) \tag{1.21}$$

As we can see in figure 1.12, the density measurements done by Hall effect (black dots) tend to confirm the theory for low thicknesses. We can see the apparition of the 2DEG at 35 Å which allows us to estimate the surface donor energy at  $E_D = 1.65$  eV. The fall of the  $n_S$  after 150Å can presuppose a relaxation of the constraints in AlGaN for superior thicknesses.

FIGURE 1.12 – Room temperature 2DEG density measured by Hall effect as a function of  $Al_{0.34}Ga_{0.64}N$  barrier thickness [16].

Theoretically, there is a saturation of the 2D electron gas density for important AlGaN thicknesses. The electric field at the interface will tend to decrease as long as the thickness increases, and will become null when all the polarization charges are neutralized. This explains the asymptotic behavior.

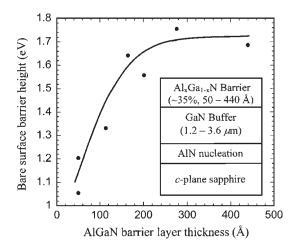

Second model : donor state distribution at the surface Even if the previous model works well, it has been contradicted by multiple studies [17, 18], particularly regarding the surface barrier height at the AlGaN barrier. The published results that we can see in figure 1.13 indeed showed that the surface barrier height decreases when the AlGaN thickness rises, which is incompatible with the one donor state model.

FIGURE 1.13 – Variation of the AlGaN surface barrier height depending on the AlGaN layer thickness [18]

Starting from this observation, we can assume that the surface states are distributed in the material gap. We thus consider a critical barrier height  $\Phi_C$  (potential between the conduction band and the highest occupied surface state) and a constant surface states density  $n_0$ . Upon increasing the barrier thickness and if  $n_0$ is low enough, the barrier height at the surface will necessarily increase in order to allow the transition of more electrons to the 2DEG. All the surface states which height is inferior to the barrier's  $\Phi_S$  will as such contribute to the formation of the 2DEG by losing their electron, as shown in figure 1.14 and the following equation :

$$n_{SURF} = n_S = n_0(\Phi_S - \Phi_C) \tag{1.22}$$

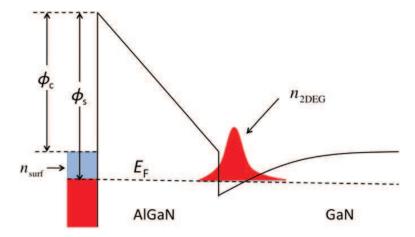

FIGURE 1.14 – Energy for the AlGaN/GaN heterostructure illustrating the electron transfer between the surface states and the 2DEG at the AlGaN/GaN interface [19].

This model is very close to the previous one, except that the barrier height  $\Phi_S$  is modified with the AlGaN thickness. The formula for the electron density in the 2DEG is similar, but the donor state energy  $E_D$  is replaced by the surface potential  $\Phi_S$ , giving the following equation :

$$n_S = \frac{\sigma}{q} - \frac{\epsilon}{da^2} (\Phi_S + E_F - \Delta E_C) \tag{1.23}$$

The variations of  $\Phi_S$  in function of the thickness d are directly related to the states density  $n_0$ : the lower  $n_0$  is, the more important the variations of  $\Phi_S$  will be. If the states density of surface donors is high enough, the electrons transfer from the surface to the 2DEG will only have a slight influence on the Fermi level. As such, we are in the same configuration as in the first model with only one donor state, assuming the hypothesis that  $E_D = q\Phi_C$  and that the surface states density is infinite.

However, multiple studies have shown noticeable differences regarding  $n_0$ ,  $\Phi_C$ and  $\Delta \Phi$  (barrier height elevation) of the measured donor states at the surface, as can be seen in table 1.7. Those variations can be attributed to the different experience conditions, particularly if we take AlGaN oxides into account. Different studies [20, 21] have shown that oxidation has an influence on the surface properties. Depending on the type of reconstruction with the oxygen atoms, the state density as well as the energy levels of the highest occupied state are modified, and this will have a direct influence on the formation of the 2D electron gas.

| Source                 | $n_0 (cm^{-2}.eV^{-1})$ | $\Phi_C (eV)$ | $\Delta \Phi \ (eV)$ |

|------------------------|-------------------------|---------------|----------------------|

| Ibbeston et al.[16]    | $\infty$                | 1.65          | 0                    |

| Koley et al.[18]       | $1.6 \text{ x} 10^{13}$ | 1.0           | 0.8                  |

| Higashiwaki et al.[20] | $4 - 6 \ge 10^{12}$     | 1.0           | 1.5                  |

| Gordon et al.[19]      | $< 10^{13}$             | 1.0           | 1.3                  |

TABLE 1.7 – Parameters differences between different studies

#### 1.3 Context of Ph.D.

As stated at the beginning of this work, the demand regarding power devices is in a large expansion and is expected to expand even further in the years to come. Compared to the silicon industry, gallium-nitride technology is still at its beginning and what we know so far about it is probably just the tip of the iceberg. However, in an energy driven economical context, the HEMT structure represents a very promising solution for achieving high power and frequency switching devices. But even though theory predicts high performances for AlGaN/GaN heterostructures, we are still very dependent on material quality and process steps. As stated earlier, GaN epitaxy is complicated, and there are still a lot of problems preventing us for achieving performances as high as we would like. Whether it be defects, doping or device architecture challenges, every step in the elaboration process brings its fair share of difficulties, and each one of them must be addressed separately.

This works takes place in the context of the creation of GaN on silicon industry oriented device processing chain in the LC2E laboratory. Using the already present CMOS industry equipment of the CEA-Leti, the objective here is to achieve high performance devices for power applications with cost reduction through the use of large diameter 200 mm silicon substrates.

In terms of device technology and considering its maturity on silicon, the Schottky gate structure has been studied intensively and already yielded some good results. However, for it to be reliable, a very good control of the different creation processes is necessary. Even though it has proven to be a very robust structure, it still presents some defects, particularly in terms of gate leakage current, and its performances are very sensitive to material quality. The natural way to reduce this hindrance would be, as in the silicon industry, to turn to the use of an intermediate insulating layer between the gate and the material to achieve MOS-like devices.

This is precisely where this work will be integrated. From the choice of the insulator to its electrical testing, going through deposition, characterization, preor post-processing and material conditioning, it was my work as a Ph.D student in CEA-Leti to address the different challenges in order to create a reliable MIS-HEMT device (MIS standing for Metal Insulator Semiconductor). Most of the research was carried on wafers produced at CEA-Leti, but also on some samples coming from the III-V Lab in Paris.

The main objective in the elaboration of a MIS-HEMT during my work was to address one of the major problematic in power device elaboration, which is to suppress or at least greatly reduce the gate-leakage current. As the continuous down-scaling of the device size has lead to very thin gate oxides, the leakage current that can flow from the channel to the gate comes into the order of the subthreshold leakage current and the gate cannot be considered as an ideally insulated electrode anymore. This affects the circuit functionality and increases the standby power consumption due to the static gate current. Another key aspect directly following, is to elaborate a sufficiently robust and optimal process in order to better achieve a normally-off device. Ultimately, and mainly for safety reasons, it is preferable to apply a positive gate bias in order to open the device channel, instead of applying a negative bias in order to close it.

While introducing a gate dielectric is a very good solution towards solving the above mentioned problems, it also comes with its limitations and constraints typically found in CMOS structures in general. As we will see in the next chapter, we also have to take into account the potential barrier height of the dielectric and the critical electric field.

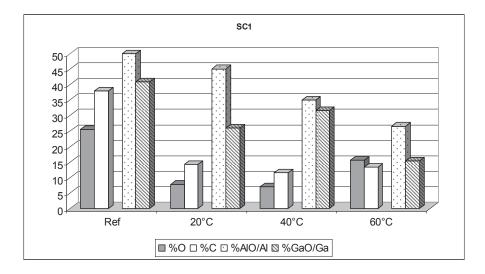

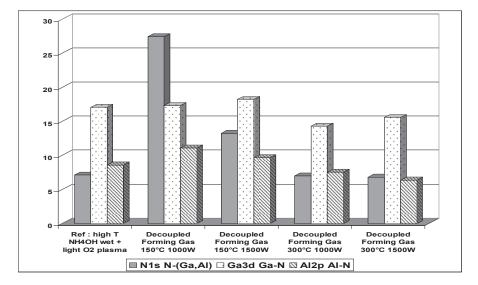

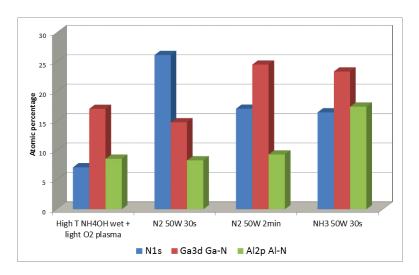

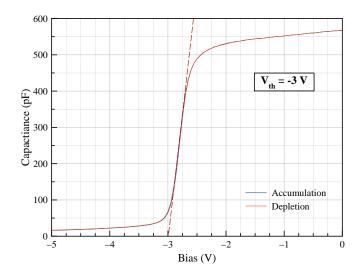

#### 1.4 Conclusion