# Flexible substrate technology for millimeter wave applications

Zhening Yang

#### ▶ To cite this version:

Zhening Yang. Flexible substrate technology for millimeter wave applications. Electronics. INSA de Toulouse, 2016. English. NNT: 2016ISAT0023. tel-01499425v2

### HAL Id: tel-01499425 https://laas.hal.science/tel-01499425v2

Submitted on 12 Jun 2017

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# **THÈSE**

#### En vue de l'obtention du

### DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE

Délivré par :

Institut National des Sciences Appliquées de Toulouse (INSA de Toulouse)

# Présentée et soutenue par : Zhening YANG

le lundi 19 décembre 2016

Titre:

Flexible Substrate Technology For Millimeter Wave Applications

#### École doctorale et discipline ou spécialité:

ED GEET: Micro et Nanosystèmes

#### Unité de recherche :

LAAS-CNRS

#### Directeur/trice(s) de Thèse:

Daniela DRAGOMIRESCU, Professeur, INSA-Toulouse Alexandru TAKACS, Maître de Conférences, Université Paul Sabatier

#### Jury:

Raluca MULLER, Directeur de Recherche, IMT Bucharest (Rapporteur) George PAPAIOANNOU, Professeur, University of Athens (Rapporteur) Anthony GHIOTTO, Maître de Conférences, IMS-Bordeaux (Examinateur) Patrick PONS, Directeur de Recherche, LAAS-CNRS (Examinateur) Invité(s):

Alexandru MULLER, Directeur de Recherche, IMT Bucharest Samuel CHARLOT, Ingénieur, LAAS-CNRS

## **Table of Contents**

| List | of T        | l'ables                                         | 4    |

|------|-------------|-------------------------------------------------|------|

| List | of F        | Figures                                         | 5    |

| I.   | Gei         | neral introduction                              | . 11 |

| II.  | Sta         | ate of art of flexible electronics technology   | . 15 |

| Ι    | <b>I</b> .1 | Introduction to Wireless Sensors Network (WSN)  | . 15 |

| I    | I.2         | Introduction to flexible electronics            | .16  |

| I    | I.3         | Materials for flexible electronics              | .16  |

|      | II.3        | 3.1 Organic substrate materials                 | . 17 |

|      | II.3        | 3.2 Inorganic substrate materials               | . 19 |

| Ι    | <b>I</b> .4 | Fabrication technology for flexible electronics | .20  |

|      | II.4        | 4.1 Conventional technologies                   | .20  |

|      | II.4        | 4.2 Direct printing technologies                | .21  |

| I    | I.5         | Evolution of electronic packaging               | .25  |

|      | II.5        | 5.1 System on Chip (SoC)                        | .25  |

|      | II.5        | 5.2 Chip on Board (CoB)                         | .26  |

|      | II.5        | 5.3 MCM                                         | .27  |

|      | II.5        | 5.4 System in Package (SiP)                     | .28  |

|      | II.5        | 5.5 System on Package (SoP)                     | .29  |

|      | II.5        | 5.6 Package on Package (PoP)                    | .29  |

| ľ    | I.6         | Conclusion                                      | .30  |

| III. D        | Design and measurement of passive circuit elements on flexible substrate | 33 |

|---------------|--------------------------------------------------------------------------|----|

| III.1         | Theoretical background                                                   | 33 |

| III.          | 1.1 Reflection coefficient                                               | 33 |

| III.          | 1.2 Fundamental parameters of antenna                                    | 34 |

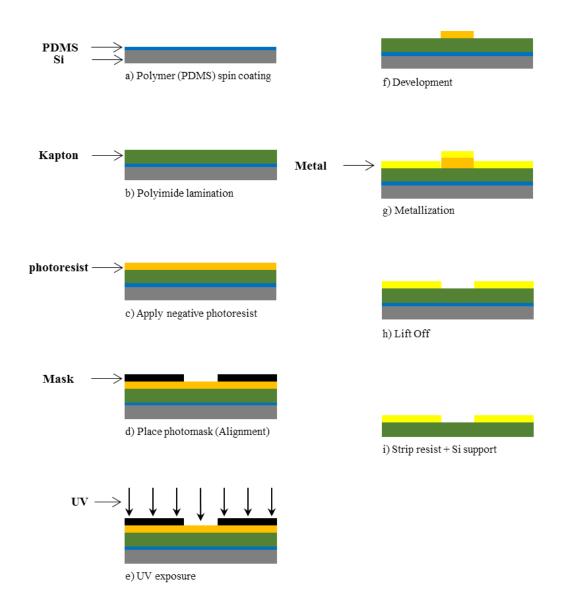

| III.1         | Technological process for flexible substrate                             | 35 |

| III.2         | RF characterization of Kapton                                            | 38 |

| III.          | 2.1 Ring resonator                                                       | 39 |

| III.3         | Antennas                                                                 | 41 |

| III.          | 3.1 Patch antenna                                                        | 41 |

| III.          | 3.2 Crossed-dipoles array antenna                                        | 45 |

| III.          | 3.3 Cross slot dipole antenna                                            | 50 |

| III.4         | Humidity test                                                            | 53 |

| III.5         | Conclusion                                                               | 55 |

| IV. T         | echnological process for passive elements on flexible substrate          | 57 |

| IV.1          | Introduction                                                             | 57 |

| IV.2          | Substrate preparation                                                    | 57 |

| IV.           | 2.1 PDMS layer deposition                                                | 57 |

| IV.           | 2.2 Kapton film preparation                                              | 59 |

| IV.3          | Implementation of circuits with electrical pattern on topside            | 60 |

| IV.4<br>backs | Implementation of circuits with electrical patterns on both topside ide  |    |

| IV.5          | Conclusion                                                               | 65 |

| V. Heterogeneous integration on flexible substrate |

|----------------------------------------------------|

| V.1 Introduction67                                 |

| V.2 IC packaging choice                            |

| V.2.1 Wire bonding vs flip chip67                  |

| V.2.2 Au stud bumping69                            |

| V.3 Assembly process                               |

| V.3.1 Reliability test                             |

| V.4 Bumping process by electroplating81            |

| V.4.1 Optimization of thick resist processing      |

| V.4.2 Electroplating process                       |

| V.4.1 Reliability test88                           |

| V.5 Conclusion93                                   |

| VI. General conclusions95                          |

| Bibliography97                                     |

| List of publications                               |

### **List of Tables**

| Table II.1: Comparative properties of organic substrates       | 19 |

|----------------------------------------------------------------|----|

| Table III.1: Resonant frequencies & quality factors            | 41 |

| Table III.2: Cross dipoles array antenna dimensions            | 46 |

| Table III.3: Parametric study of angle α effect on radiation   | 53 |

| Table III.4: Extracted dielectric constant and dielectric loss | 55 |

| Table V.1: Test plan of spin coating                           | 83 |

| Table V.2: Test plan of UV exposure duration                   | 84 |

## **List of Figures**

| Figure I.1: Structural health monitoring (SHM) systems arrayed in keay areas where              |

|-------------------------------------------------------------------------------------------------|

| loads are highest. Source: Airbus                                                               |

| Figure I.2: WSNs deployed on aircraft wings for real-time in-flight testing12                   |

| Figure I.3: Concept of the communicating nano-objects on flexible substrate12                   |

| Figure II.1: Process flow of the photolithography process [16]                                  |

| Figure II.2: Principle of screen printing[18]                                                   |

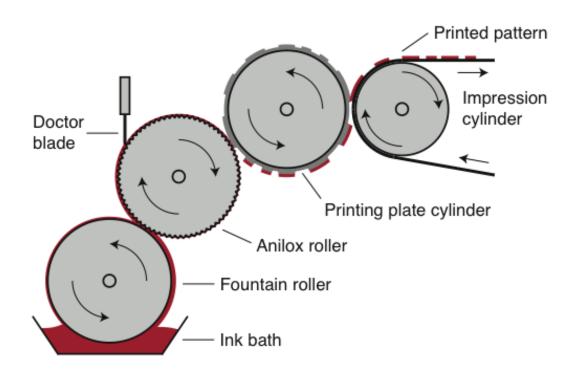

| Figure II.3: Principle of flexographic printing [21]23                                          |

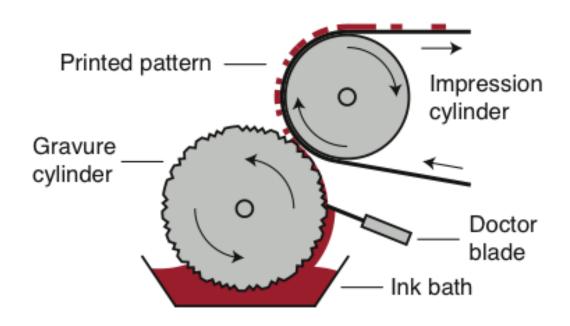

| Figure II.4: Principle of gravure printing[23]23                                                |

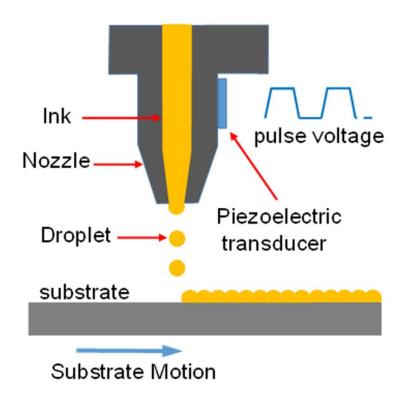

| Figure II.5: Principle of inkjet printing process [28].                                         |

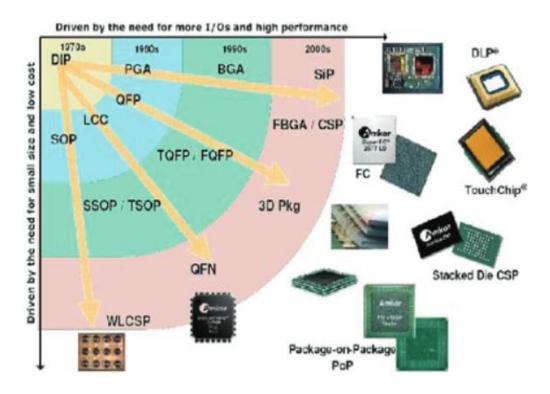

| Figure II.6: Development of packages in the last decades [29]25                                 |

| Figure II.7: Example of a SoC architecture (source: http://electronicdesign.com/)26             |

| Figure II.8: Two views of a CoB technology memory module (source: MB Electronique)              |

| Figure II.9: Example of MCM structure                                                           |

| Figure II.10: Example of SiP structure (SiP technology of 5 stacked chips), source: renesas.com |

| Figure II.11: Example of SoP structure [34]29                                                   |

| Figure II.12: Example of PoP structure, source: shinko.co.jp                                    |

| Figure II.13: Roadmap of system integration. [29]31                                             |

| Figure III.1: Transmitted and reflected currents and voltages                                   |

| Figure III.2: Dipole Antenna with 3D Radiation Pattern, Azimuth Plane Pattern and               |

| Elevation Plane Pattern, source Cisco                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------|

| Figure III.3: Shipley 360N Laminator                                                                                              |

| Figure III.4: EVG120 resist processing system                                                                                     |

| Figure III.5: Skin depth versus frequency, the horizontal lines show the selected metallization thickness                         |

| Figure III.6: Microstrip Patch Antenna, source emtalk.com                                                                         |

| Figure III.7: Maximum simulated antenna gain versus substrate thickness at 60 GHz                                                 |

| Figure III.8: Procedure for extraction of dielectric parameters                                                                   |

| Figure III.9: Ring resonator design40                                                                                             |

| Fig. III.10: Simulated and measured insertion loss of the ring resonator40                                                        |

| Figure III.11: (a) 60GHz GCPW feeding rectangular patch antenna; (b) Measurement setup; (c) Manufactured patch antenna on Kapton  |

| Figure III.12: Simulated and measured return loss of the patch antenna                                                            |

| Figure III.13: H-plane radiation patterns of the patch antenna at 60.3 GHz44                                                      |

| Fig. III.14: E-plane radiation patterns of the patch antenna at 60.3 GHz44                                                        |

| Figure III.15: Cross dipoles array antenna: top view of the layout (the bottom layout is represented in filled with green trellis |

| Figure III.16: Simulation model of Cross dipoles array antenna                                                                    |

| Figure III.17: Manufactured Cross dipoles array antenna                                                                           |

| Figure III.18: Simulated and measured return loss of the Ku band CDAA47                                                           |

| Fig. III.19: Simulated and measured return loss of the K band CDAA48                                                              |

| Fig. III.20: XOZ plane (phi = $0^{\circ}$ ) radiation patterns of the $K_u$ band CDAA at 17 GHz                                   |

| 48                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. III.21: YOZ plane (phi = $90^{\circ}$ ) radiation patterns of the $K_u$ band CDAA at 17 GHz                                                                                                                                                                   |

| Fig. III.22: XOZ plane (phi = $0^{\circ}$ ) radiation patterns of the K band CDAA at 22 GHz                                                                                                                                                                        |

| Fig. III.23: YOZ plane (phi = 90°) radiation patterns of the K band CDAA at 22 GHz                                                                                                                                                                                 |

| Fig. III.24: Design of crossed slot dipole antenna                                                                                                                                                                                                                 |

| Fig. III.25: Simulation model of slot dipole antenna                                                                                                                                                                                                               |

| Fig. III.26: Simulated return loss of the cross slot dipole antenna                                                                                                                                                                                                |

| Fig. III.27: Simulated (HFSS) radiation patterns in E-Plane and H-Plane at 60.2 GHz                                                                                                                                                                                |

| Figure III.28: Measured transmission coefficient of the ring resonator: initial state/0hm (continuous black line), measure after 12hr (red line, square dot), measure after 24hm (green line, circular dot), measure after 48hr (violet, dashed line)              |

| Figure III.29: Measured reflection coefficient of the microstrip patch antenna: initial state/0hr (continuous black line), measure after 12hr (red line, square dot), measure after 24hr (green line, circular dot), measure after 48hr (violet, dashed line)      |

| Figure III.30: Measured reflection coefficient of the crossed slot dipole antenna: initial state/0hr (continuous black line), measure after 12hr (red line, square dot), measure after 24hr (green line, circular dot), measure after 48hr (violet, dashed line)54 |

| Figure IV.1: Sylgard 184 part A and Part B                                                                                                                                                                                                                         |

| Figure IV.2: Vacuum desiccator                                                                                                                                                                                                                                     |

| Figure IV.3: Cut Kapton tape into a 4-inches wafer shape                                                                                                                                                                                                           |

| Figure IV.4: Fabrication sequence of wet etching process                                                                                                                                                                                                           |

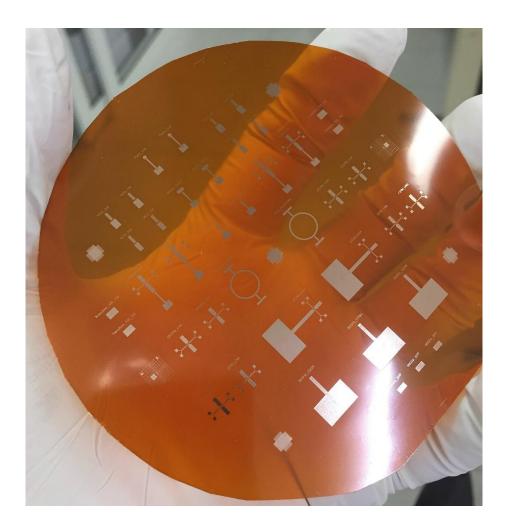

| Figure IV.5: Realized Kapton wafer with topside electrical pattern.                                                                                                                                                                                                                   | 62       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Figure IV.6: Fabrication sequence of lift-off process.                                                                                                                                                                                                                                | 63       |

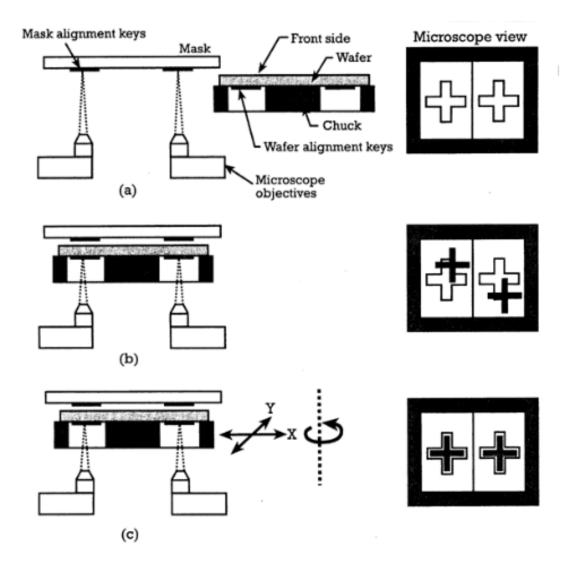

| Figure IV.7: Double-sided alignment scheme: (a) The image of mask alignment is electronically stored; (b) The alignment marks on the back side of the was brought in focus; (c) The position of the wafer is adjusted by the translation rotation to align with the stored image [45] | afer are |

| Figure IV.8: Realized Kapton wafer with double sided electrical patterns                                                                                                                                                                                                              | 65       |

| Figure V.1: Generic configuration of wire-bond packaging, source : [47]                                                                                                                                                                                                               | 67       |

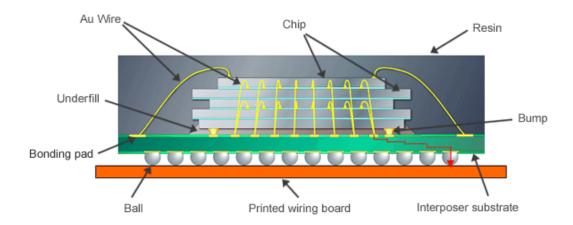

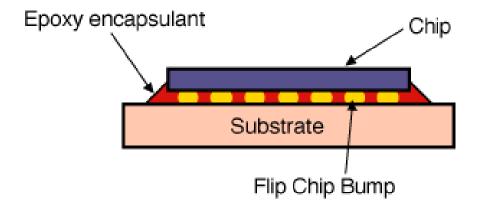

| Figure V.2: Generic configuration of flip chip packaging with underfill                                                                                                                                                                                                               | 68       |

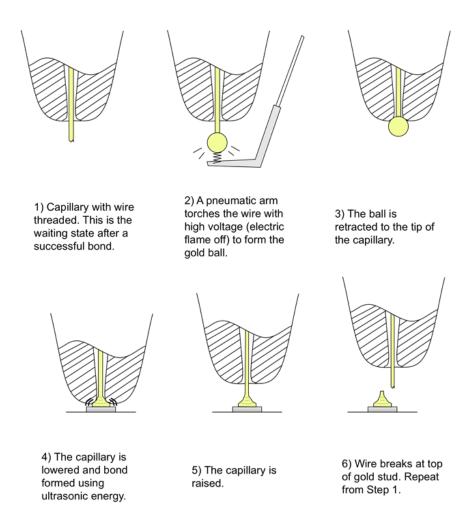

| Figure V.3: Gold stud bumping process, source: [51]                                                                                                                                                                                                                                   | 70       |

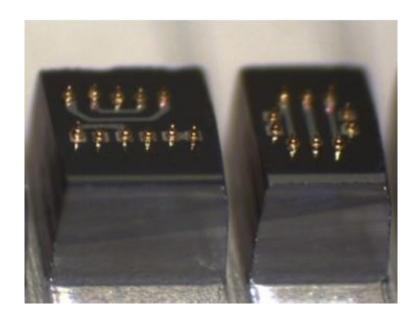

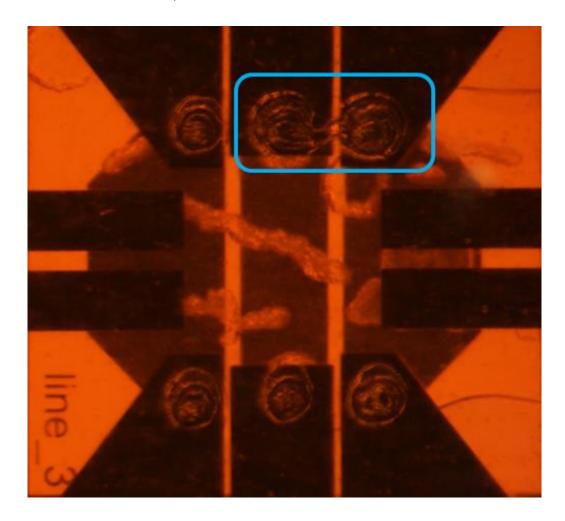

| Figure V.4: Gold stud bump realization on silicon dummy                                                                                                                                                                                                                               | 70       |

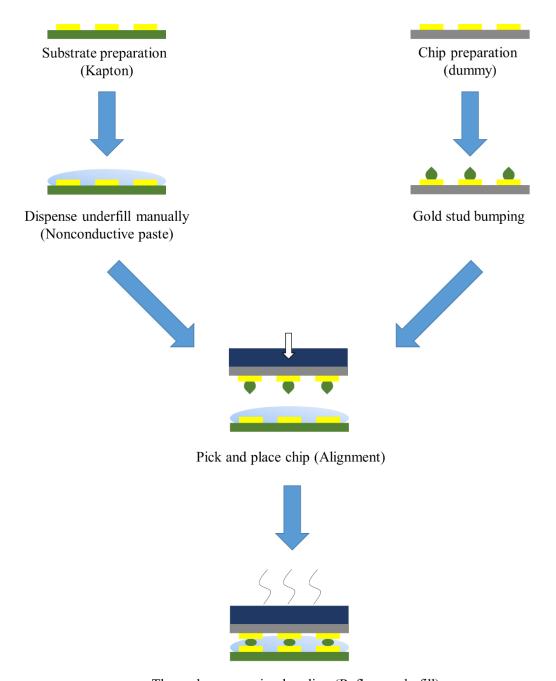

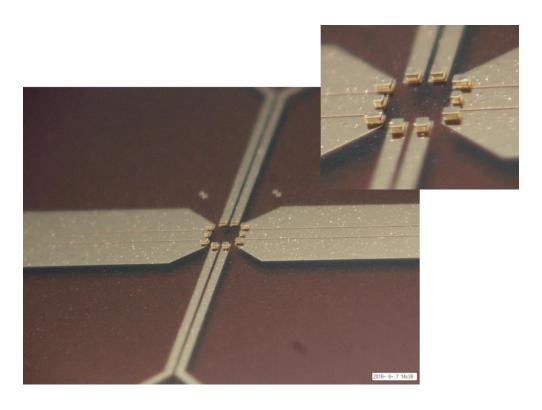

| Figure V.5: Process flow of flip chip                                                                                                                                                                                                                                                 | 71       |

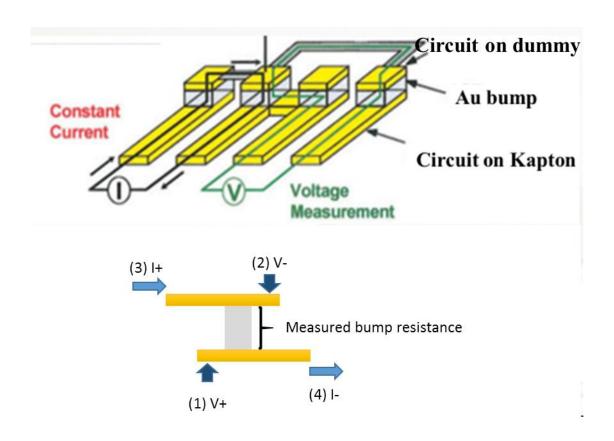

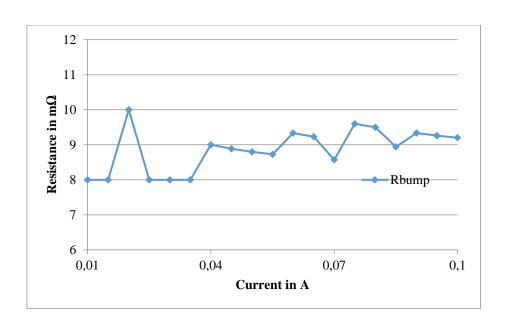

| Figure V.6: Four-point probe resistivity measurement                                                                                                                                                                                                                                  | 73       |

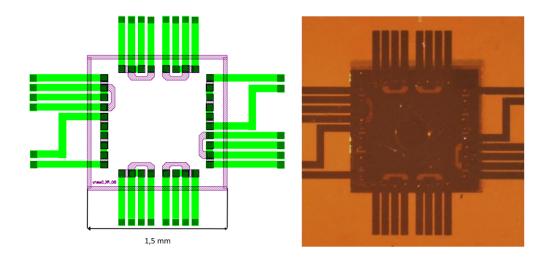

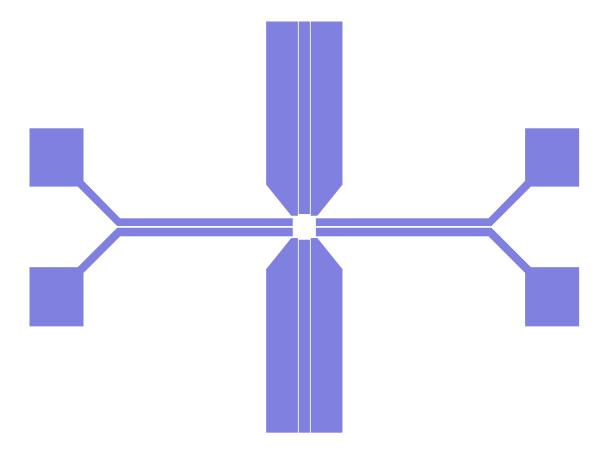

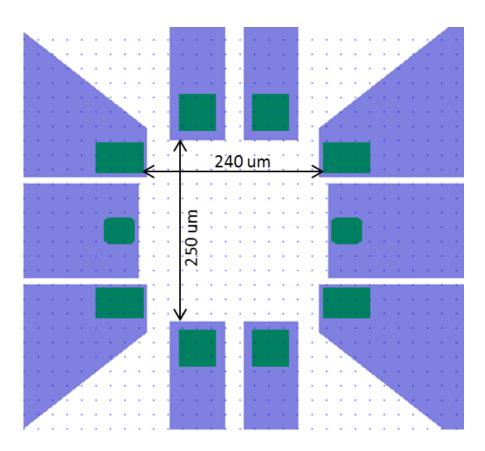

| Figure V.7: Design and bottom view of 4-point probe and daisy chain structure                                                                                                                                                                                                         | s73      |

| Figure V.8: Measurement of Au bump resistivity using 4-point probe method                                                                                                                                                                                                             | 74       |

| Figure V.9: Daisy chain test                                                                                                                                                                                                                                                          | 74       |

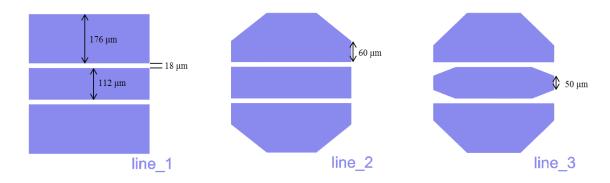

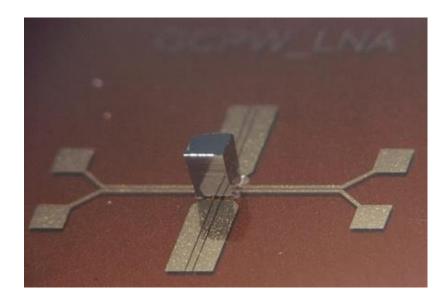

| Figure V.10: Designed 50-Ω-CPW lines (LNA dummy) on glass AF32                                                                                                                                                                                                                        | 75       |

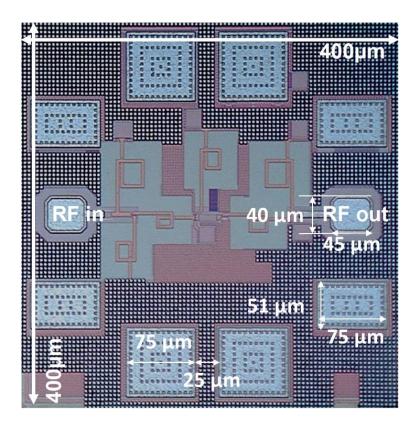

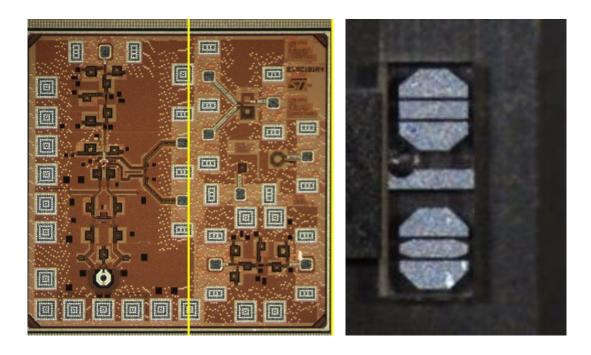

| Figure V.11: Photo of the LNA, circuit dimensions 400 $\mu$ m $\times$ 400 $\mu$ m includin                                                                                                                                                                                           |          |

| Figure V.12: Design of 50-Ω-CPW structure on Kapton                                                                                                                                                                                                                                   | 76       |

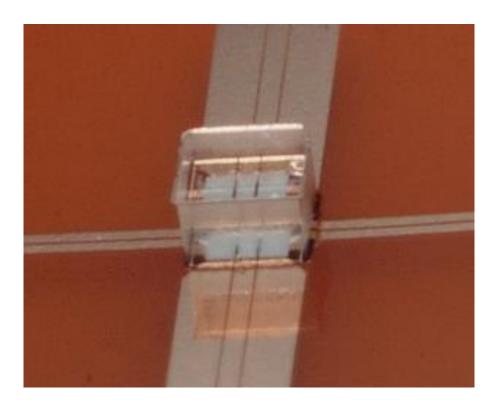

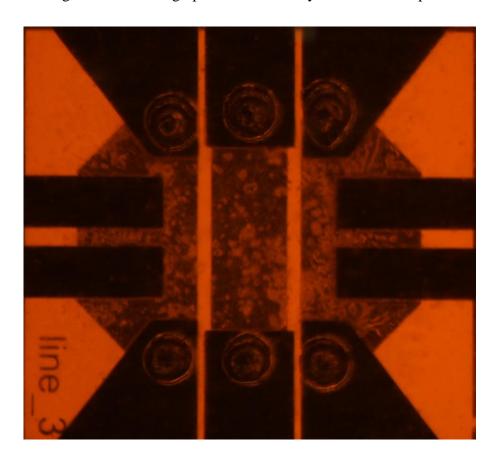

| Figure V.13: Photograph of LNA dummy mounted on Kapton                                                                                                                                                                                                                                | 77       |

| Figure V.14: Bottom view (through Kapton) of a LNA dummy mounted by the f                                                                                                                                                                                                             |          |

| technique.                                                                                                                                                                                                                                                                            | / /      |

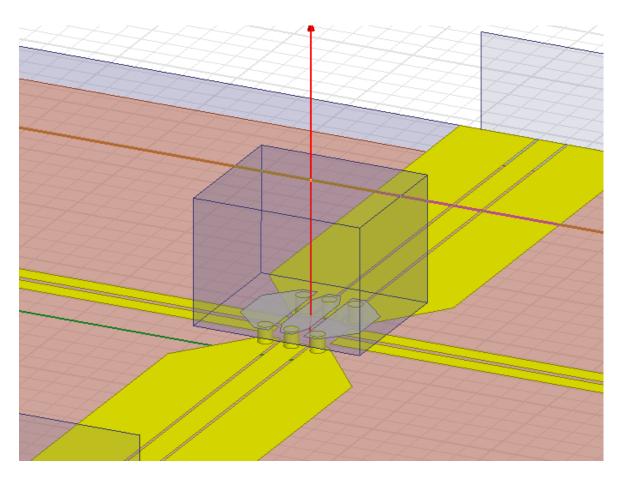

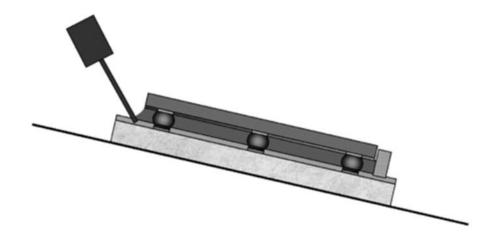

| Figure V.15: Designed LNA dummy chip mounted on Kapton in HFSS75                       |

|----------------------------------------------------------------------------------------|

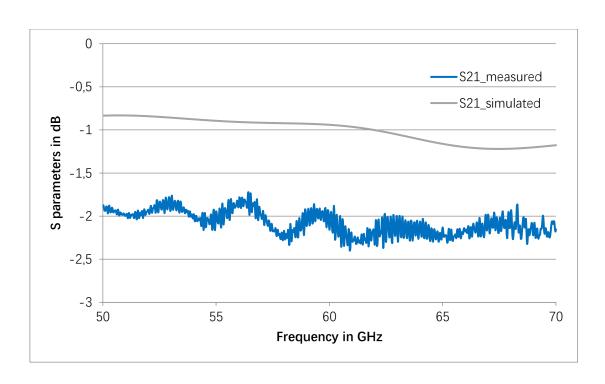

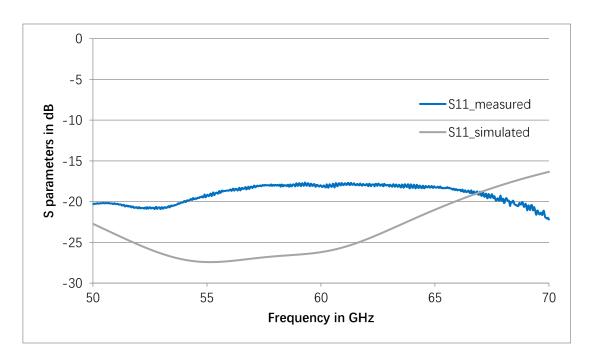

| Figure V.16: Measured and simulated insertion loss S21 of LNA dummy on Kapton          |

|                                                                                        |

| Figure V.17: Measured and simulated return loss S11 of LNA dummy on Kapton79           |

| Figure V.18: Short-circuit situation of Au bump deposited by gold stud bumping process |

| Figure V.19: 65nm CMOS technology LNA mounted on Kapton structure8                     |

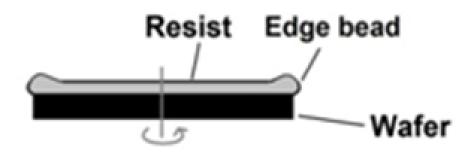

| Figure V.20: Formatting of edge bead during spinning[59]                               |

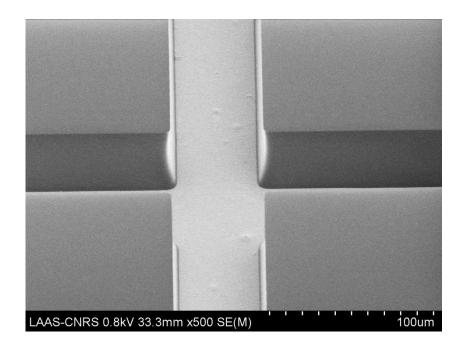

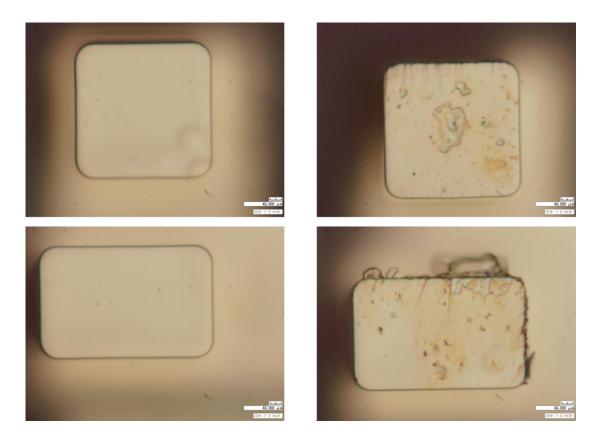

| Figure V.21: SEM photo of a cross opening of 40 XT on Kapton8                          |

| Figure V.22: Fabrication sequence of electrodeposition                                 |

| Figure V.23: Realized 30-µm-height Au bump on Kapton                                   |

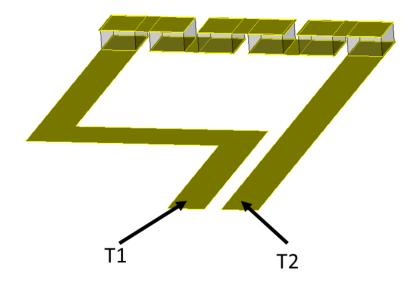

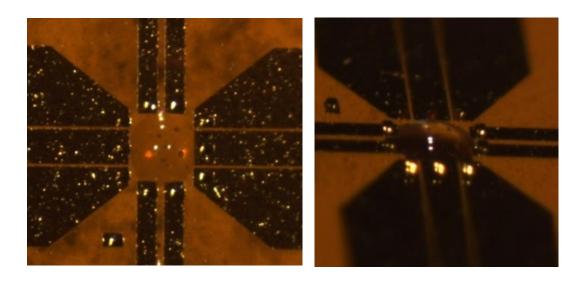

| Figure V.24: 65nm CMOS chip contains LNA block (left) and LNA dummy on glas (right).   |

| Figure V.25: Needle-dispensed adhesive polymer resin on Kapton                         |

| Figure V.26: Leaning LNA dummy mounted on Kapton90                                     |

| Figure V.27: Non-leaning LNA dummy mounted on Kapton90                                 |

| Figure V.28: Au bumps before (left) and after (right) NCA process9                     |

| Figure V.29: Footprint of Kapton structure                                             |

| Figure V.30: Schematic of raised-die underfill, source [60]                            |

#### I. General introduction

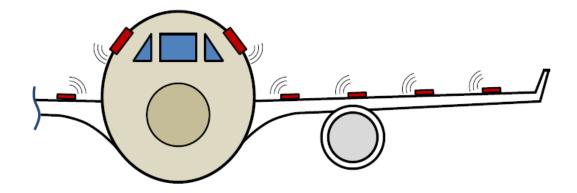

This thesis is part of research effort to develop a 3D heterogeneous integration of wireless sensor node on flexible substrate for the high data rate communication in the unlicensed 60GHz band. The System in Package (SiP) should have a very low power consumption and very low cost to meet the stringent requirement of applications like Wireless Sensor Networks (WSNs). As shown in Figure I.1 and Figure I.2, the deployment of WSNs for Structure Health Monitoring (SHM) can allow better maintenance of the aircraft and predictive of the aircrafts in a long term approach [1].

Figure I.1: Structural health monitoring (SHM) systems arrayed in keay areas where loads are highest. Source: Airbus

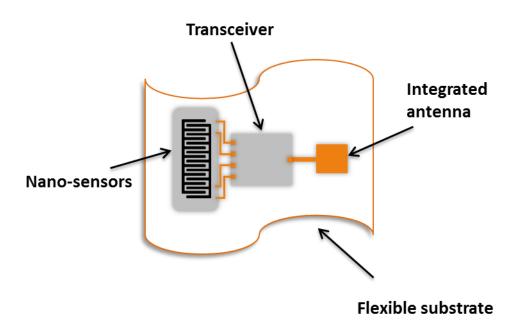

Using a flexible substrate for wireless sensor node integration can offer the advantage of being localized in areas with access difficulty especially in non-planar area or in difficult access places. Figure I.3 shows each node is composed of Nano-sensors, transceivers and TX/RX antenna. Nanotechnologies made it possible the development of ultra-sensitive nano-sensors based on nanoparticles deposition [2][3]. Transceivers

become more and more miniaturized and hence enable the possibility of postpone them onto flexible substrate [4][5]. One can also take the benefits from nano-ink with silver nanoparticles to develop antenna directly on flexible substrate[6][7]. These antennas can be integrated on the flexible substrate along with the developed nano-sensors and miniaturized transceivers, which is the very innovative approach of this thesis.

Figure I.2: WSNs deployed on aircraft wings for real-time in-flight testing.

Figure I.3: Concept of the communicating nano-objects on flexible substrate.

In the following pages the research work accomplished during the three years of Ph.D. will be discussed.

Chapter II gives an introduction on flexible electronic technology. It contains discussions about materials for flexible electronic and different fabrication technology.

A theoretical discussion will also be given.

Chapter 0 describes about the RF characterization of the flexible substrate by using a ring resonator and the adopted microfabrication process in clean room. Then antennas design and its characterization, which including reflecting coefficient, gain and radiation pattern.

Chapter IV deals the implementation of Kapton technology at 60 GHz, including the substrate preparation the implementation of circuits with electrical patterns on single/both side of the substrate.

Chapter V presents the technique of heterogeneous integration on flexible substrate, the DC/RF tests and their results, also a new gold bump forming process is shown in this chapter.

Finally, Chapter VI concludes on integration of wireless sensor node on flexible substrate and shows perspectives towards a fully integrated TX/RX link.

#### II. State of art of flexible electronics technology

#### **II.1** Introduction to Wireless Sensors Network (WSN)

The deployment of Wireless Sensors Network (WSN) for Structure Health Monitoring (SHM) will allow better maintenance of the aircraft, and predictive diagnosis for the aircrafts in a long-term approach.

The major driver for the aircraft industry development [8] nowadays is the ecoefficiency. That means the need of the development of future greener aircrafts with

lowest carbon emission which pass by less weight in the aircraft while keeping the

passenger's comfort. The new generation of aircraft has to be also high performance

while staying cost efficiency. That will be a global system challenge to develop the new

generation aircrafts which can be solved only by a global system solution: rethink all

the system architecture of the aircraft.

In this context, structure health monitoring (SHM) becomes a very important issue. The deploying of a whole sensor network on the structure of the aircraft is necessary. Nowadays, it is estimated that more than 40000 aircrafts will be in activity by the end of 2025 and more than 1000 sensors are necessary for each one. The facility of sensor deployment becomes also a main issue.

The introduction of sensor network for structure health monitoring will improve the maintenance system and will lead to safer aircrafts, which is another major topic together with eco-efficiency and also to lower airplane ticket cost for passengers. It is estimated that a decrease of 3% to 12% in the prices of airline tickets can be expected. Today the deployment of the sensors is limited by wired connections which lead to excess weight and carburant consumption (the major driver is eco-efficiency, greener aircrafts). The wired sensor put also a huge problem of installation. The wireless solution, Wireless Sensors Network (WSN), is imposed by these major constraints.

The aeronautic application impose severe constrains for the reliability, the ElectroMagnetic Compatibility (EMC), the immunity of the interferences and the power consumption. All these constraints lead us to choose to develop short distance wireless communications using ultra-wide band impulse radio technique (UWB-IR)

followed by a RF front-end at 60GHz.

The 60 GHz band is chosen because it is ideally suited for applications required very high data rate, energy-autonomous Wireless Sensor Networks (WSNs) or Gbit/s multimedia links with low power constraints.

#### **II.2** Introduction to flexible electronics

In the past decade, the interest from both academia and industry in the field of flexible electronics has risen enormously due to the unique properties of being bendable, conformably shaped, elastic, lightweight, and non-breakable. In fact, this research topic tops the pyramid of research priorities requested by many national agencies.

According to the market analysis, the total market of flexible electronics will grow from 26.54 billion USD in 2016 to 69.03 billion USD in 2026 [9].

Uncompressed digitized audio, video content can be transmitted in a short-range (below 10 m) with a data rate up to 10.7 Gb/s using unlicensed 60 GHz transceiver [10]. This technology enables applications like wireless personal area networks (WPANs), inflight entertainment (IFE), and structure health monitoring (SHM). The need for integrating all function modules on a single chip or into a single package is emerging.

This chapter deals with the state of the art of materials and fabrication technologies for flexible electronics, especially in the 60 GHz millimeter-wave spectrum.

#### **II.3** Materials for flexible electronics

Substrates that used in flexible electronics need meet various requirements as following [11][12]:

- a) Thermal properties Heat resistance is extremely important for flexible substrates, for example the glass transition temperature (Tg) of a polymer, must be compatible with the maximum fabrication process temperature (Tmax).

- b) Chemical properties The substrate should not release contaminants and should be inert against the process chemicals, and unlike glass substrates which are essentially gas-impermeable, plastic substrates are gas-permeable in a certain way, for organic

light-emitting diode (OLED) application the water permeation rate should lower than  $10^{-6}$  g/m<sup>2</sup>/day and the oxygen permeation rate lower than  $10^{-3}$  to  $10^{-5}$  cm<sup>3</sup>/m<sup>2</sup>/day.

- c) Dimensional stability Dimensional changes may result in deformation (especially warping) and distortion of device films, the causes can be moisture, solvents ueds during manufacture process, exposure to chemicals, and repeated heating and cooling cycles. That is to say, ensuring dimensional stability requires low moisture absorbency, chemical resistance, a low coefficient of thermal expansion, etc.

- d) Electrical and RF properties Electrically insulating substrates minimize the coupling capacitances. RF properties (permittivity and permeability) mainly determine the bandwidth and the efficiency performance of the planar antenna.

- e) Mechanical properties A high elastic modulus makes the substrate rigid, and a hard surface supports the device layers under impact.

- f) Optical properties In display applications, high transparency and optically isotropic substrates (with low birefringence) are required, especially for liquid crystal displays (LCDs).

- g) Surface flatness and roughness Poor surface flatness can cause the gap between top and bottom substrates to become irregular in the case of LCDs, for example, causing image distortion. The thinner the device films, the more sensitive their electrical function will depend on the surface roughness. Asperities and roughness over short distance must be avoided.

Materials used for flexible applications are generally classified into two categories: organic substrate, and inorganic substrate.

#### **II.3.1** Organic substrate materials

a) Polyethylene terephthalate (PET)

PET is a plastic resin and the most common type of polyester. It can be obtained through the polycondensation of ethylene glycol and terephthalic acid. PET is often used in some printed circuit boards for large circuit not requiring soldering because the lack of heat resistance (Tg =  $80 \, ^{\circ}$ C).

#### b) Polyethylene naphthalate (PEN)

PEN is chemically quite similar to PET, and is generally produced by polycondensating ethylene glycol and naphthalene-2.6-dicarboxylic acid, it has more heat resistance (Tg = 120 °C), more chemical resistance, and more dimensional stability than PET.

#### c) Polyimide (PI)

Polyimide is synthesized by polymerizing an aromatic dianhydride and an aromatic diamine. The most notable characteristics of polyimide are its excellent heat resistance (Tg between 360 °C and 410 °C) and excellent chemical resistance (no known organic solvents for the film). It also has excellent rigidity, flexibility and electrical properties.

The main problems of polyimide are water absorption and a high moisture absorption rate at 4% after 24 hours water immersion at 23°C [13], which result a poor dimensional stability. In our own test, the resonance frequency of a v-band patch antenna is shifted 5% to the lower frequency after 12 hours' water immersion at 23°C.

#### d) Liquid crystal polymers (LCPs)

LCPs are partially crystalline aromatic polyesters based on p-hydroxybenzoic acid and related monomers, and have good mechanical properties and high heat resistance (Tg = 145 °C), excellent chemical resistance, excellent moisture absorption rate, along with a low water absorption rate < 0.05% at 75% relative humidity (RH) in 40°C atmosphere.

#### e) Paper-based substrate

Paper-based substrate is a low-cost "green" substrate. It is extremely environment-friendly because it is cellulose in nature and renewable. But it has limitations in terms of high roughness, heat resistance, chemical resistance and water absorption make it problematic for electronics.

Table II.1: Comparative properties of organic substrates.

| Material                        | PET     | PEN     | Kapton    | LCP           | Paper  |

|---------------------------------|---------|---------|-----------|---------------|--------|

| Dielectric constant             | 3.3~3.4 | ~2.9    | 3.2~3.4   | ~3.1          | ~3.2   |

| Loss Tangent                    | ~0.01   | ~0.025  | ~0.002    | 0.002~0.005   | ~0.007 |

| Melting Point                   | ~260 °C | ~265 °C | NA        | 285 °C~315 °C | NA     |

| Glass-transition<br>temperature | 78 °C   | 121°C   | 410°C     | NA            | NA     |

| Chemical resistance             | Good    | Good    | Good      | Excellent     | NA     |

| Mechanical properties           | Good    | Good    | Excellent | Good          | NA     |

#### **II.3.2** Inorganic substrate materials

#### a) Thin glass

Glass is used as standard substrate for various types of devices. Plate glass becomes flexible when its thickness is reduced to  $100 \, \mu m$  or  $200 \, \mu m$  [14]. Glass foils as thin as  $25 \, \mu m$  can be produced by the down-draw technology [15]. Glass has essentially excellent performance in nearly every aspect: resistance to most process chemicals, high temperature tolerance, dimensional stability, optical characteristics, no outgassing, impermeability against oxygen and water. However, since glass lacks flexibility and is very fragile, it is very difficult to handle.

#### b) Metal foil

A typical stainless steel meets many requirements imposed on flexible substrates like high resistance to corrosion and process chemicals, very high temperature tolerance, and dimensionally stable, impermeable to moisture and oxygen. The drawback of metal substrates is that i) they are completely opaque, and thus cannot use for transmissive displays; ii) they are electrically conducting, an insulating layer must be coated to provide circuit isolation.

In conclusion, we have selected Kapton, a polyimide film developed by Dupont as substrate for the development of passive circuits due to its good RF and thermal properties, very good flexibility over a wide temperature range (-73 to +400°C), highly resistant to many chemical solvents, and most importantly for the price, hence we can deploy the WSNs nodes as many as possible at a relatively low cost.

#### II.4 Fabrication technology for flexible electronics

#### **II.4.1** Conventional technologies

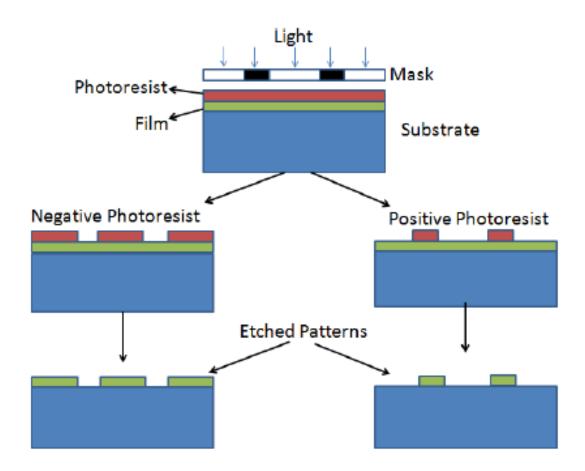

In conventional process, photolithography, chemical etching, and physical vapor deposition (PVD) coating process are usually combined to fabricate metallic patterns, on a substrate.

Figure II.1: Process flow of the photolithography process [16].

There are two types of photoresist (organic polymers whose chemical characteristics change when exposed to UV light): positive and negative. For positive resists, the

exposed area becomes more soluble in the developer. Negative resists behave in an opposite way, the exposed area becomes polymerized, and less dissolvable in the developer.

Negative resists were popular back in the early history of microfabrication process, a major disadvantage is that the exposed regions swell as the counterpart is dissolved by the developer, which compromise the resolution of resist, hence, positive resists became more widely used since they offer better process controllability and higher resolution than negative resists.

Despite the conventional process can produce high complexity and fine detailed patterns, its lengthy process, low throughput, involvement of dangerous chemicals massive vacuum system requirement are major drawbacks of this technology.

#### **II.4.2** Direct printing technologies

The new emerged direct writing technologies that can significantly simplify the fabrication process and dramatically reduce the manufacturing costs became popular recently, this type of technology consist of patterning in a single shot semiconductor materials or metallic materials onto a substrate. Various writing methods, such as screen printing, flexographic printing, gravure printing, and inkjet printing will be described in detail on the following sections.

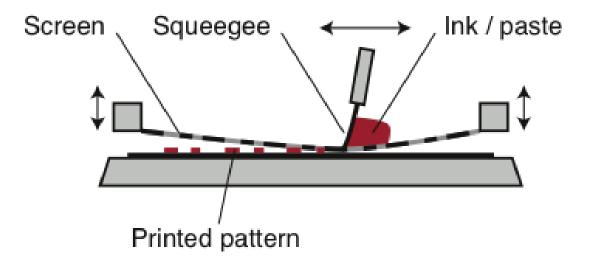

#### a) Screen printing

Screen printing is one of the simplest and most cost effective methods used for the fabrication of printed electronics. It is also commonly used for metallization of silicon solar cells.

To produce a printed pattern, the ink is pressed with a squeegee blade through a screen mesh (stencil) onto the affixed substrate. The stencil is defined on the mesh photochemically or manually, and the squeegee is made of a rubber and therefor easy to wear. Due to the simplicity of the process, it has been widely employed and is compatible with a wide variety of functional inks and substrates. Recently, screen printed electrolyte-gated transistors on polyimide (PI) with graphene patterns as narrow as 40 µm has been reported [17].

Figure II.2: Principle of screen printing[18].

#### b) Flexographic printing

Flexographic printing is a relief printing technique commonly used in the commercial printing industry, especially for foil substrates. The image is printed from protruding elements on a soft, rubber cylinder (plate cylinder), transferring the pattern on substrates.

In a flexographic printing process, the anilox cylinder is first immersed in an ink bath and a doctor blade is used to scrape off the excess ink from the non-engraved surface of anilox cylinder. The ink is then brought into contact with the soft printing plate, which is subsequently transferred to the substrate.

With flexography, RFID tags has been printed on paper substrate with silver ink [19]. Continuous conductive tracks of silver ink have also been reported on a indium tin oxide (ITO) coated, heat stabilized polyethylene terephthalate (PET) film with a minimal line widith of 74.6  $\mu$ m [20]. The typical resolution limit is about 50 to 100  $\mu$ m.

Figure II.3: Principle of flexographic printing [21].

Figure II.4: Principle of gravure printing[23].

#### c) Gravure printing

Contraire to the flexography, the relatively low viscous ink is transferred from the pits of the master to the substrate. It has four basi component to each printing unit: an

engraved (gravure) cylinder, ink bath, doctor blade and the impression roller (cylinder). The key of a gravure printing is the gravure cylinder, which carries the image design (ink) to be printed. Excess of ink is removed from the protruding elements of the gravure cylinder by the doctor blade before transferred to the substrate. Grauvre printing of continuous graphene pattern as fine as 30 µm on Kapton substrate has been reported [22].

#### d) Inkjet printing

Inkjet printing of RF circuits and antennas using highly conductive inks have become very popular in recent years [24]. This new technology utilizes conductive inks baked on different nanostructure materials such as silver nanoparticle based ink to form pattern on the substrate from a digital image. It is a low-cost, non-impact and raid technique with a large potential to manufacture electronic circuits.

Figure II.5: Principle of inkjet printing process [28].

By using inkjet printing, a square monopole antenna on PEN has been reported on [25], a transmission lines with silver nano-particles has been printed on Kapton [26], and a 60 GHz CPW fed dipole antenna on PET substrate has been reported on [27].

#### II.5 Evolution of electronic packaging

Over the past decades, electronic assembly took different paths of evolution. Such as System on Chip, Chip on Board, System in Package, System on Package and Package on Package.

Figure II.6: Development of packages in the last decades [29].

#### II.5.1 System on Chip (SoC)

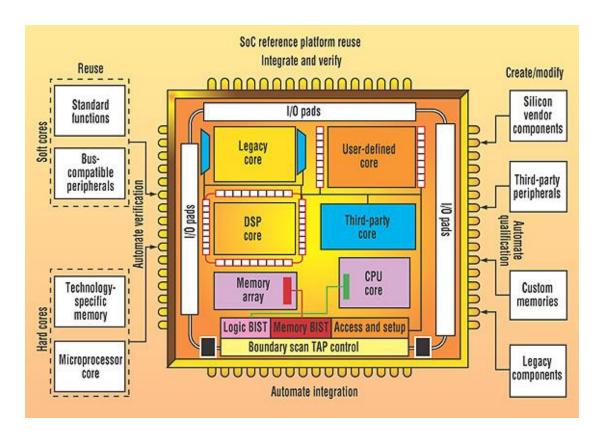

The System on Chip (SoC) is a technology operating at zero level packaging and answers to the More Moore domain. By its name, System on Chip is an integrated system implemented in CMOS (Complementary Metal Oxyde) technology. These modern technologies are the reasons that made possible the integration of a complete electronic system on a single silicon chip. This integrated circuit (IC), generally complex, contains a large number of different electronic functions. Recent SoC can contain several microprocessor cores, Digital Signal Processing (DSP) core, associated with hardware operators, memories and I / O interfaces (Figure II.7). This SoC technology is often used for embedded applications. On chip integrated antenna was reported in [30] for 60 GHz WPAN applications.

Figure II.7: Example of a SoC architecture (source: http://electronicdesign.com/).

#### II.5.2 Chip on Board (CoB)

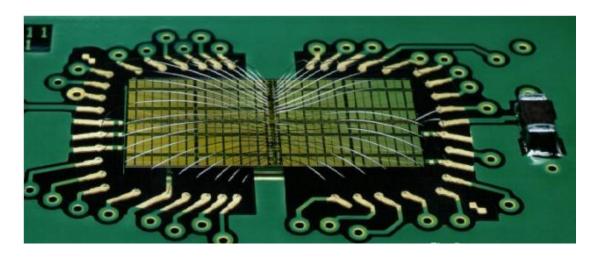

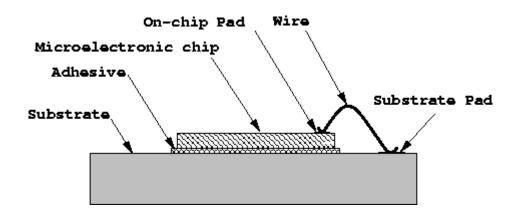

it refers to the assembly technology in which the chip or die is directly mounted on its final circuit and electrically interconnected to the latter, instead of undergoing traditional assembly as an integrated circuit (IC) individual. Chip on Board (CoB) simplifies the entire design and manufacturing process of the final product and improves its performance due to the short interconnection paths. Figure II.8 shows two views of a memory module CoB product bonded with aluminum wire.

The term generally used for CoB technology is currently Direct Chip Attachment (DCA). Beside from the circuits used for CoB, various substrates are available for use of DCA. For example, ceramic and glass-ceramic substrates which exhibit excellent dielectric and thermal properties. The organic substrates also exist because of its light weight and low cost while offering a low dielectric constant. 60 GHz wireless chipsets was investigated in [31] by using the DCA method.

Figure II.8: Two views of a CoB technology memory module (source: MB Electronique).

#### **II.5.3** MCM

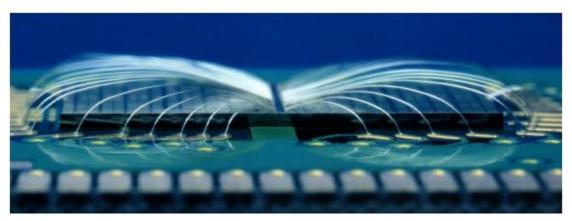

A Multi-Chip Module (MCM) is a generally electronic assembly where multi integrated circuits (ICs), semiconductor dies and/or other discrete components are integrated on a single substrate (Figure II.9), which facilitates their use as single component (like a larger IC). The MCM itself is often referred to as a "hybrid IC", which shows its integrated nature.

The MCMs come in a variety of shapes depending on the complexity and development philosophies of their designers. These can range from using pre-packaged ICs on a small printed circuit board (PCB) meant to mimic the package footprint of an existing chip package, to fully custom chip packages integrating many chip dies on a High-Density Interconnection (HDI) substrate. 60 GHz Antenna Array for Multi-Chip Communication was studied and shown in [31].

Multi-Chip Module packaging is an important facet of modern electronic miniaturization and micro-electronic systems. MCMs are classified according to the technology used to create the HDI (High Density Interconnection) substrate.

- MCM-L laminated MCM. The substrate is a multi-layer laminated PCB (Printed circuit board).

- MCM-D deposited MCM. The modules are deposited on the base substrate using thin film technology.

- MCM-C ceramic substrate MCMs, such as LTCC.

Figure II.9: Example of MCM structure.

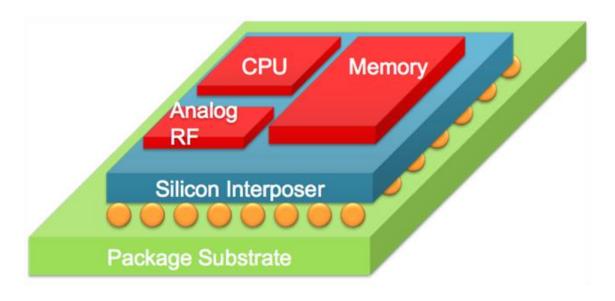

#### II.5.4 System in Package (SiP)

As shown in Figure II.10, the System in Package (SiP) presents generally a vertical integration configuration. In this case, the different functionalities of the system are made via chips with different natures (standard bare silicon chip, microsystems, passive components and RF devices ...) interconnected to each other by stacking. It consists of a stack of electronic slices whose interconnection is made in three dimensions using the faces of the stack to make the connections between slices. A SiP micro-radar at 60 GHz was designed and measured for noncontact vital sign detection[32].

Figure II.10: Example of SiP structure (SiP technology of 5 stacked chips), source: renesas.com.

#### II.5.5 System on Package (SoP)

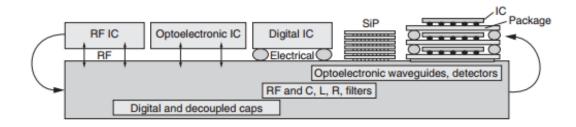

We can also cite the System on Package (SoP) as a new integration solution. The concept of SoP brings the idea of integrating inside the volume of the substrate, mainly used for electrical interconnections, passive element such as capacity, inductors, filters which are the general functionality of the system. This technique is also a 3D integration. This dimension is formed by the stack of organic substrate layers that have been functionalized beforehand. This technology then groups the previous (SoC, SiP and MCM) and therefore it is much more complete. 60 GHz SoP research activities including the integration and demonstration of a transmitter (Tx)/receiver (Rx) radio were presented in [33].

Figure II.11: Example of SoP structure [34].

#### II.5.6 Package on Package (PoP)

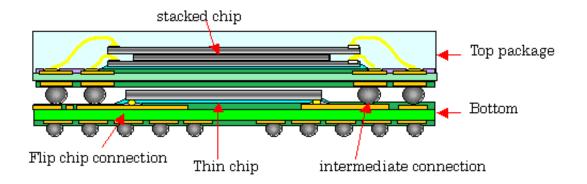

One of the latest innovations is the Package on Package (PoP) which is an assembly process of combining several vertically packaged modules. Two or more modules are

stacked one above another, with a standard interface for routing signals between them. This allows to have a higher density of components. The most obvious advantage is saving space on the motherboard. The PoP uses much less board space, almost as little as the SiP. Electrically, PoP offers advantages in minimizing the length of track between different inter-operating parties, such as a controller and a memory. This provides better electrical performance of the devices, the return of interconnections between circuits, the speed of the signal and reducing noise and crosstalk. junction temperatures are lower in compared to those of SiP. The main advantage in terms of PoP returns is that the memory device is decoupled from the logic device and therefore, these two devices can be optimized and tested separately. From the perspective of manufacturing efficiency, only the components tested good are assembled, which is very favorable in terms of manufacturing cost. The Figure II.12 describes an example PoP designed by Shinko[35].

Figure II.12: Example of PoP structure, source: shinko.co.jp.

#### **II.6** Conclusion

In conclusion, inkjet printing is a direct write technology which presents a low-cost advantage because the design pattern is transferred directly to the substrate and does not require masks. However, the liquid metal nanoparticles used for inkjet printing have much lower conductivity compared with the bulk conductor used for lithography [36][24], which can degrade the printed circuit's performances at RF and millimeter wave frequency. In addition, millimeter wave applications require high accuracy, and both screen printing and inkjet printing can only offer a highest resolution about 20 µm [37]. Antennas fabricated on Kapton at lower frequency have been reported in [38][39]

using screen printing or inkjet printing, but the traditional photolithography remains the most suitable method for the microfabrication at millimeter frequency range.

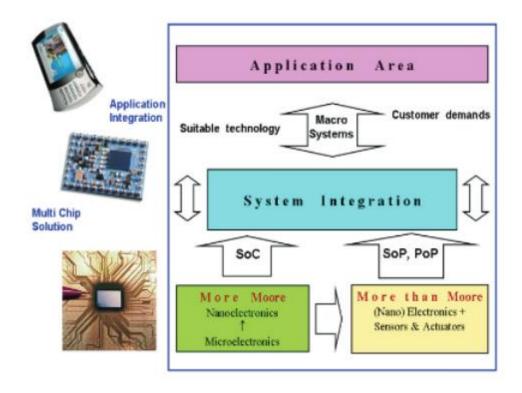

The evolution of electronic packaging followed two major trends that are intertwined: the "More Moore" and the "More than Moore". The first trend is to miniaturize the components and the second is to diversify their duties. Combining the two trends allows the emergence of new innovations such as: SoC, the CoB, MCM, which are horizontal integrations and SiP, PoP and the SoP which are vertical or 3D integration.

Figure II.13: Roadmap of system integration. [29].

# III. Design and measurement of passive circuit elements on flexible substrate

#### III.1 Theoretical background

#### **III.1.1 Reflection coefficient**

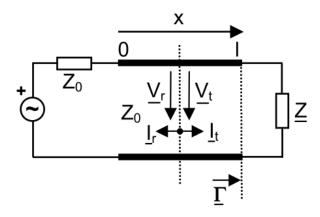

Microwave measurements are usually made with a length of transmission line between the observation point and the terminals of the device under test (DUT) as shown in Figure III.1.

Figure III.1: Transmitted and reflected currents and voltages.

At a location x, the voltage the current on the line are [40]:

$$\underline{V}(x) = \underline{V}_t + \underline{V}_r$$

III.1

$$\underline{I}(x) = \underline{I}_{t} - \underline{I}_{r}$$

III.2

At the terminal x = 1, the following equation must be satisfied:

$$\underline{Z} = \frac{\underline{V}(l)}{\underline{I}(l)} = \frac{\underline{V}_t + \underline{V}_r}{\underline{I}_t - \underline{I}_r} = \frac{\underline{V}_t + \underline{V}_r}{(\underline{V}_t - \underline{V}_r)/Z_0} = Z_0 \frac{1 + \underline{V}_r/\underline{V}_t}{1 - \underline{V}_r/\underline{V}_t}$$

$$= Z_0 \frac{1 + \underline{\Gamma}}{1 - \underline{\Gamma}}$$

III.3

The ratio of the reflected voltage amplitude to that of the transmitted voltage amplitude is the reflection coefficient which is given by:

$$\underline{\Gamma} = \frac{\underline{V}_{r}}{\underline{V}_{t}} = \frac{\underline{I}_{r}}{\underline{I}_{t}}$$

III.4

$$\underline{\Gamma} = \frac{\underline{Z} - Z_0}{\underline{Z} + Z_0}$$

III.5

When  $\underline{Z}=Z_0$ ,  $\underline{\Gamma}$  equals 0, the maximum power is transferred to the load, and in the case of  $\underline{Z}=0$  or  $\underline{Z}=\infty$ ,  $\underline{\Gamma}$  equals -1 and 1 respectively, the power is totally reflected to the source.

#### III.1.2 Fundamental parameters of antenna

#### a) Gain and efficiency

Gain of an antenna (in a given direction) is defined as the ratio of the intensity, in the direction of peak radiation, to the radiation intensity that would be obtained If the power accepted by an isotropic antenna. Antenna gain is more commonly used than directivity in antenna's specification sheet because it takes into account the actual losses that occur.

Antenna gain (G) can be related to directivity (D) and antenna efficiency  $(\eta)$  by:

$$G = \eta. D$$

III.6

If the antenna is lossless, than its gain and directivity is equal. So all the power delivered to the antenna can be radiate. In the real case, a high efficiency antenna has most of power present at the antenna's input radiated away, a low efficiency antenna has most of the power absorbed as losses within the antenna, or reflected away due to impedance mismatch. So the efficiency of an antenna can be written as follows:

$$\eta = \frac{P_{radiated}}{P_{input}}$$

III.7

#### b) Radiation pattern

An antenna radiation pattern or antenna pattern defines the variation of the power radiated by the antenna as a function of the directional coordinates. Usually, they are observed in the far field.

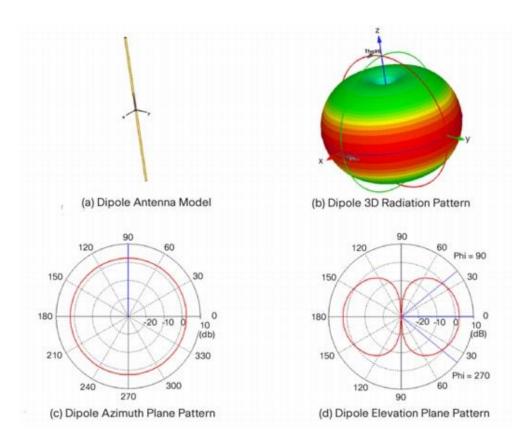

Figure III.2: Dipole Antenna with 3D Radiation Pattern, Azimuth Plane Pattern and Elevation Plane Pattern, source Cisco.

Figure III.2 shows an example of a donut shaped radiation pattern for a dipole antenna. In this case, along the z-axis, which would correspond to the radiation directly overhead the antenna, there is very little power transmitted. In the x-y plane (perpendicular to the z-axis), the radiation is maximum. These plots are useful for visualizing which directions the antenna radiates.

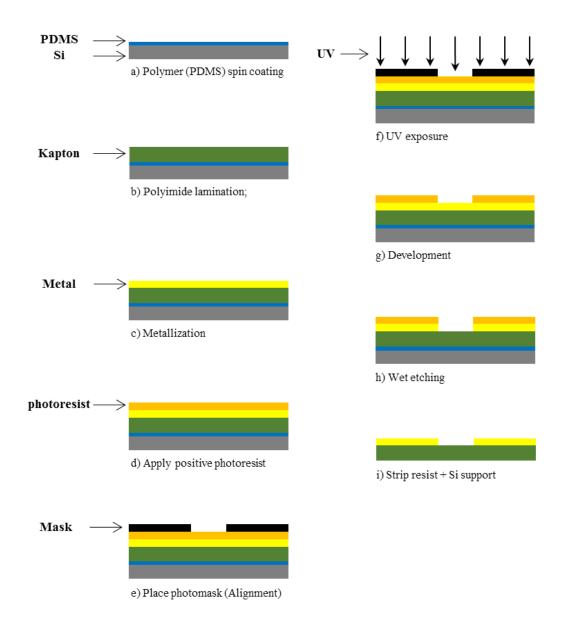

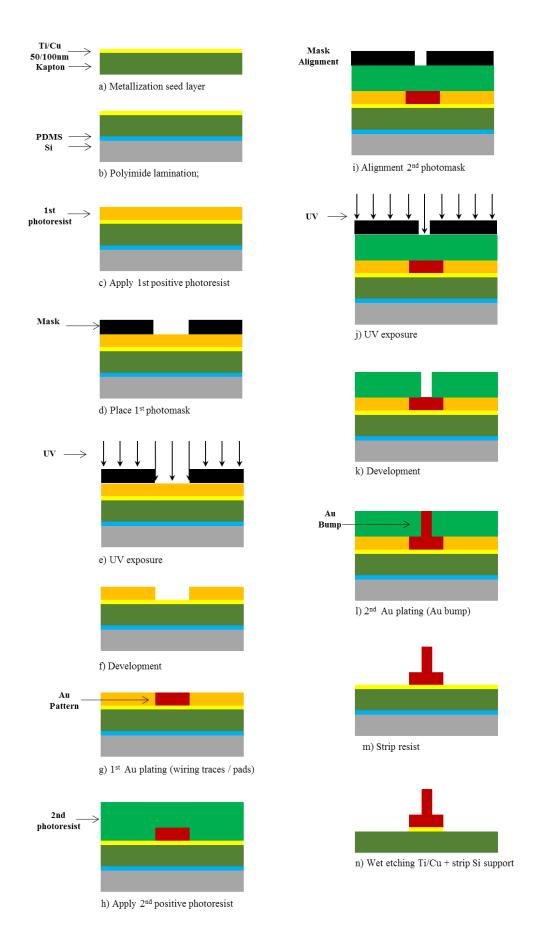

#### III.1 Technological process for flexible substrate

To manufacture our circuits onto a flexible substrate, we have chosen the traditional

photolithography, the main difficulty during the fabrication process lies on the flexible film handling and its use in micro-technology equipment. In order to overcome this difficulty, a 4-inch silicon wafer is used as a host carrier. One of the critical obstacles consists in finding a way to adhere the polyimide film on the Si support. This adhesion has to be compatible with the various technological stages (vacuum, solvent and temperature) and allows after manufacture a peeling without any physical or chemical constraint.

A matured fabrication process [41] is used where first a PDMS (PolyDiMethylSiloxane) spin coating is performed for the adhesion of the polyimide on the holding wafer. Then the Kapton polyimide is patterned on the PDMS-Si support using a Shipley 360N laminator (see Figure III.3). A resin spin coating is then realized in a fully automated resist processing tool EVG120 (see Figure III.4), followed by a photolithography process.

Figure III.3: Shipley 360N Laminator.

Figure III.4: EVG120 resist processing system.

During the different fabrication processes, Kapton polyimide is metallized with Ti/Au layers (50 nm/ 200 nm) or Ti/Cu layers (50 nm/500 nm) using the Electron Beam Physical Vapor Deposition (EBPVD). In case of Cu coating, the fabrication process will be terminated with a surface finishing (gold immersion deposits) to prevent Cu from oxidizing. Both wet-etching and lift-off methods were carried out during different tests, each of them is able to obtain a sufficient resolution for the metallization tracks.

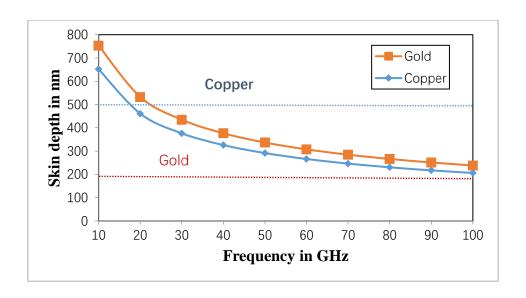

The skin depths of gold and copper at microwave frequencies are given in Figure III.5. One can see the skin depth decrease with higher frequency. So with the metal thickness mentioned above, selected mainly for V-band applications, high losses at lower frequencies should be expected.

Figure III.5: Skin depth versus frequency, the horizontal lines show the selected metallization thickness.

## III.2 RF characterization of Kapton

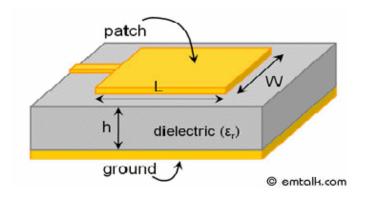

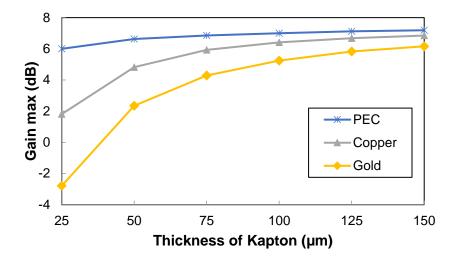

A commercially 127-µm Kapton (type 500HN) was chosen for our flexible substrate as discussed previously, which is the thickest product available in the HN series. In fact there is a minimum substrate thickness that must be respected for designing an effective patch antenna in V-band. As shown in Figure III.6, this type antenna is composed by a rectangular patch on the top side of the substrate and a ground plane on the back side. In order to avoid undesired capacitive effect and to ensure a highly-efficient radiation mechanism of a patch antenna, a quick parametric study is done. It shows the influence of substrate thickness versus maximum antenna gain in HFSS simulation (Figure III.7). One can see that the thicker the substrate, the better the antenna gain, regardless its metallization layer: Perfect Electric Conductor (PEC), copper or gold.

Figure III.6: Microstrip Patch Antenna, source emtalk.com.

Figure III.7: Maximum simulated antenna gain versus substrate thickness at 60 GHz.

#### **III.2.1 Ring resonator**

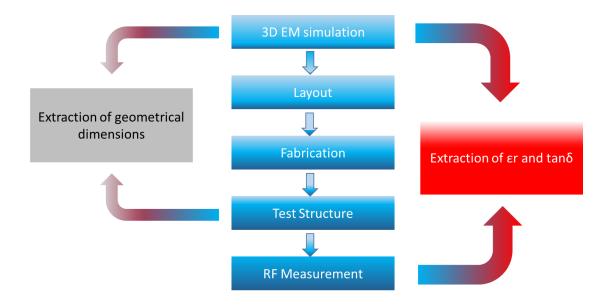

To design properly any high-frequency structure on this 127- $\mu$ m Kapton by using numerical simulation, the knowledge of dielectric properties of substrate becomes necessary. The dielectric properties of Kapton: the relative permittivity  $\epsilon_r$  and the loss tangent tan  $\delta$  were extracted from S-parameters measurement of a ring resonator as illustrated in Figure III.8 [42].

Figure III.8: Procedure for extraction of dielectric parameters.

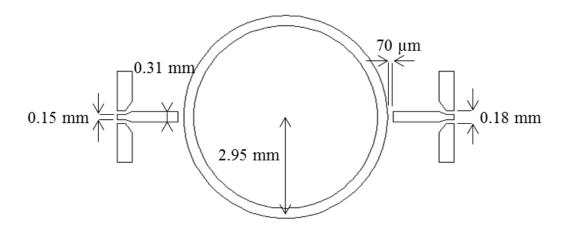

This resonator is composed by a ring with mean radius of 2.95 mm. The width of the microstrip on the Kapton surface is 310 µm to give us a characteristic impedance in the

range of 50  $\Omega$ . Additionally, a grounded coplanar waveguide (GCPW) to microstrip transition was optimized with the help of HFSS electromagnetic (EM) software to minimize the impedance mismatch. There are two 70  $\mu$ m gaps at the edges of the ring to couple the resonator with the measurement system, which provides us sufficient coupling to measure the resonator without overload the test equipment (see Figure III.9).

Figure III.9: Ring resonator design.

Fig. III.10: Simulated and measured insertion loss of the ring resonator.

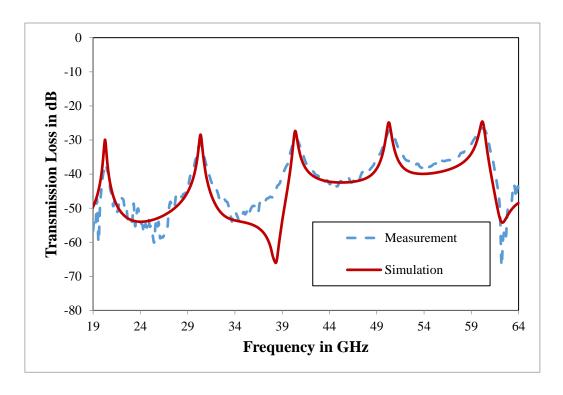

The same structures were also modeled using ADS Momentum software. In order to fit measured and simulated data for the entire frequency band, we tuned the dielectric

parameters. It is clear that the full 3D Finit Element Method (FEM) used in HFSS software is more accurate than the Method of Moments (MoM) used in ADS Momentum, but in our case, a simulation from 10 to 65 GHz with ADS Momentum is much faster. The correlation between experimental and simulation results is depicted in Fig. III.10. Simulated and measured resonant frequencies and quality factors are given in Table III.1. The experimental results were obtained by using an Agilent PNA network analyzer and Cascade Microtech GSG probe with a 150  $\mu$ m pitch. A 2-port onwafer SOLT calibration method was used. The dielectric properties found for this Kapton polyimide are  $\epsilon_r = 3.2 \pm 0.03$  and  $\epsilon_r = 0.012 \pm 0.004$  within the entire frequency band.

Table III.1: Resonant frequencies & quality factors.

| Simulation         |          | Measurement        |          |  |

|--------------------|----------|--------------------|----------|--|

| Resonant Frequency | Q factor | Resonant Frequency | Q factor |  |

| 20.27              | 72.4     | 20.345             | 36.7     |  |

| 30.36              | 89.3     | 30.265             | 39.1     |  |

| 40.37              | 98.5     | 40.34              | 42       |  |

| 50.28              | 104.7    | 50.415             | 44.4     |  |

| 60.17              | 114.6    | 60.18              | 50.2     |  |

#### III.3 Antennas

A high gain antenna at 60 GHz is required to enable an ultra-low power consumption radio interface, and this antenna must also have a relative large bandwidth (500 MHz to 2 GHz) to ensure the Ultra-Wide Band Impulse Radio (UWB-IR) communications.

#### III.3.1 Patch antenna

A 60 GHz grounded coplanar waveguide (GCPW) feeding rectangular patch antenna (see Figure III.11 a) was designed, fabricated, and measured on a flexible 127-µm-thick polyimide substrate (Kapton). The GCPW-to-microstrip transition was optimized to

reduce the impedance mismatch. The antenna was then characterized in terms of return loss, gain, and radiation pattern.

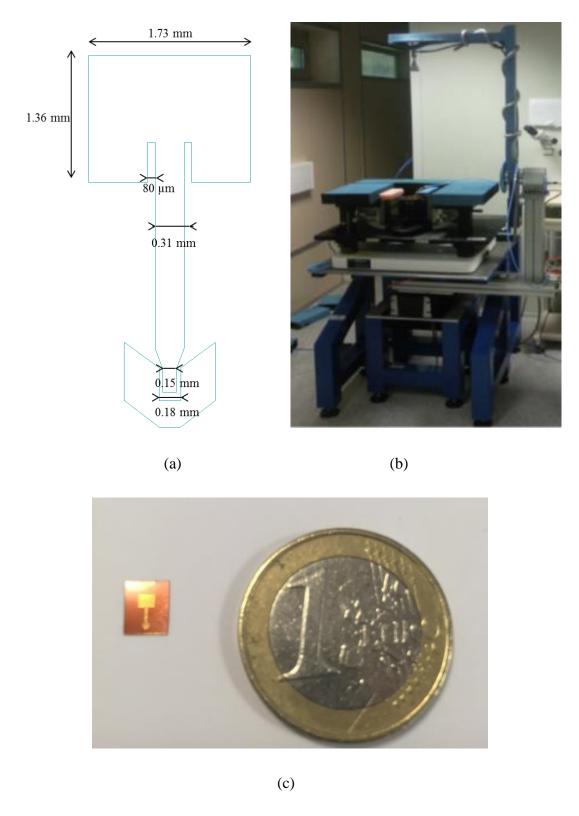

Figure III.11: (a) 60GHz GCPW feeding rectangular patch antenna; (b) Measurement setup; (c) Manufactured patch antenna on Kapton.

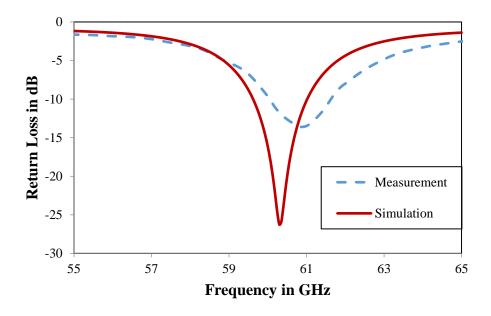

The simulated and the measured return loss of the patch antenna versus frequency are presented in Figure III.12. The agreement between experiments and simulations is very good: a relative frequency shift of only 0.7% is observed between the simulated (HFSS) and measured results. The difference is due to the uncertainties of the substrate permittivity/permeability value and under/over etching of the conductive patterns. The measured impedance bandwidth, defined by return loss less than -10 dB, is from 60.05 GHz to 61.8 GHz (3% of relative bandwidth).

The far-field radiation pattern and gain measurement were performed with a probe based antenna measurement setup at LAAS (Figure III.11 b). The antenna is fed through a 150-µm Ground-Signal-Ground (GSG) probe, and this probe is directly connected to a 65 GHz VNA (Anritsu 37397D) with a flexible V-cable. Dielectric foam from Rohacell was used below the antenna to prevent reflections from the metallic part of the setup. The Antenna Under Test (AUT) was illumined by the field generated by a calibrated VT-15-25-C horn antenna from Vector Telecom.

Figure III.12: Simulated and measured return loss of the patch antenna.

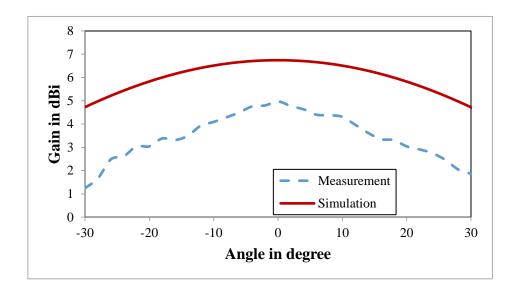

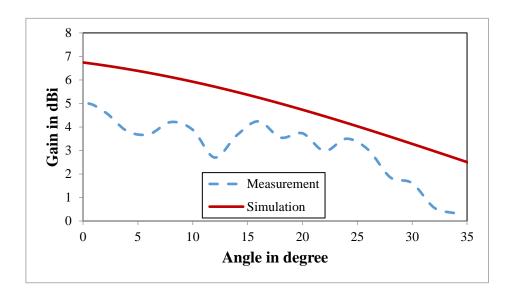

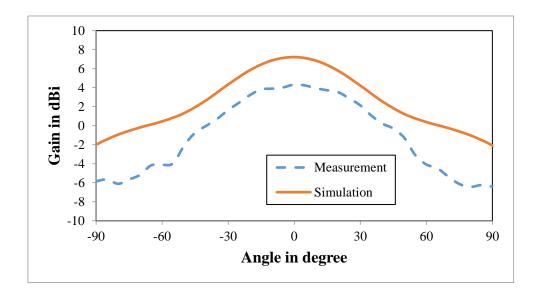

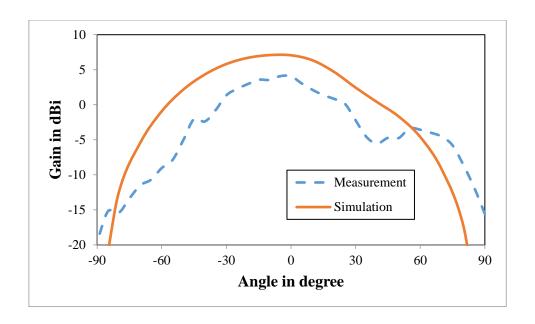

Under these conditions, a maximum gain of 5 dBi was measured in the perpendicular direction of the antenna at 60.3 GHz. The simulated and measured radiation patterns in the H- and E-plane are given in Figure III.13 and Fig. III.14. The difference of gain between simulation and measurement is about 1.7 dB, which may due to insertion loss

introduced by the CPW probe and the metallization quality of conductive tracks. The E-plane radiation pattern has a restricted range due to architecture of the measurement setup because the probe was placed in the E-plane. Ripples observed in the E-plane are due to reflection and diffraction effects on the metallic micro-positioner and the probe. The 3-dB beamwidth is 56° for the H-plane.

The results demonstrate the quality of fabrication on flexible polyimide substrate and the accuracy of measurement setup for millimeter-wave antenna.

Figure III.13: H-plane radiation patterns of the patch antenna at 60.3 GHz.

Fig. III.14: E-plane radiation patterns of the patch antenna at 60.3 GHz.

#### III.3.2 Crossed-dipoles array antenna

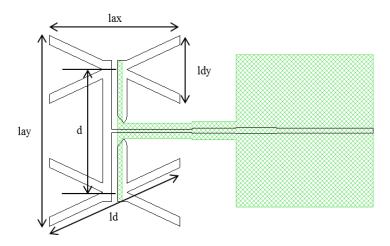

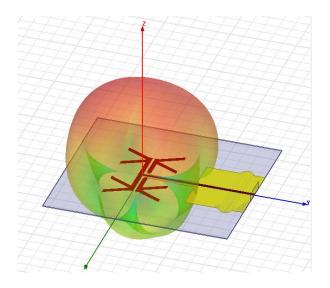

For the interest of energy harvesting for satellite health monitoring, the cross dipoles array antenna (CDAA) on Kapton polyimide is proposed, which consists of four printed half-wave dipoles arrays on the top side of substrate. As shown in Fig. III.25 to Figure III.17, CDAA is a coplanar stripline (CPS) structure. A T-junction CPS-to-microstrip was designed and optimized by using intensive electromagnetic simulations to allow the excitation of the CDAA by a microstrip and the proper connection with a K "end launch" connector from Southwest for measurement purposes [43].

Figure III.15: Cross dipoles array antenna: top view of the layout (the bottom layout is represented in filled with green trellis.

Figure III.16: Simulation model of Cross dipoles array antenna.

Figure III.17: Manufactured Cross dipoles array antenna.

Table III.2: Cross dipoles array antenna dimensions.

| Band | lax (mm) | lay (mm) | d (mm) | Ld (mm) | Ldy (mm) |

|------|----------|----------|--------|---------|----------|

| Ku   | 8.5      | 12.42    | 8      | 93.18   | 4.42     |

| K    | 5.7      | 7.5      | 4.5    | 6.26    | 3        |

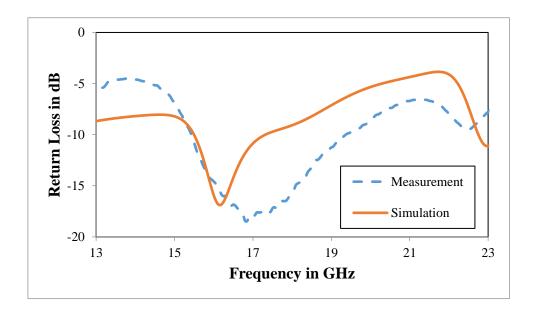

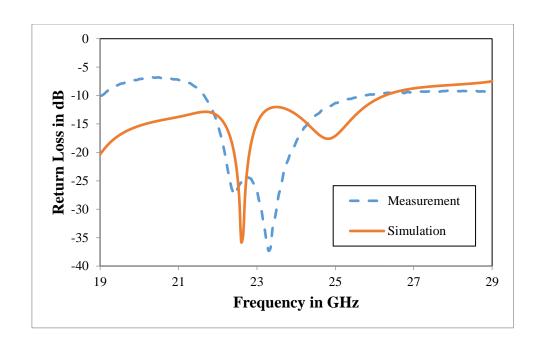

Two CDAAs operating in Ku and K band are fabricated and measured respectively, their dimensions are summarized in Table III.2. S-parameter measurement and simulation results are reported in Figure III.18 and Fig. III.19. One can see a large impedance bandwidth is obtained (measured at S11 = -10 dB) for two proposed antennas, 15.45 GHz to 19.35GHz for the Ku band CDAA (22% of relative bandwidth), and 21.7GHz to 25.7GHz for the K band CDAA (17% of relative bandwidth).

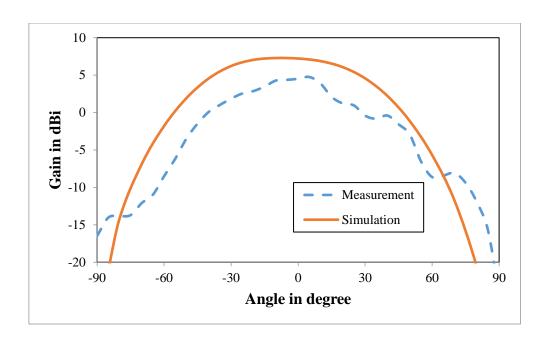

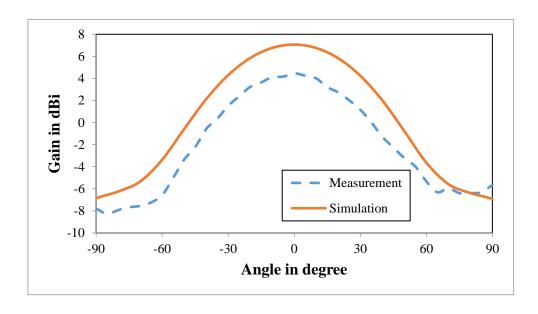

The radiation pattern characterizations were performed in an anechoic chamber. Fig. III.20 and Fig. III.21 report the measured and simulated radiation patterns in two orthogonal planes at 17 GHz for the Ku band CDAA. Fig. III.22 and Fig. III.23 report the measured and simulated radiation patterns at 22 GHz for the K band CDAA. We note that the simulation results were obtained in HFSS and the "end-launch" connector was not included in the model. The difference of gain between measurement and simulation is about 2.7 dB may due to (i) the losses introduced by the "end-launch" connector (estimated to be in the range of 1 dB); (ii) the assembling mechanical process

for connecting the Kapton structure to the connector that can lead to an imperfect contact; (iii) the skin effect. Metallization layers are composed by: (a) adherent layer of Ti about 50 nm; (b) cooper layer (thickness: 500 nm); (c) gold layer (thickness: a few nanometers). As mentioned in section II, the skin depth of copper at 20 GHz is 460 nm which is comparable with the total metal thickness of 600 nm, thus unexpected RF losses may occur. The ripples observed in the YOZ plane (phi = 90°) are due to reflection and diffraction effects on the connector and the coaxial cable. The 3dB beamwidth is 52° in the XOZ plane and 65° in the YOZ plane for the Ku band CDAA at 17 GHz. For the K band CDAA, The 3dB beamwidth is 58° in the XOZ plane and 62° in the YOZ plane at 22 GHz. As depicted from Figure III.18 to Fig. III.22, the proposed CDAAs are wideband antennas (22% of relative bandwidth in Ku band and 17% of relative bandwidth in K band). The radiation pattern does not change significantly in the relative bandwidth and the measured maximum gain is about 4.3 dBi (included the losses added by the end lunch connector and the associated mounting process and by CPS-to-microstrip T junction). We note that the gain can be increased by 3dB if a metallic plate acting as reflector is properly putted below the CDAA.

Figure III.18: Simulated and measured return loss of the Ku band CDAA.

Fig. III.19: Simulated and measured return loss of the K band CDAA.

Fig. III.20: XOZ plane (phi =  $0^{\circ}$ ) radiation patterns of the  $K_u$  band CDAA at 17 GHz.

Fig. III.21: YOZ plane (phi =  $90^{\circ}$ ) radiation patterns of the  $K_u$  band CDAA at 17 GHz.

Fig. III.22: XOZ plane (phi =  $0^{\circ}$ ) radiation patterns of the K band CDAA at 22 GHz.

Fig. III.23: YOZ plane (phi =  $90^{\circ}$ ) radiation patterns of the K band CDAA at 22 GHz.

#### III.3.3 Cross slot dipole antenna

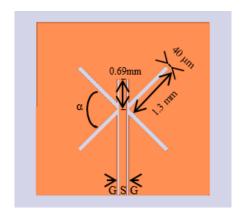

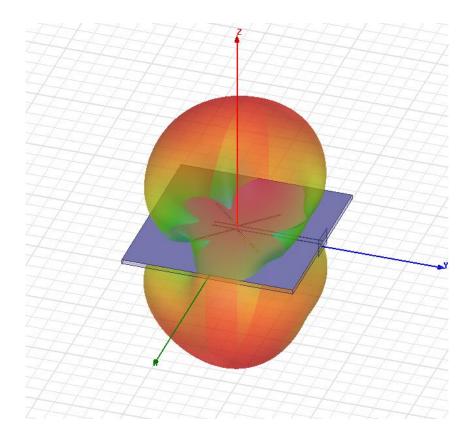

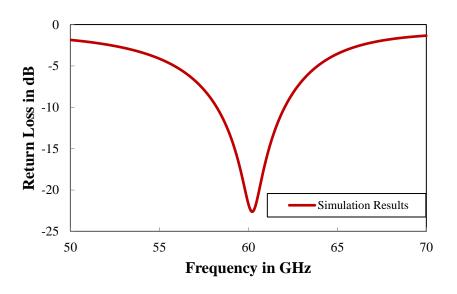

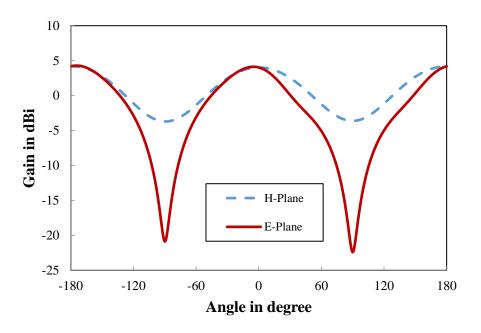

Inspired by the design of CDAAs at Ku band and K band, and the Babinet's principle which relates the radiated field and impedance of a slot antenna to a printed (strip) antenna, a first prototype of Crossed Slot Dipole Antenna (CSDA) in V band is proposed shown in Fig. III.24 and Fig. III.25. The antenna is designed on a 127- $\mu$ m thick Kapton with a dielectric constant 3.2 and a loss tangent 0.006. CPW feed dimensions of S = 170  $\mu$ m and G = 12  $\mu$ m were selected corresponding to the 50 Ohm GSG probe. The slot length L is fixed to 1.3 mm (quarter wavelength for 60 GHz) for the simulation, the slot width w, the stub length d and the angle between slots  $\alpha$  were set to 40  $\mu$ m, 0.69 mm and 45° as default respectively.

Fig. III.24: Design of crossed slot dipole antenna.

Fig. III.25: Simulation model of slot dipole antenna.

Fig. III.26: Simulated return loss of the cross slot dipole antenna.

Fig. III.27: Simulated (HFSS) radiation patterns in E-Plane and H-Plane at 60.2 GHz.

Fig. III.26 shows the simulated return loss. The center frequency is 60.2 GHz, and the -10 dB bandwidth is from 58.2 GHz to 62.05 GHz (6% of relative bandwidth). The antenna radiation patterns were also presented in Fig. III.27, a peak antenna gain of 4.02 dB is obtained at 60.2 GHz.

A parametric study for the angle between slots is shown in Table III.3. It is seen that when the angle  $\alpha$  increase, the peak antenna gain decrease along with a larger half power beamwidth (HPBW) on H-plane. This phenomenon can be explained by the increase of the coupling effect when the slots approach each other.

As demonstrated by the simulation, CSDA has interesting performances in 60 GHz band. This antenna has no ground plane and in V band its performances (input matching and radiation pattern) can be impacted by the surrounding environment placed behind the antenna (the metallic chuck of the probe station used for S-parameters measurement or the dielectric supporting plate of the antenna setup shown in Figure III.11). In order to avoid such issues and obtain a good correlation between simulation and measurements two solutions can be envisaged: (i) redesign this antenna by using a reflector/ground plane properly positioned behind the antenna and (ii) re-simulate the antenna taking into account a representative 3D model of the surrounding environment.

Table III.3: Parametric study of angle  $\alpha$  effect on radiation.

| α (°) | fc (GHz) | Return Loss (dB) | Maximum Gain | HPBW (°) |

|-------|----------|------------------|--------------|----------|

| 40    | 59.7     | -21.09           | 4.14         | 82       |

| 45    | 60.2     | -22.76           | 4.02         | 86       |

| 50    | 61.15    | -27.48           | 40.8         | 90       |

## **III.4** Humidity test

The humidity test method is based on IPC-TM-650 2.6.2.1 standard technique[44]. The test samples were firstly dry out in an oven for over 30 minutes at 150 °C, each of them was individually weighed immediately. Then the test samples were immersed in a crystallizing dish filled with deionized water for 12 hours (hr). Each sample was removed independently from the water and sprays dried with nitrogen and weighed again. The same process was repeated for 24 hr and 48 hr respectively. The weight was increased with 1.64% after 12 hr, 1.78% after 24 hr and 1.81% after 48 hr.

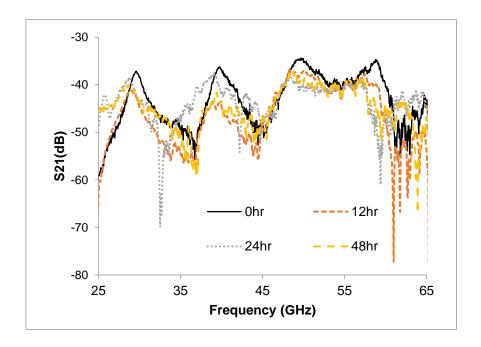

Figure III.28: Measured transmission coefficient of the ring resonator: initial state/0hr (continuous black line), measure after 12hr (red line, square dot), measure after 24hr (green line, circular dot), measure after 48hr (violet, dashed line).

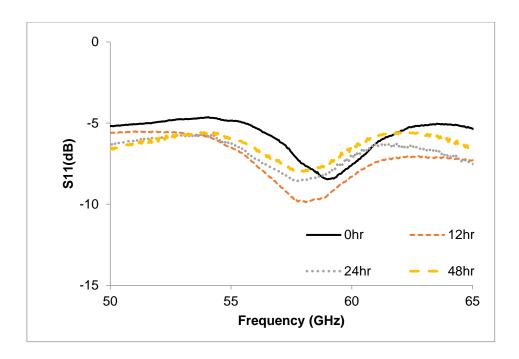

Figure III.29: Measured reflection coefficient of the microstrip patch antenna: initial state/0hr (continuous black line), measure after 12hr (red line, square dot), measure after 24hr (green line, circular dot), measure after 48hr (violet, dashed line).

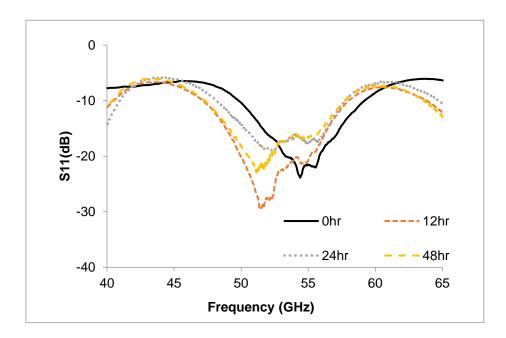

Figure III.30: Measured reflection coefficient of the crossed slot dipole antenna: initial state/0hr (continuous black line), measure after 12hr (red line, square dot), measure after 24hr (green line, circular dot), measure after 48hr (violet, dashed line).

The S-parameters measurements were carried out right after the weighing of the samples. Figure III.28 shows the results obtained for the ring resonator, the patch

antenna and the crossed slot dipole antenna. The extracted values for the relative dielectric permittivity are reported in Table. II taking into account the associated tolerances.

Figure III.29 and Figure III.30 show the measured reflection coefficient for the patch and the crossed slot antenna respectively. One can see that the frequency resonance is shifted to the lower frequency because the relative permittivity of the substrate was increased after water immersion as depicted in Table III.4. Also, the S11 decreases because the dielectric losses increase due to water exposition. The input matching of the patch antenna is (only) -8.2 dB mainly due to the transition between microstrip and CPW line. This input matching should appear to be poor but it is not unusual for V-band antennas. For example, the coplanar square monopole antenna proposed in [25] presents a measured S11 in the range of -11 dB at 58 GHz despite of the use of an 'intrinsic' CPW excitation. The second antenna (shown in Figure III.30) exhibits better performances: S11 < -20 dB in a 2 GHz bandwidth mainly due to its intrinsic CPW excitation and wideband behavior.

Table III.4: Extracted dielectric constant and dielectric loss.

| Time  | $\epsilon_{\rm r}$ | Tolerance of $\epsilon_r$ | tanδ  | Tolerance of tano |

|-------|--------------------|---------------------------|-------|-------------------|

| 0 hr  | 3.2                | +/- 0.08                  | 0.016 | +/- 0.005         |

| 12 hr | 3.4                | +/- 0.06                  | 0.03  | +/- 0.008         |

| 24 hr | 3.6                | +/- 0.08                  | 0.04  | +/- 0.006         |

| 48 hr | 3.7                | +/- 0.09                  | 0.045 | +/- 0.008         |

#### III.5 Conclusion

This chapter provides the prerequisites for the heterogeneous integration of wireless communicating node. First, the RF characterization of Kapton is given by measuring a ring resonator. Then, several antennas were designed, fabricated and measured for the implementation of WSN. These antennas will be later combined with the transceiver block.

A standard humidity test was performed in the V band. The experimental results demonstrate that the dielectric constant of the Kapton increases with maximum 15.6 % (up to 3.7 from 3.2 the initial value) and the dielectric losses increases with maximum 181% (up to 0.045 from the initial value of 0.016) when the Kapton structure were immersed in water after 48 hours. A limitation of the water absorption was also observed after 24 hours of the water immersion.

Based on the devices described in this chapter, the following chapter describes the microfabrication process adopted for circuit with electrical patterns on single/both side of the substrate.

# IV. Technological process for passive elements on flexible substrate

#### IV.1 Introduction

The previous chapter presented the implementation of the antennas on flexible substrate, which are the key building components to build a wireless communicating node. For the device which has electrical patterns on only one side, such as patch antenna or cross slot dipole antenna, wet etching process is adapted. For the device which has electrical patterns on both side of the substrate, wet etching process is used for the top side pattern, and lift off process is used for the backside.

This chapter presents in detail the microfabrication process used to implement RF circuits on flexible substrate, including the wet etching, and the lift off.

#### **IV.2** Substrate preparation

As discussed in chapter II.4, we use the PDMS to make adherence between polyimide film and the substrate host. The electrostatic forces between the Kapton film and the PDMS allow a free adhesion without adhesive and an easy peeling after manufacture.

#### IV.2.1 PDMS layer deposition

The PDMS deposition is generally done on a wafer which will be used in a spin coater to realize the PDMS membrane. A classical cleaning process is required for the host carrier (Silicon wafer or glass wafer). First, we need to clean the wafer with piranha solution, which is a mixture of sulfuric acid (H<sub>2</sub>SO<sub>4</sub>) and hydrogen peroxide (H<sub>2</sub>O<sub>2</sub>), the H<sub>2</sub>SO<sub>4</sub> can help reduces organics to carbon while H<sub>2</sub>O<sub>2</sub> can oxidize carbon to form CO<sub>2</sub>. Then an oxygen plasma treatment (optional) during 5 minutes can help remove all moisture on the surface.

The PDMS membrane is made by spin coating the PDMS on the substrate, so the PDMS has to be prepared. It means, mixing of the monomer and the curing agent and degassing the PDMS. The PDMS we used is the Sylgard 184 from Dow Corning. For this PDMS the usual ratio between the PDMS and the curing agent is 10:1 (weight). The order is

put first the PDMS then the curing agent, doing the opposite may lead to a bad cross linkage of the polymer. Once the PMDS is mixed, it is placed in a vacuum desiccator for degassing (30 minutes).

Figure IV.1: Sylgard 184 part A and Part B.

Figure IV.2: Vacuum desiccator.

The most relevant step is the spin coating of the PDMS since the speed, the acceleration and the time of the spin coating will define the thickness of the layer. In this work, the recipe employed is 5000 rpm, 5000 rpm/s and 30 seconds, to obtain a PMDS layer as thin  $(5 \mu m)$  as possible:

- To guarantee the best homogeneity thickness

- To limit the vacuum degassing

- To limit swelling on the chemical stages

Finally, the film of deposited PDMS is polymerized in an oven at 120°C during 2 hours, or a rapid curing on a hotplate temperature to 150°C for 10 minutes.

#### IV.2.2 Kapton film preparation

First, we need to cut the Kapton tape into shape of 4-inches wafer, so we can later laminate the polyimide onto the Silicon wafer. We made the choice of 4-inches wafer as the host carrier respect to our micro technologies equipment.

Figure IV.3: Cut Kapton tape into a 4-inches wafer shape.

The substrate need to be properly cleaned to prevent a poorly adhesion of the deposited metal on the substrate, and obtain a higher purity of metal deposition. But unlike the classical cleaning process used for silicon wafer, to remove all the moisture on Kapton, we need:

- 1. Soaking Kapton in a crystallizing dish filled with Xylene during 5 minutes to remove any hydrocarbon contamination.

- 2. Rinsing with wash bottle contains Xylene.

- 3. Soaking Kapton in a crystallizing dish filled with Acetone during 5 minutes to remove Xylene.

- 4. Rinsing with wash bottle contains Acetone.

- 5. Soaking Kapton in a crystallizing dish filled with Ethanol during 5 minutes to remove Acetone.

- 6. Rinsing with wash bottle contains Ethanol.

- 7. Rinsing with deionized water to remove all trace of previous chemical.

- 8. Blow drying with a nitrogen gun.