# Contribution to the development of massively parallel radio frequency SoC architectures in advanced CMOS technologies

Reda Kasri

## ▶ To cite this version:

Reda Kasri. Contribution to the development of massively parallel radio frequency SoC architectures in advanced CMOS technologies. Micro and nanotechnologies/Microelectronics. Université Toulouse 3 Paul Sabatier (UT3 Paul Sabatier), 2017. English. NNT: . tel-01987950

# HAL Id: tel-01987950 https://laas.hal.science/tel-01987950

Submitted on 21 Jan 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE

En vue de l'obtention du

# DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE

**Délivré par :** l'Université Toulouse 3 Paul Sabatier (UT3 Paul Sabatier)

## Présentée et soutenue le 20/11/2017 par :

#### Reda Kasri

Contribution au développement d'architectures SoC radio fréquences massivement parallèles en technologies CMOS avancées

#### **IURY**

| MME NATHALIE DELTIMPLE | Maître de conférences HDR        | Rapporteur         |

|------------------------|----------------------------------|--------------------|

| M. Bernard Jarry       | Professeur d'Université          | Rapporteur         |

| M. Andreas Kaiser      | Professeur d'Université          | Membre du Jury     |

| M. Jean-Guy Tartarin   | Professeur d'Université          | Membre du Jury     |

| M. PHILIPPE CATHELIN   | Ingénieur R&D STMicroelectronics | Membre du Jury     |

| M. Éric Tournier       | Maître de conférences HDR        | Directeur de Thèse |

|                        |                                  |                    |

## École doctorale et spécialité :

GEET : Micro et Nanosystèmes

Unité de Recherche:

LAAS

Directeur de Thèse :

Éric Tournier

Rapporteurs:

Mme Nathalie Deltimple et M. Bernard Jarry

# Acknowledgements

Firstly, I would like to express my sincere gratitude to my advisor assoc. prof. Éric Tournier along with co-advisors: ing. Philippe Cathelin, dr.ing. Eric Klumperink and prof. dr. ir. Bram Nauta, for the continuous support of my Ph.D study and related research, for their patience, motivation, and immense knowledge. Their guidance helped me in all the time of research and writing of this thesis. I could not have imagined having better advisors and mentors for my Ph.D study.

Besides my advisors, I would like to thank the rest of my thesis committee: assoc. prof. Nathalie DELTIMPLE, prof. Bernard JARRY, prof. Andreas KAISER and prof. Jean-Guy TARTARIN, for their insightful comments and encouragement, but also for the hard questions which incented me to widen my research from various perspectives.

A very special gratitude goes out to ing. Sylvain CLERC, for his help on digital Flow. Without his precious support it would not have been possible to conduct this research.

I thank my fellow labmates both in STMicroelectronics and in ICD groupe in University of Twente for the stimulating discussions, for the sleepless nights we were working together before deadlines, and for all the fun we have had in the last four years.

Last but not the least, I would like to thank my family: my parents and my sisters for supporting me spiritually throughout writing this thesis and my life in general.

# **Contents**

| A  | knov       | wledgements                                                          | j                |

|----|------------|----------------------------------------------------------------------|------------------|

| In | Mot<br>Des | ivation ivation and objectives                                       | 1<br>1<br>2<br>3 |

| 1  | Stat       | e of the art of massively parallel reception                         | 5                |

|    | 1.1        | Introduction                                                         | 5                |

|    | 1.2        | Digital-to-Analog Converter+Direct Digital Frequency Syn-            |                  |

|    |            | thesis in the reference path of PLL                                  | 5                |

|    | 1.3        | A Direct Digital Frequency Synthesis driving segmented Gilbert       |                  |

|    |            | mixer                                                                | 6                |

|    | 1.4        | Full Spectrum Capture                                                | 8                |

|    | 1.5        | Conclusion                                                           | 9                |

| 2  | $G_m$      | N-path based receiver genesis                                        | 11               |

|    | 2.1        | Introduction                                                         | 11               |

|    | 2.2        | <i>N</i> -path based receiver presentation                           | 11               |

|    |            | 2.2.1 <i>N</i> -path filter definition                               | 11               |

|    |            | 2.2.2 <i>N</i> -path filter used as a receiver                       | 13               |

|    | 2.3        | N-path filter input impedance calculation                            | 16               |

|    |            | 2.3.1 Input impedance of Linear Time-Invariant <i>N</i> -path filter | 16               |

|    |            | 2.3.2 Input impedance of Linear Time-Varying <i>N</i> -path filter   | 20               |

|    |            | 2.3.3 Use of switch resistance ( $R_{sw}$ ) for input impedance      |                  |

|    |            |                                                                      | 23               |

|    | 2.4        |                                                                      | 23               |

|    | 2.5        | 1                                                                    | 27               |

|    | 2.6        | Conclusion                                                           | 28               |

| 3  | Pow        | ver Efficiency Comparison of Mixer-DAC and FSC                       | <b>3</b> 1       |

|    | 3.1        |                                                                      | 31               |

|    | 3.2        | Presentation of the two compared architectures                       | 32               |

|    |            | 3.2.1 Full Spectrum Capture                                          | 32               |

|    |            | 3.2.2 Mixer-DAC receiver                                             | 33               |

|          | 3.3 Full Spectrum Capture and mixer-DAC power efficiency com- |         |                                                         |                  |

|----------|---------------------------------------------------------------|---------|---------------------------------------------------------|------------------|

|          |                                                               | pariso  | n in DOCSIS context                                     | 33               |

|          |                                                               | 3.3.1   | Comparison assumptions                                  | 33               |

|          |                                                               | 3.3.2   | Mixer-DAC: noise contributions vs power consumption     | 36               |

|          |                                                               | 3.3.3   | Full Spectrum Capture: noise contributions vs power     |                  |

|          |                                                               |         | consumption                                             | 43               |

|          |                                                               | 3.3.4   | Power consumption comparison: introduction of effi-     |                  |

|          |                                                               |         | ciency limit concept                                    | 44               |

|          | 3.4                                                           | Comp    | arison for other standards                              | 45               |

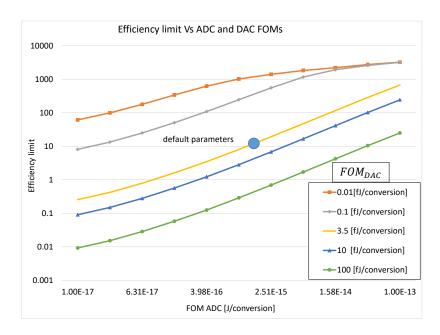

|          |                                                               | 3.4.1   | Efficiency limit versus ADC and DAC Figures Of Merit    | 46               |

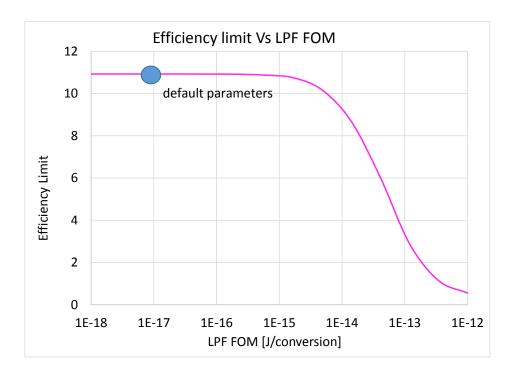

|          |                                                               | 3.4.2   | Efficiency limit versus Low Pass Filter Figure Of Merit | 47               |

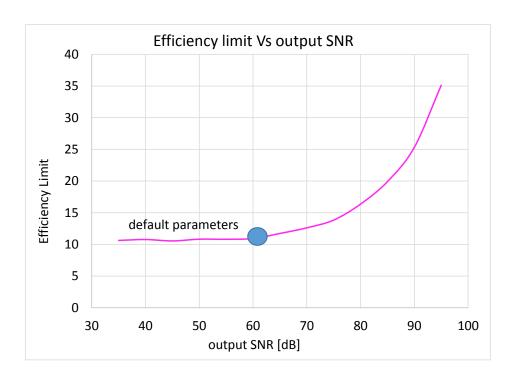

|          |                                                               | 3.4.3   | Efficiency limit versus Signal-to-Noise Ratio           | 47               |

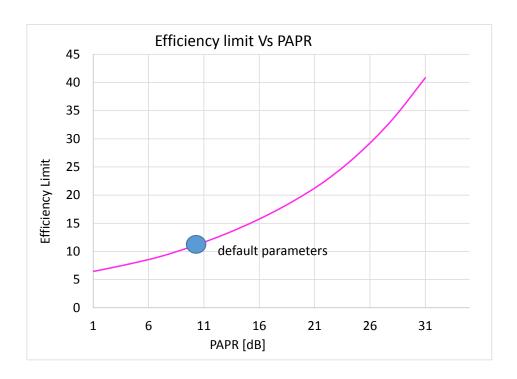

|          |                                                               | 3.4.4   | Efficiency limit versus Peak-to-Average Power Ratio     | 48               |

|          |                                                               | 3.4.5   | Efficiency limit versus number of channels and maxi-    |                  |

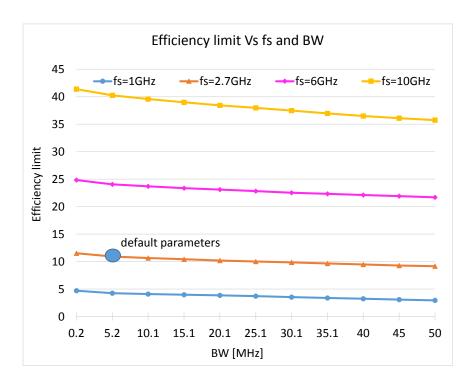

|          |                                                               |         | mum frequency channel                                   | 48               |

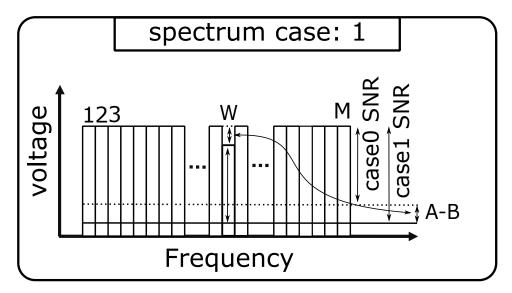

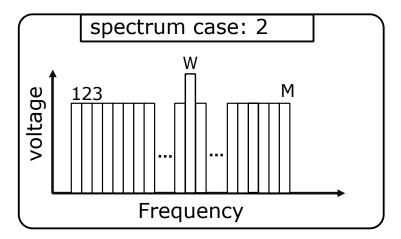

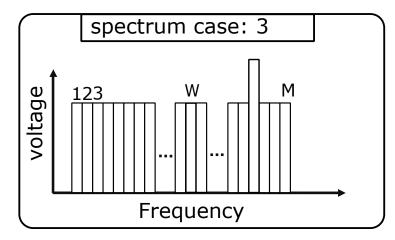

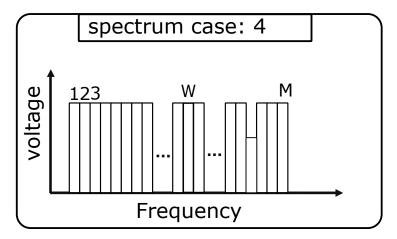

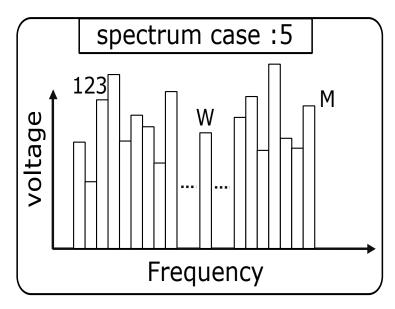

|          |                                                               | 3.4.6   | Comparison results for other spectrum cases             | 50               |

|          | 3.5                                                           | Comp    | arison conclusion                                       | 54               |

|          | <b>C1.</b>                                                    |         |                                                         |                  |

| 4        |                                                               | •       | ementation and measurements                             | 57               |

|          | 4.1                                                           |         | luction                                                 | 57<br><b>-</b> 2 |

|          | 4.2                                                           | -       | sed circuit                                             | 58               |

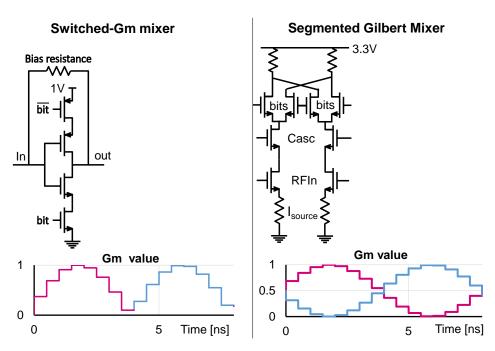

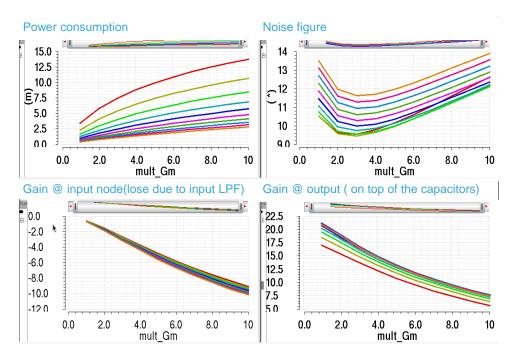

|          |                                                               | 4.2.1   | Switched- $G_m$ mixer low power benefit over segmented  |                  |

|          |                                                               |         | Gilbert mixer                                           | 60               |

|          |                                                               | 4.2.2   | The 2-path also filters the RF signal                   | 62               |

|          |                                                               | 4.2.3   | The implemented demonstrator                            | 62               |

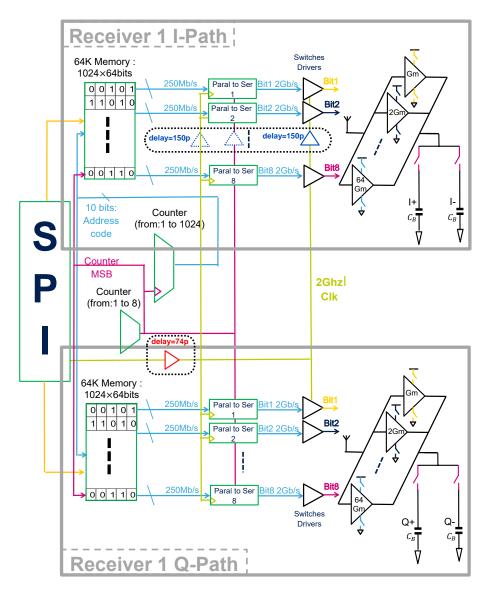

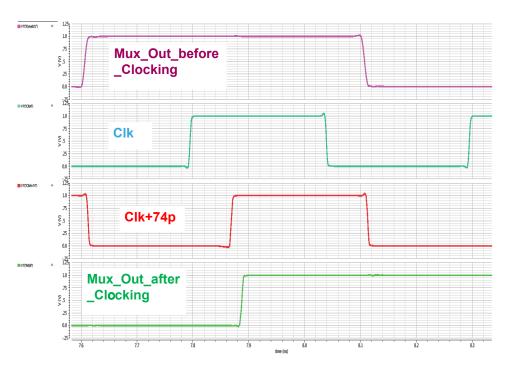

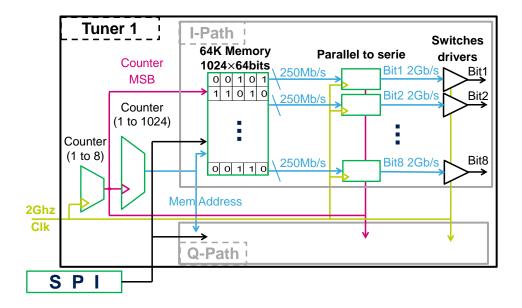

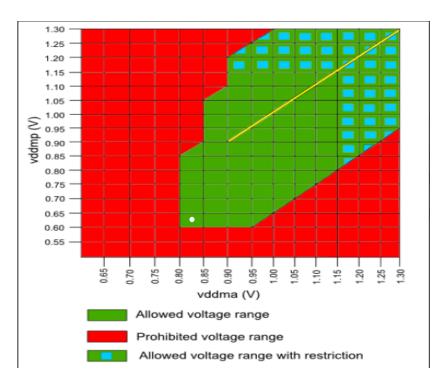

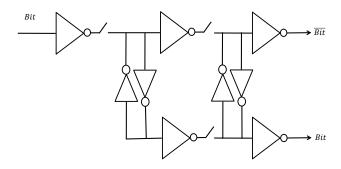

|          |                                                               | 4.2.4   | The implemented Direct Digital Frequency Synthesis      | 65               |

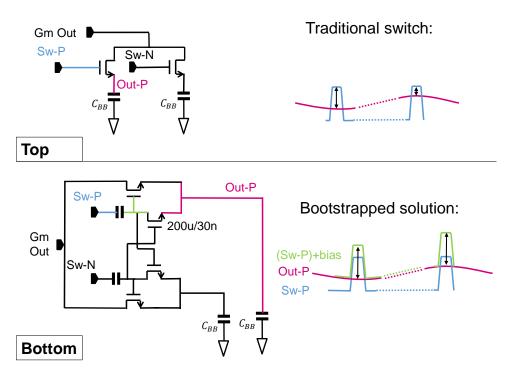

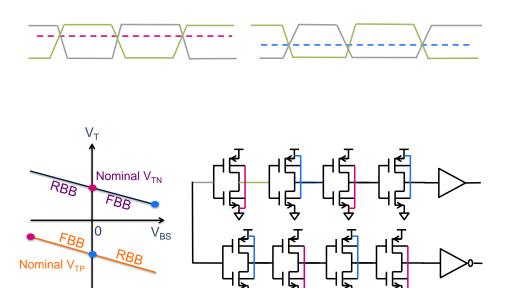

|          |                                                               | 4.2.5   | Capacitor switch                                        | 69               |

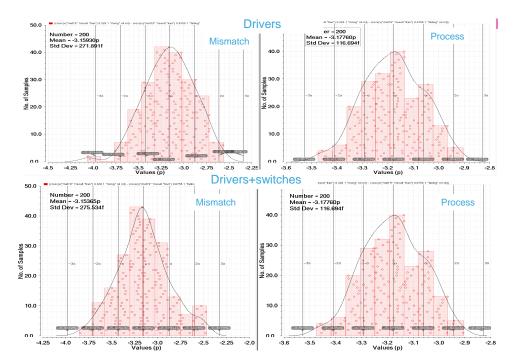

|          |                                                               | 4.2.6   | $G_m$ switch driver                                     | 71               |

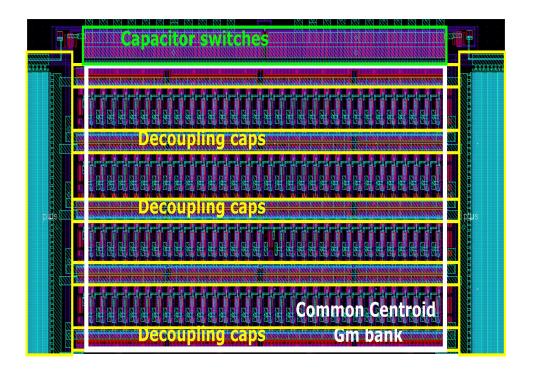

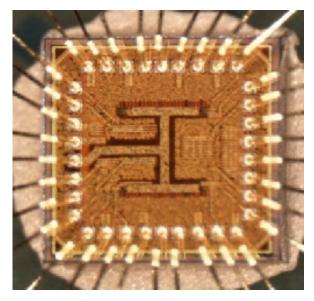

|          |                                                               | 4.2.7   | Mixer-DAC layout and chip photo                         | 71               |

|          | 4.3                                                           |         | ench                                                    | 73               |

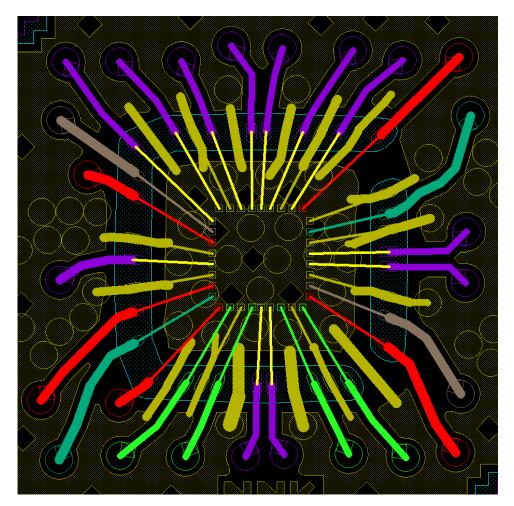

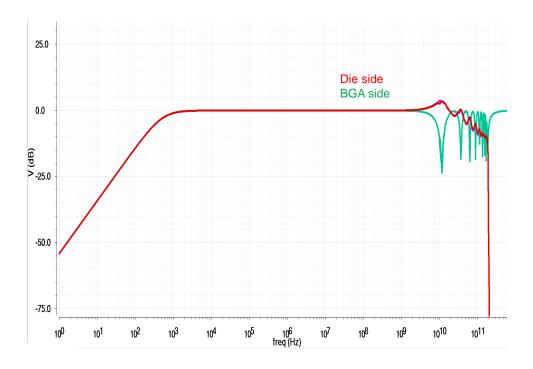

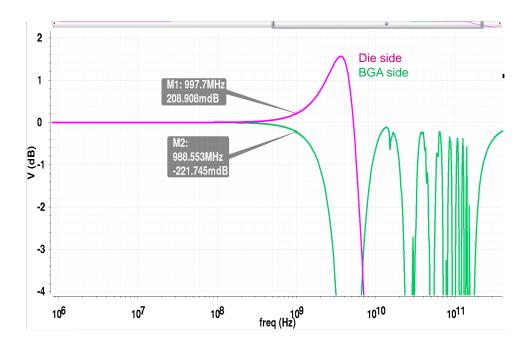

|          |                                                               | 4.3.1   | Ball Grid Array design description                      | 73               |

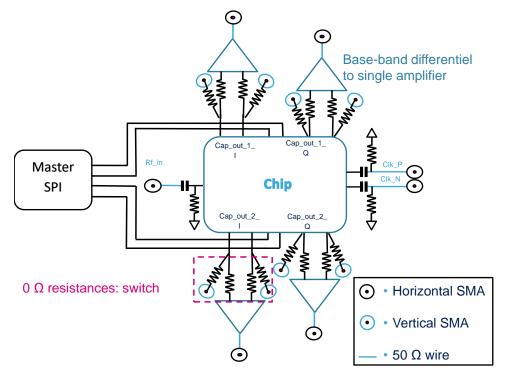

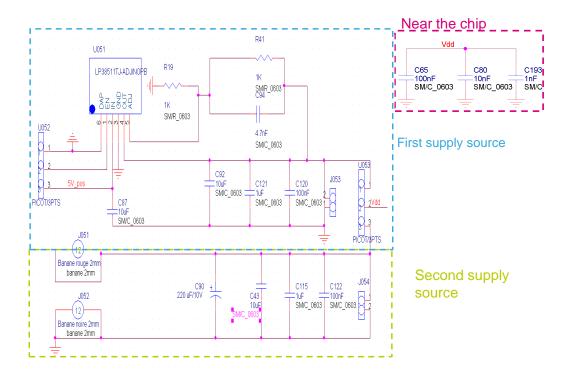

|          |                                                               | 4.3.2   | Printed Circuit Board design description                | 74               |

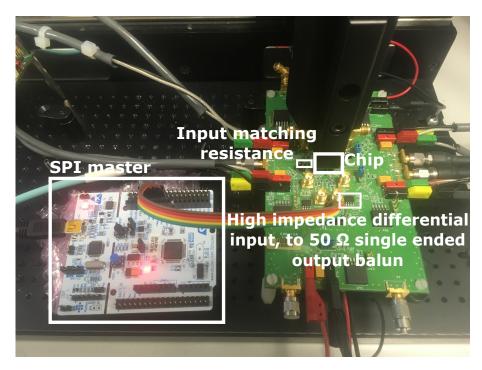

|          |                                                               | 4.3.3   | Measurement bench                                       | 76               |

|          | 4.4                                                           |         | urements results                                        | 78               |

|          | 4.5                                                           | Concl   | usion                                                   | 84               |

| G        | enera                                                         | l concl | usion and perspectives                                  | 85               |

| <b>J</b> |                                                               |         |                                                         | 85               |

|          |                                                               |         | k                                                       | 87               |

|          |                                                               |         | lication                                                | 88               |

|          | -104                                                          | or han  |                                                         |                  |

| A Appendix: input impedance of LTV $N$ -path c | alculation 89 |

|------------------------------------------------|---------------|

| Bibliography                                   | 95            |

v

# Introduction

## Motivation and objectives

Parallel radio reception stands for a system capable of extracting, from the electromagnetic spectrum, more than one signal data stream, carried by different and arbitrary distributed carrier frequencies. This definition can be extended to massive parallel reception, where the system purpose is to receive a large number of channels. Behind this definition, we can recognize some well known applications:

- Digital TV reception (terrestrial, satellite or cable) where a hundred of programs are transmitted in a 1 GHz band.

- Internet Of Things (IOT), where a sensor node must wait for signals coming from different relays.

- Cellular communications, where LTE (4G) standard uses aggregation of carriers, which may be located in different frequency bands, to increase the data-rate. 5G standards will even push this principle further, enabling the aggregation of non exogenous signals (WiFi and LTE, mmW and RF ...)[1], [2].

Of course, when addressing massive parallel reception, energy efficiency and monolithic integration constraints have to be fulfilled:

- Energy efficiency, because solution must be compatible with portable devices.

- Monolithic integration for cost and volume constraints. This monolithic integration has to be compliant with a System On Chip approach (SOC), meaning that the technology must be an advanced CMOS.

Finally, parallel reception is already linked to hot research areas:

- Re-configurable radio receivers or Software-defined radio (SDR).

- Wide band reception.

2 Contents

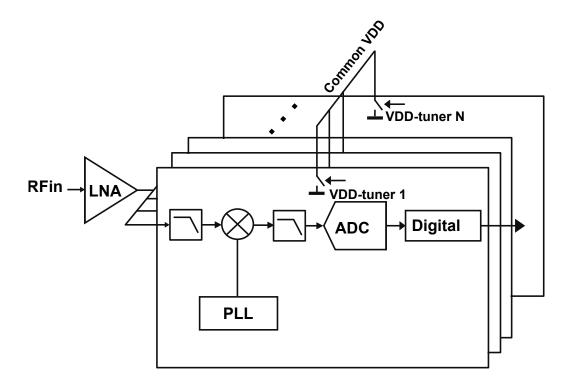

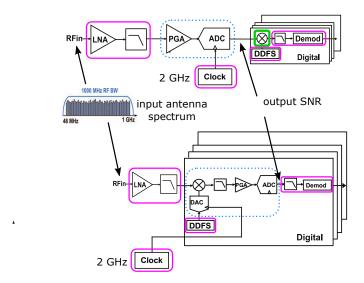

FIGURE 1: *N* RF traditional receivers in parallel.

# Design challenges

The straight forward way to tackle massively parallel reception would be to put in parallel as many RF traditional receivers as needed (Fig. 1). With the latter solution, the total signal would be first amplified by a common Low Noise Amplifier (LNA), then every single receiver would down-convert its wanted signal to baseband, where it undergoes filtering and digitization through a baseband Analog-to-Digital Converter (ADC).

However, the integration of multiple uncorrelated clocks on the same chip leads inevitably to some issues:

- In case of a monolithic integration, the harmonics of all operating VCOs and all the spurs of the fractional dividers will couple to LNA input. The number of these spurs will become too large to consider interference mitigation schemes.

- Having multiple Voltage Controlled Oscillators (VCO), on the same chip, with frequencies in the same range, will produce Voltage Controlled Oscillator (VCO) pulling, degrading reception [3]–[6].

Contents 3

• LNA and mixer, which have to handle the full RF band, will exhibit a poor linearity degrading the overall Signal-to-Noise Ratio (SNR).

• High area, mainly for clock generation.

To conclude this section , we can state that monolithic integration of parallel receivers will force to solve two challenges:

- Generation of arbitrarily distributed clock frequencies while keeping a "reasonable" amount of spurs.

- Management of the wide band aspects, meaning low harmonic mixing and high linearity constraints.

#### Thesis outline

In chapter 1 we show the main existing solution solving part of massively parallel reception challenges. In chapter 2, the *N*-path receiver is presented along with the problems it faces when used in a massively parallel configuration. Some solutions to these problems are then provided and a massively-parallel-friendly solution based on *N*-path is finally proposed.

Power efficiency comparison, with respect to the number of received channels, between a traditional solution and the latter *N*-path based solution will be done in chapter 3.

In chapter 4, a circuit, demonstrating the feasibility of the proposed architecture and its compatibility with massive parallel reception is proposed. The details of the implementation as well as simulations and measurements results are discussed.

Finally, a conclusion and future work in the last chapter.

# Chapter 1

# State of the art of massively parallel reception

#### 1.1 Introduction

Massively parallel reception started to be an area of interest only in the past few years, it combines two difficulties:

- Designing a reconfigurable radio receiver (which was already targeted in SDR researches).

- Managing the cohabitation of a large number of such a receiver on the same chip (Spurs, Area, energy efficiency ...).

In this chapter, we will report studies addressing at least one of these aspects, describe principle involved and point limitations.

# 1.2 Digital-to-Analog Converter+Direct Digital Frequency Synthesis in the reference path of PLL

One partial solution to the massively parallel reception is the "Digital-to-Analog Converter (DAC)+Direct Digital Frequency Synthesis (DDFS) in the reference path of Phase Locked Loop (PLL)" [7]. This solution exploits a DAC+DDFS combined to a Band Pass Filter (BPF) at the PLL reference path. This DAC+DDFS+BPF combination, allows to generate any wanted low frequency clock, that can be used in the reference path of an integer frequency-divider PLL. The frequency flexibility is therefore obtained by the combination of a tunable reference frequency and integer frequency-divider, and not through the combination of a fractional frequency divider and a fixed frequency reference as usually done. Thus, we can afford a wide range flexible PLL without using a fractional divider that comes inevitably with interferences. Therefore, if compared to a classical solution that includes

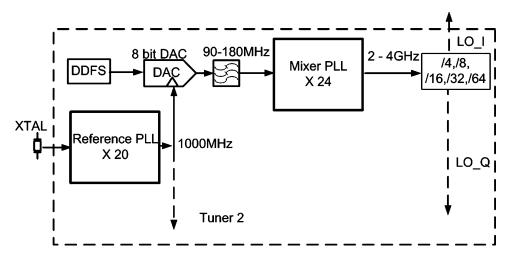

FIGURE 1.1: F. Gatta [7] LO generation block.

fractional dividers, this solution is more robust to interferences, even if it still suffers from the VCO harmonics that will couple to other VCO and may lead to VCO pulling.

This solution proposes a novel idea to get rid of fractional dividers and thus reduce the amount of spurs, but it is only a part of the problem: one PLL per receiver is still needed, and this will impact circuit area. Moreover, having a sine-wave reference, involves inevitably the use of a mixer-based PLL, instead of the traditional, low phase-noise, Charge Pump based PLL.

# 1.3 A Direct Digital Frequency Synthesis driving segmented Gilbert mixer

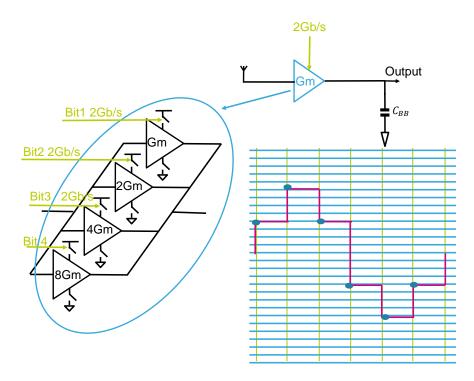

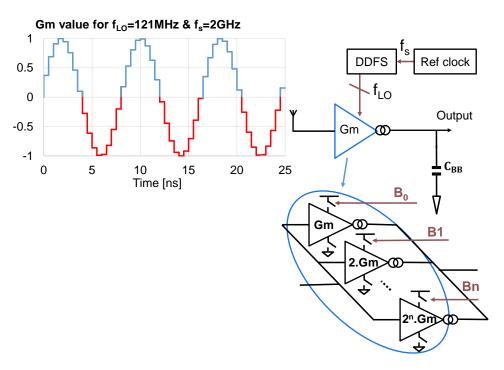

The figure Fig 1.2 present a DDFS driving a segmented Gilbert mixer [8]. This solution exploits a 10 binary weighted Gilbert mixer set, realizing a mixer-DAC behavior. This mixer-DAC is driven by a 10 bit DDFS. Many parallel receivers can thus be put in parallel while still being driven by a single analog-clock, which prevents clock interference problems from occurring.

The Direct Digital Frequency Synthesis (DDFS) is generally based on a Static Random Access Memory (SRAM), in which are stored the samples of a walking sine-wave, thus the interferences that a DDFS can cause are very low compared to the ones that can be created using an analog-clock. Indeed the interference inter-analog-clocks are mainly due to:

the use of an inductor in the VCO that will produce an electromagnetic field that could disturb other working VCO's inductors, known as VCO pulling [3].

FIGURE 1.2: A. Maxim [8] receiver architecture.

• the high current drawn by the frequency dividers, at Local Oscillator (LO) frequency, that transform to voltage drop at the different VDD nodes of the circuit due to the VDD wire resistance. That can also disturb other working VCO's that will see a variation in their own VDD and can cause VCO pulling [3].

A DDFS do not have an inductor, preventing it from the first source of interference. The current drawn by the DDFS would be at the sampling frequency and not at the sine wave LO, providing to the DDFS based receivers much more robustness to interference.

Drawback of this solution is the difficulty to obtain sufficient linearity. No RF filtering is present, meaning that LNA output and mixer input signal is the sum of all signals present at the antenna and thus both will need to be extremely linear. This linearity constraint will translate in current consumption: The circuit presented in the paper consumes 500 mW for a single I/Q receiver. This solution proposes to generate the LO signal from a DDFS, which is a good solution to avoid spurs coming from LO path, but segmented Gilbert-cell approach make it incompatible with massive parallel reception.

FIGURE 1.3: Full spectrum capture architecture [9].

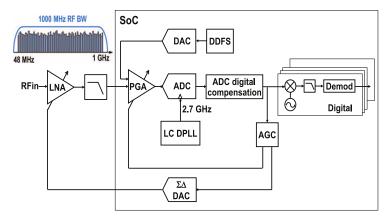

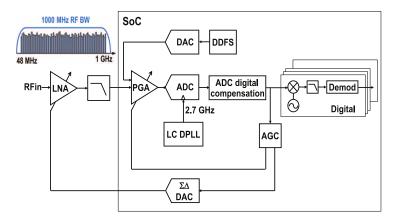

# 1.4 Full Spectrum Capture

The Full Spectrum Capture (FSC) shown a in fig. 1.3 is an ADC-first receiver, that digitizes the full antenna spectrum. Every received channel is then processed digitally through a Digital Channel Selection (DCS) block. This architecture solves the need of a clean LO-generation by using a unique clock and DCS blocks; mixing in digital with a DDFS helps overcome the harmonic mixing problem (harmonic mixing level can be lowered by properly selecting the number of bits). This solution simply translates the analog processing blocks to the digital domain, giving them an ultimate flexibility. Moreover, a digital filter or mixer block consumes less power compared to its analog counterpart with the same performances. However, the power consumption reduction at the digital blocks is replaced by a very high power consumption of the ADC<sup>1</sup>.

FSC receiver was long considered as a solution for cognitive radio. It was first introduced in [10] (Mitolla sofware radio), but the high bandwidth and high resolution ADCs it required were impossible to achieve at the time. For example, digitizing the frequency band from 800 MHz to 5.5 GHz, where all of today's cellular and WLAN channels lie, will require a 12 bit, 11 GS/s ADC [11].

To conclude, the challenge in the analog design becomes an ADC design challenge (example: 12 bits and  $f_S = 2.7 \,\text{GHz}$  for DOCSIS). This solution suffers from drawbacks:

The consumption remains almost the same, for whatever number of really used channels.

<sup>&</sup>lt;sup>1</sup>this is a general remark for receivers architecture, that digital blocks consume less than RF ones, but the high power consumption of the ADC that had to digitize the whole spectrum, binds us to use RF pre-processing of the signal

1.5. Conclusion 9

FIGURE 1.4: B. Murmann ADC survey [12].

- If the standard only uses some portions of the spectrum (cellular as an example), efficiency reduces (as the power consumption remain the same).

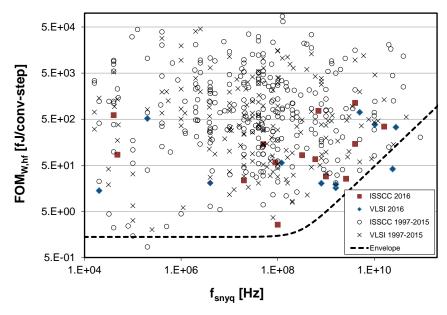

- The power consumption grows in a quadratic fashion with sampling frequency [12] (fig. 1.4 for frequencies above 100 MHz and thus the maximum signal frequency (the sampling frequency must be two time higher than the maximum signal frequency).

#### 1.5 Conclusion

None of the presented solutions will be the ultimate solution for massive parallel reception. FSC has advantages, but can be considered relatively power hungry when only few channels are really used at the same time or when the useful spectrum is sparse. The two other solutions do not have this issue, but both are based on traditional (mixer based) receivers capable of working on a wide band (and thus without RF filtering) with a large quantity of blockers. This will put a linearity constraint on the mixer that will be solved with additional current consumption. To get rid of this problem, solution must provide some RF (before mixer) filtering. This characteristic is provided by *N*-path receivers, motivating to start the seek for a new architecture with detailed *N*-path study.

# **Chapter 2**

# $G_m$ N-path based receiver genesis

#### 2.1 Introduction

In the last chapter we presented the state of the art for parallel receivers, where the FSC drawbacks motivated us to look for an alternative receiver architecture, of which power consumption scales with the number of received channels and which includes RF filtering. One promising architecture that include RF filtering along with power and area efficiency is the N-path receiver. In the first section, we present the N-path filter and the N-path receiver along with its drawbacks, that are mainly the input impedance and the harmonic mixing. Then in the second section, an intuitive way to calculate input impedance is presented, and some solutions to get rid of the input impedance drawback are presented. one solution to the input impedance problem is to combine a  $G_m$  block to the N-path receiver, presented in the section 2.3. This  $G_m$  N-path receiver still suffer from harmonic mixing, which can be solved by the use of a  $G_m$  N-path based mixer-DAC that is presented in section 2.4.

# 2.2 N-path based receiver presentation

# 2.2.1 N-path filter definition

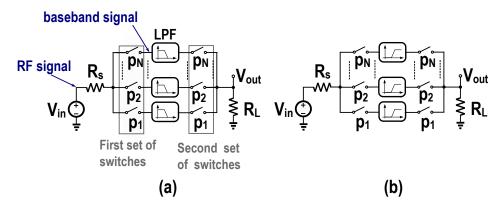

The *N*-path filter is a BPF circuit, illustrated in fig. 2.1(a) [13], where the first set of switches realizes a multi-phase passive mixer that down-converts the input RF signal to baseband. Then, this down-converted signal is low-pass filtered through the LPF. Finally the filtered signal is up-converted through the second set of switches. This implements, when both pairs of switches are driven with the same frequency (LO frequency) a BPF with a center frequency of LO and a 3 dB bandwidth equal to twice the BPF bandwidth. The main benefit of this architecture is that the cut off frequency of the Low

FIGURE 2.1: N-path architecture: (a) BPF (b) BSF

Pass Filter (LPF) is independent of the mixing frequency, resulting in a high selectivity BPF (high Q)<sup>1</sup>:  $Q = \frac{f_{\text{mixer}}}{\Delta f}$  where  $f_{\text{mixer}}$  is both down-conversion and up-conversion frequency and  $\Delta f$  is the full width at half maximum of the filter transfer function (in this case equal to 2 times the cut off frequency of the LPF). For example, using a 1 MHz cut off frequency low pass filter, along with a 1 GHz mixing frequency, result in a Q = 500 BPF.

Similarly with BPF, fig. 2.1(b) [13] shows an *N*-path Band Stop Filter (BSF). It follows the same principal of the BPF, except that instead of using a LPF to pass the low frequency signals, it uses a High Pass Filter (HPF) to pass the high frequency signals, realizing a BSF behavior.

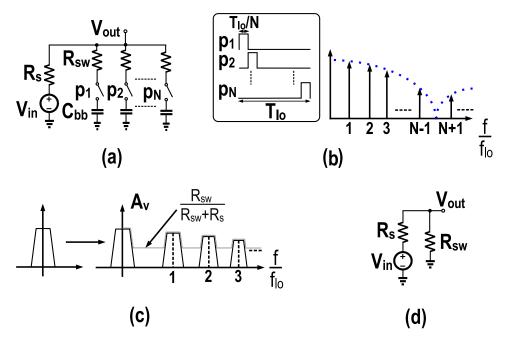

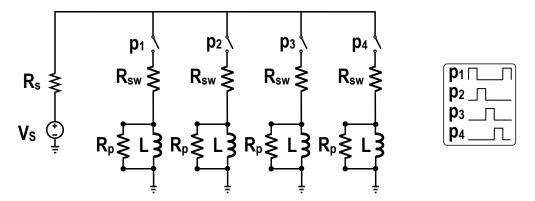

An implementation of an *N*-path BPF [13] is illustrated in fig. 2.2(a), where a simple capacitor is used to realize a LPF when combined to the switch and source resistors. In this implementation, the second set of switches are not needed, because by nature, a passive mixer is bidirectional and thus a single mixer can play both roles: down-mixer (from RF to baseband) and up-mixer (from baseband back to RF).

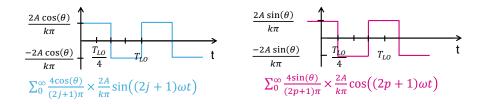

In a passive mixer implementation, it is forbidden to have the switches of two baseband sections on at the same time (this would short-circuit both and thus kill the filtering function). For this reason, square-LO signals must be non overlapping and thus will have a duty cycle of 1/N. The mixing signals are illustrated in fig. 2.2(b) along with its spectral decomposition (the dashed curve): this  $\frac{100}{N}$ % duty cycle signal contain on top of the fundamental  $f_{\text{LO}}$ , all its harmonics except  $k N f_{\text{LO}}$ .

The *N*-path can be intuitively seen as a passive mixer that translates the low-pass behavior of the RC network to create a band-pass behavior around the switching frequency, as shown in fig. 2.2(c), where the LPF

<sup>&</sup>lt;sup>1</sup>The quality factor (*Q* factor) is a dimensionless parameter that characterizes a resonator's bandwidth relative to its center frequency

FIGURE 2.2: (a) *N*-path implementation (b) Mixing signals: time and spectrum BPF (c) Transfer function (d) Equivalent circuit for out-of-band signals

transfer function is being translated around every one of the mixing signal spectral components. The input signals see either a high or low impedance, depending on its frequency as follow [14]:

- An input signal at  $f_{LO}$  or its harmonics sees a LPF behavior (or high input impedance as shown in fig. 2.2(c)), where the baseband capacitor holds the mean value of this in-band signal.

- An input signal at a different frequency sees only the switch resistance  $R_{sw}$ (or low input impedance as shown in fig. 2.2(c)), resulting in a simple voltage divider, as shown in fig. 2.2(d).

*N*-path filters are tunable low-power and low area filters, where the center frequency is totally tunable and independent of the filter sharpness. Indeed, the *N*-path filters present very good performances compared to other RF filters or receivers topologies<sup>2</sup> [15], making this architecture suitable for receiver architecture previously targeted in chapter 1.

## 2.2.2 N-path filter used as a receiver

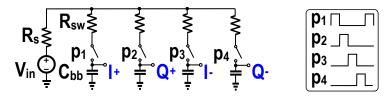

An N-path receiver is illustrated in fig. 2.3. It has the same implementation as fig. 2.2, with N=4 and considering the voltage at the capacitance nodes

<sup>&</sup>lt;sup>2</sup>We only consider tunable and low power low area topologies

FIGURE 2.3: *N*-path receiver

as output. This implementation benefits of the properties of N-path filter (filtering), while taking outputs on capacitors will bring baseband signal out of the circuit. On the other hand, the choice of N=4 will drive us towards  $90^{\circ}$  shifted LO signals. By properly choosing the outputs, one can construct in-phase differential and quadrature signals. An image reject mixer can thus be implemented simply by digitizing I and Q and calculating, in digital domain the I+jQ function.

The *N*-path has multiple advantages when used as a receiver, namely:

- Low power consumption: the circuit include both *I* and *Q* at the same time, using passive mixer and passive LPF, where the only power consumers are the clock generation block and the different switches drivers (not shown in the fig. 2.3).

- High linearity: the *N*-path implementation exhibits two major advantages in term of linearity:

- Passives mixers, as they only use the transistors in ON or OFF modes are inherently very linear.

- The fact that input impedance is low out of the bands is also a major advantage. All blockers will see a low impedance, resulting in a low voltage swing on the input, relaxing linearity constraints on switches and active devices, if any.

The *N*-path also have some disadvantages when used as a receiver, and some when used as parallel receivers:

- Harmonic rejection: the N-path down-converts the RF signals present at the fundamental frequency along with its harmonics, which results in the superposition of signals present in the antenna spectrum at  $f_{LO}$  harmonics, with the wanted signal.

- Low selectivity: selectivity of the N-path shown in fig. 2.2(a) cannot exceed  $\frac{R_{\text{sw}}}{R_{\text{sw}} + R_{\text{S}}}$  (voltage divider mentioned above, for input frequencies different from the mixing frequency).

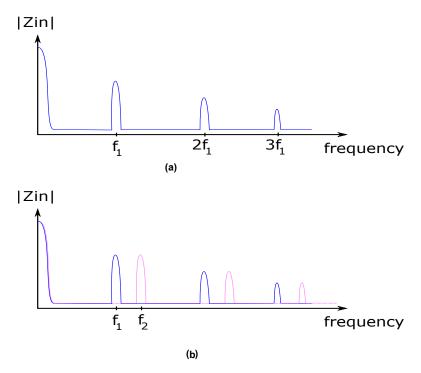

FIGURE 2.4: *N*-path input impedance of: (a) single *N*-path (b) 2 parallel *N*-paths at 2 different frequencies

• *N*-path input impedance: input impedance of a single *N*-path filter is depicted in fig. 2.4(a), while in fig. 2.4(b), two parallel *N*-paths with two different center frequencies are depicted. At  $f_1$  the first *N*-path have a high input impedance while the second *N*-path input impedance is very low: the second *N*-path acts like a shunt for the first one, around its receiving frequency. Putting two *N*-path receivers in parallel will thus cancel any signal present at the antenna.

We have three problems if we want to implement parallel reception with *N*-path filtering: harmonic mixing, selectivity and input impedance. *N*-path harmonic mixing and selectivity problems seems not that severe, and have been addressed and solved in [13], [16]. Input impedance become the bottleneck, that can be summarized as follow: it is obvious now that implementing parallel reception with *N*-path receivers built with simple RC filters, leads to shorting both receivers to ground, due to low out-of-band input impedance. Is there any other filter implementation that can solve this problem? In other words, can we, by carefully choosing the baseband filter, shape the *N*-path receiver so that input impedance becomes compatible with parallel reception?

For that study, a general analytic calculation of *N*-path receiver input impedance is needed. In next section, we will develop the input impedance

FIGURE 2.5: *N*-path receiver: general baseband impedance case.

FIGURE 2.6: LTI N-path input impedance: general circuit

formula of a general *N*-path shown in fig. 2.5, where the capacitor was replaced by a general impedance, that could be replaced by capacitor, inductor, resistor or a combination of two or more of them. First we assume Z to be replaced only by a combination of inductors and resistors (where the *N*-path remains an Linear Time-Invariant (LTI) system), then in a second time we introduce an intuitive method to calculate capacitor based *N*-path input-impedance.

# 2.3 N-path filter input impedance calculation

#### 2.3.1 Input impedance of Linear Time-Invariant N-path filter

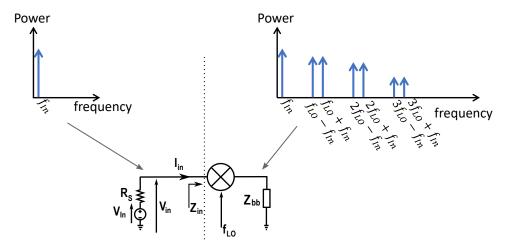

For LTI N-paths input impedance calculation, we consider the circuit shown in fig. 2.6, which is a single path ( $\frac{1}{N}$  of the N-path). Before the mixer, the input signal is a single spectral tone, that will transform after mixing with the  $\frac{100}{N}$ % duty cycle square-LO, to many spectral tones at  $f_{\rm in} \pm k f_{\rm LO}$ .

For this circuit we consider the power conservation equation 2.1, i.e. the input power is equal N time the power in one branch<sup>3</sup>, which is the sum of the power of tones at  $f_{in} \pm k$   $f_{LO}$ :

$<sup>^{3}</sup>$ The N branches are the same and do not overlap

FIGURE 2.7: *N*-path mixer: current mixing

$$P_{\text{in}} = N \cdot P_{\text{one path}}$$

$$= N \cdot \sum_{k=0}^{\infty} P_{\text{BB},k}$$

(2.1)

where  $P_{BB,k}$  is the power of the  $k^{th}$  tone in one branch.

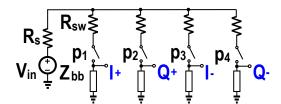

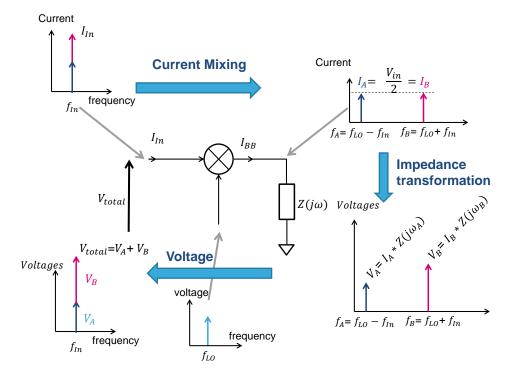

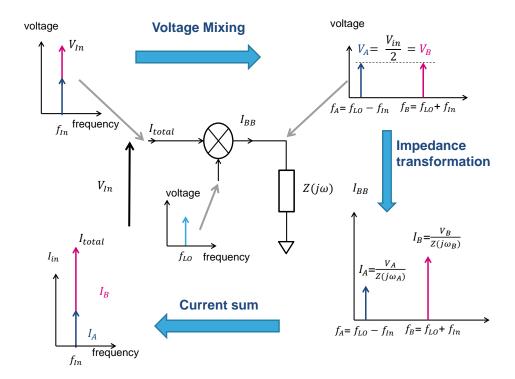

This passive mixer is considered as a current mixer [13], meaning that it's the RF current that splits into many baseband currents, at different frequencies, following the LO signal Fourier decomposition. Then, this different currents are transformed through the baseband impedance to voltages which sum up to produce the output voltage, as shown in fig. 2.7 for a single RF tone mixing with a single LO-tone. In opposition a voltage mixer is shown in fig. 2.8 for a single RF tone mixing with a single LO tone. In other words, due to mixing, we consider the input current that split in two equal tones, and not the RF voltage.

For a square-LO the RF current will splits in many baseband currents according to the square-LO signal Fourier decomposition (and it is not the RF voltage that split):

FIGURE 2.8: *N*-path mixer: voltage mixing

$$I_{\text{BB},k} = \alpha_k I_{\text{in}} \tag{2.2}$$

where  $\alpha_k$  is the  $k^{\text{th}}$  coefficient of the LO signal one-sided Fourier decomposition<sup>4</sup>.

The  $k^{\text{th}}$  baseband power expression  $P_{BB,k}$  can be deduced from:

$$P_{BB,k} = I_{BB,k}^2 Z_{BB,k}$$

(2.3)

combining 2.1, 2.2 and 2.3 we get:

$$P_{\rm in} = N I_{\rm in}^2 \sum_{k=0}^{\infty} \alpha_k^2 Z_{{\rm BB},k}$$

(2.4)

$P_{\rm in}$  can also be expressed as  $I_{\rm in}^2 \cdot Z_{\rm in,LTI}$ , resulting in:

$$I_{\text{in}}^2 \cdot Z_{\text{in,LTI}} = N I_{\text{in}}^2 \sum_{k=0}^{\infty} \alpha_k^2 Z_{\text{BB},k}$$

(2.5)

<sup>&</sup>lt;sup>4</sup>For a rectangular signal with amplitude *A* and duty-cycle *d*:  $\alpha_k = \frac{2A}{k\pi}\sin(k\pi d)$

FIGURE 2.9: LTI N-path input impedance: baseband inductors

FIGURE 2.10: LTI *N*-path input impedance: baseband capacitor

Finally if we simplify by  $I_{in}^2$ , we get:

$$Z_{\text{in,LTI}} = N \sum_{k=0}^{\infty} \alpha_k^2 Z_{\text{BB},k}$$

(2.6)

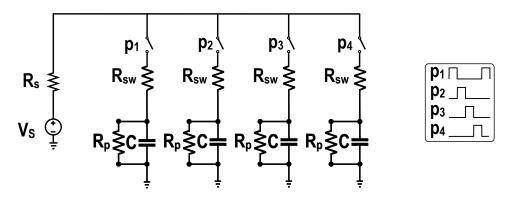

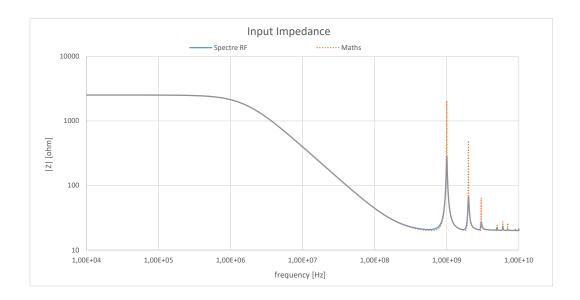

The later formula has been tested for an inductive baseband impedance shown in fig. 2.9, where a parallel resistor  $R_p$  was added to limit the impedance increase over frequency of the inductor (adding a parallel resistor is a more realistic case, moreover it helps the Spectre RF simulator to converge). Then, both simulated (Spectre RF) and calculated (Matlab using eq. 2.6) input impedance are plotted in fig. 2.11, where  $R_s = 50 \,\Omega$ ,  $R_{\rm sw} = 20 \,\Omega$ ,  $L = 10 \,\mu H$ ,  $R_p = 10 \,\mathrm{k}\Omega$  and  $f_{\rm LO} = 1 \,\mathrm{GHz}$ .

Note that when  $Z_{BB}$  is replaced by a resistor, the equation 2.6 simplifies to  $Z_{in} = N \left(\sum_{k=0}^{\infty} \alpha_k^2\right) R_{BB}$  where the parenthesis is equal to the LO amplitude, which is equal to 1/4 for one path. Finally, for a resistive N-path, the input impedance is equal to:

$$Z_{\text{in.resistor}} = R_{\text{BB}}$$

(2.7)

FIGURE 2.11: LTI N-path input impedance(simulation Vs calculus): inductors

Our model now being confirmed for LTI N-path, we tried the same formula for a capacitive baseband impedance N-path shown in fig. 2.10, and again both simulated (Spectre RF) and calculated (Matlab using eq. (2.6)) input impedance are plotted in fig. 2.12, where  $R_s = 50\,\Omega$ ,  $R_{\rm sw} = 20\,\Omega$ ,  $C = 100\,\mathrm{pF}$ ,  $R_p = 10\,\mathrm{k}\Omega$  and  $f_{\rm LO} = 1\,\mathrm{GHz}$ . In this figure, we can see that the mathematical calculus done through formula (2.6) does not fit simulation, especially around the mixing frequency and its harmonics, i.e. showing that more current is flowing in the simulation than in the calculated one. This difference was expected due to the use of an LTI model for this Linear Time-Varying (LTV) N-path. In the next section, we will investigate the input impedance of an LTV model through calculating the later "extra floating current" when using an LTI model for calculating LTV N-path.

## 2.3.2 Input impedance of Linear Time-Varying N-path filter

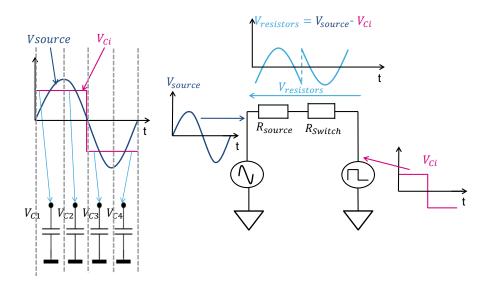

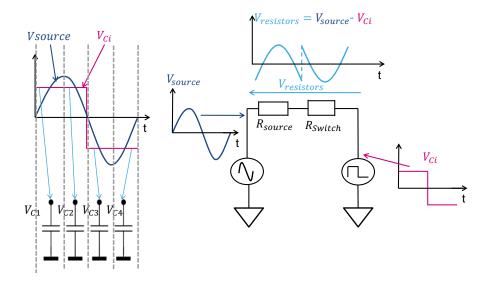

For an input signal at the same frequency as  $f_{LO}$ , each capacitor will always see the same quarter of the input sine-wave, for every switch-on window. The capacitor will thus hold the mean value of this quarter sine-wave. The combination of switch resistance and source resistance then sees a voltage difference equal to the input voltage minus its mean value held by the capacitor, resulting in a current flow equal to this voltage difference over the sum of resistances, as shown in fig. 2.13. This current average is equal

FIGURE 2.12: LTI *N*-path input impedance (simulation Vs calculus): capacitors

to zero, nevertheless it should be counted in the input impedance calculus, where the LTI model does not include the capacitor voltage "memory-effect".

The input impedance resulting from this current is calculated in the case of N=4 (4-path) in Appendix. A and the input impedance value depends on the value of the harmonic following 4 cases:

Input impedance for k = 4l

$$Z_{\text{in,mem}}k \cdot f_{\text{LO}}) = R_{\text{sw}}$$

(2.8)

**Input impedance for** k = 4l + 1 **or** k = 4l + 3

$$Z_{\text{in,mem}}(k \cdot f_{\text{LO}}) = \frac{k^2 \pi^2}{k^2 \pi^2 - 8} (R_{\text{source}} + R_{\text{sw}}) - R_{\text{source}}$$

(2.9)

Input impedance for k = 4l + 2

$$Z_{\text{in,mem}}(k \cdot f_{\text{LO}}) = \frac{k^2 \pi^2}{k^2 \pi^2 - 16} (R_{\text{source}} + R_{\text{sw}}) - R_{\text{source}}$$

(2.10)

To validate this formula, we replace the values of  $R_{\text{source}}$  and  $R_{\text{sw}}$  by those of the simulated circuit of fig. 2.10 giving:  $Z_{\text{in,mem}}(f_{\text{LO}}) = 321 \,\Omega$ . As

FIGURE 2.13: LTV N-path input impedance

stated before, the capacitor memory-effect impedance calculated in this section is not the total input impedance, it's only the impedance resulting from the voltage held in the baseband capacitor, and not the baseband impedance itself. The total input impedance is therefore the parallel combination of  $Z_{\rm in,mem}$  and the baseband impedance equal to  $\frac{R_p}{4}$ :  $Z_{\rm in}(f_{\rm LO}) = Z_{\rm in,mem}(f_{\rm LO})//\frac{R_p}{4} = 321//2500 = 284\,\Omega$  which is close to the simulated input impedance value  $Z_{\rm in,Sim}(f_{\rm LO}) = 283\,\Omega$ . The same for  $2f_{\rm LO}$ :  $Z_{\rm in}(2f_{\rm LO}) = Z_{\rm in,mem}(2f_{\rm LO})//\frac{R_p}{4} = 67.5//2500 = 65.7\,\Omega$  which is close to the simulated input impedance value  $Z_{\rm in,Sim}(f_{\rm LO}) = 66\,\Omega$ . Finally  $3f_{\rm LO}$ :  $Z_{\rm in}(2f_{\rm LO}) = Z_{\rm in,mem}(2f_{\rm LO})//\frac{R_p}{4} = 27//2500 = 26.7\,\Omega$  which is close to the simulated input impedance value  $Z_{\rm in,Sim}(f_{\rm LO}) = 27\,\Omega$ .

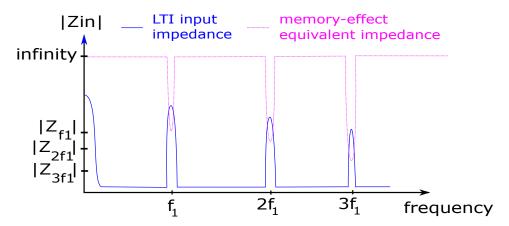

This calculated  $Z_{\text{in,mem}}$  is the impedance resulting from the memory-effect of the capacitor, that is present only at the N-path center frequency and its harmonics. Thus, outside of the center frequency and harmonics, it is the LTI impedance (eq. 2.6) which is valid.

Now that we calculated  $Z_{\rm in}$ , we propose in the next section a solution for the problem of N-path input impedance when used in parallel, i.e. the second N-path presents a shunt in parallel to the first one, at its center frequency as shown in fig. 2.4.

FIGURE 2.14: N-path input impedance, merging LTI and LTV models.

#### 2.3.3 Use of switch resistance ( $R_{sw}$ ) for input impedance tuning

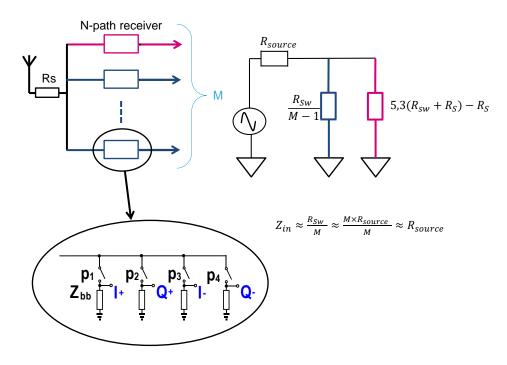

A solution to the parallel N-path presenting a low input resistance ( $R_{\rm sw}$ ), to the receiving one at its center frequency is to use  $R_{\rm sw} = M\,R_{\rm source}$ . Therefor, M parallel N-paths would have an input impedance equal to the source impedance as shown in fig. 2.15.

In the one hand, a large  $R_{\rm sw}$  value means a small switch. In the other hand, for a fixed bandwidth, increasing the resistance reduces the capacitor size, leading to both a low power and low area N-path, exactly as targeted. However, increasing  $R_{\rm sw}$  value increases the NF accordingly (for a fixed bandwidth). This solution is suitable for low power and low area receivers.

In this section, we developed and validated the analytic expression of the input impedance of a N-path receiver. We came up with a novel solution for parallel reception using N-path receivers, counting on increased switch resistance to shape the impedance according to parallel reception constraints. If this solution can be used for ultra low power reception, taking advantage of a full passive scheme, it is limited in term of noise: increasing switch resistance will result in increased NF and make the solution incompatible with most of radio standards. For this reason, it has been decided to explore another trade-off: allow ourselves to use an active block ( $G_m$ ) in our N-path arrangement. This will bring us extra flexibility (but with a consumption and linearity penalty) in the system optimization.

# **2.4** $G_m$ N-path receiver

Full *N*-path receiver appears to be a promising solution for parallel reception, for the low power and high linearity aspects. On the other hand, as demonstrated in previous chapter, this kind of solutions suffers from input

FIGURE 2.15: Solution for *N*-path input impedance :  $R_{sw} = M \cdot R_s$

impedance management constraints, which, in conjunction with parallel reception constraints, become unfeasible when targeting low noise solutions. Adding a transconductor block ( $G_m$ ) at the N-path input will split the problem. N-path will be responsible for filtering and frequency translation, whereas  $G_m$  will define the input impedance and noise.

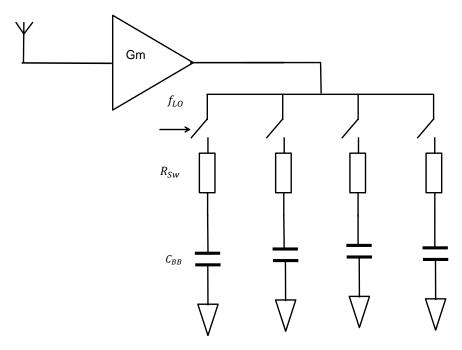

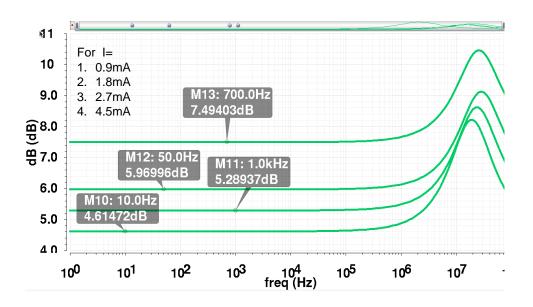

The implemented  $G_m$  block at the input of the N-path is placed as shown in fig. 2.16. It results in a low NF receiver as shown in fig. 2.17, along with avoiding the input impedance problem of parallel N-paths.

#### Need for a harmonic rejection receiver

The basic operation of the *N*-pathreceiver (as any mixer based receiver) is to multiply the input (RF) signal with an LO signal. The LO being a square wave, not only the "useful" RF signal (located at LO frequency) is down converted to baseband, but also any harmonic, corrupting the output signal.

In parallel reception context, it is not possible to have filtering prior to receiver input, obliging the receiver to reject harmonics, as the Harmonic Rejection Mixer (HRM) does.

The principle of Harmonic Rejection Mixer (HRM) is well known [17]. As mixer can only operate with square LO waves (for noise and linearity

FIGURE 2.16:  $G_m$  N-path

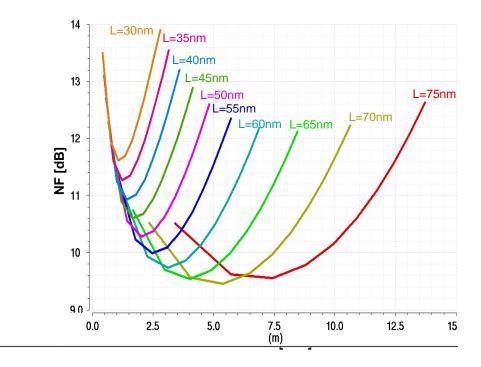

FIGURE 2.17:  $G_m$  N-path NF

FIGURE 2.18: Traditional Harmonic Rejection Mixer (HRM) [17]

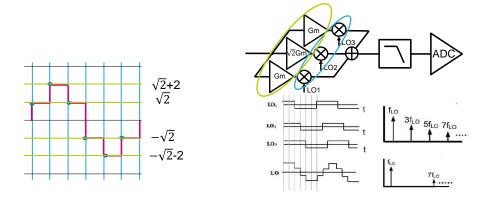

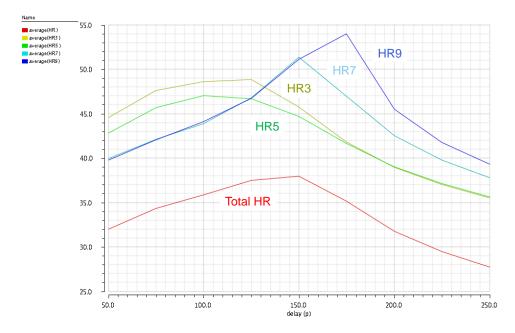

reasons), it is not suitable to multiply input signal with a sine wave to prevent any harmonic mixing. An alternative solution is to mix the input signal with multiple square waves, all with the same frequency, but with different phases and amplitudes so that, when combining all mixers output, fundamental contributions are added and harmonics contributions are canceled. One example is presented in fig. 2.18, where 3 mixers are used with  $\frac{\pi}{3}$  phase shift and 1,  $\sqrt{2}$ , 1 weights [17]. Behavior of HRM can be understood both in frequency and time domain. In frequency domain, one can observe that the Fourier transform of the weighted sum of the 3 LO signals does not contain any  $3^{\rm rd}$  and  $5^{\rm th}$  harmonics. This explains why this HRM does not mix around  $3^{\rm rd}$  and  $5^{\rm th}$  harmonics. In time domain, drawing the weighted sum of the LO signal reveals a signal mimicking a sine wave. This observation really makes sense: the more the LO signal is close to the sine wave, the less harmonics it contains and the better he performs as HRM. This HRM scheme can be extended to the  $G_m$  N-path receiver, adding multiple  $G_m$ -switch path to the same output capacitance as shown in fig. 2.19.

This scheme is nevertheless not fully compliant with the context of parallel reception because it still relies on the availability of a signal at LO frequency. This means that having *M* parallel receivers will require *M* LO frequencies (*M* PLL's) which is not practically feasible for large *M*.

Our proposed solution to get rid of the need of multiple LO frequencies

FIGURE 2.19:  $G_m$  N-path Harmonic Rejection Mixer (HRM)

is to mimic a sine wave at a given frequency by summing square waves, at LO frequency with different amplitudes. In other words, LO signal is digitized with a given sampling frequency. Nyquist criteria tells us that this is possible, as soon as sampling frequency is strictly higher than twice LO frequency.

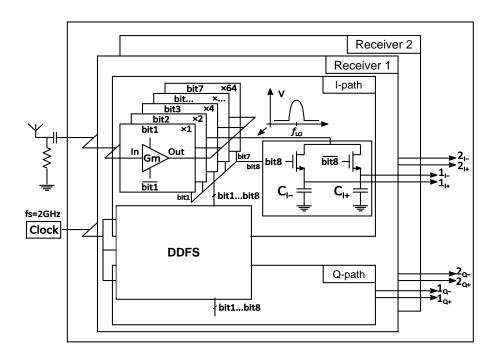

This solution open the way for parallel reception: Parallel receiver can be built with a single PLL, generating sampling frequency, chosen to be slightly higher than the two times maximum frequency to be received. Thus, each receiver will be  $G_m$ -N-path based, including a HRM driven by a Direct Digital Frequency Synthesis (DDFS).

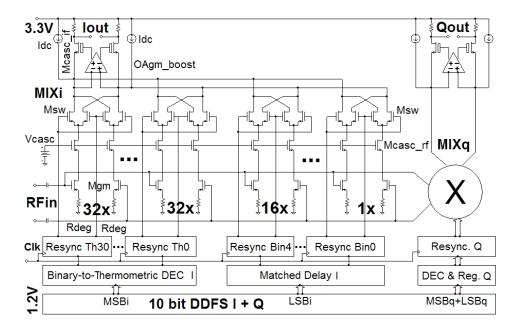

# 2.5 Novel architecture introduction: Mixer-DAC $G_m$ N-path

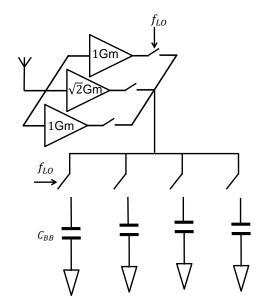

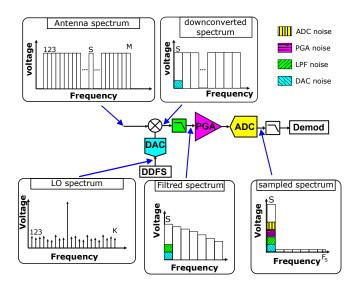

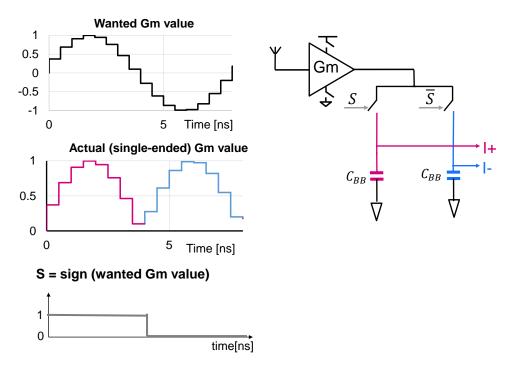

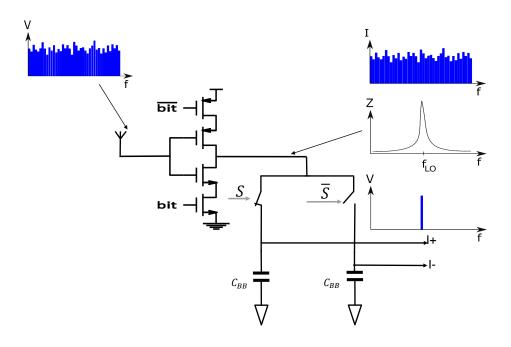

The architecture shown in fig. 2.20 is a practical implementation of the proposed solution.  $G_m$  + switch arrangement has been replaced with a "switchable  $G_m$ " and the bank of  $G_m$ , initially all with the same amplitude, has been replaced with a binary weighted  $G_m$  bank to reduce the complexity. The  $G_m$  value varies over time as walking sampled sine-wave. Thus, the mixing is done in the  $G_m$  by modulating its value. The output current is therefore the multiplication of the RF input voltage and the modulated  $G_m$ ,

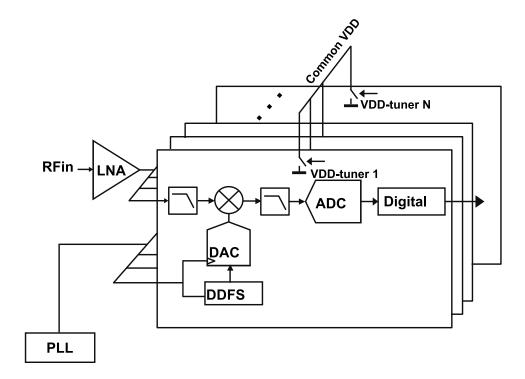

FIGURE 2.20: Harmonic rejection  $G_m$  N-path based mixer-DAC

resulting in a baseband current that will be integrated over the baseband capacitor. The  $G_m$ s are driven by a DDFS. For M parallel tuners, each tuner will include a mixer-DAC along with its DDFS, all driven by a single PLL as shown in fig. 2.21. Moreover when duplicating many  $G_m$ -N-pathreceivers in parallel only the receiving ones would be on, the others could be shunt off, meaning that this architecture power consumption scales with the number of received channels.

This architecture is power scalable and resilient to interference <sup>5</sup>. However, this architecture has to be compared to the FSC to determine in an analytic way, and for a Figure Of Merit (FOM) based comparison, which one of these two architectures is more power efficient for massively parallel reception. Comparison is drawn in chapter 3.

#### 2.6 Conclusion

In this chapter, we introduced the N-path filter and it's correspondent N-path receiver, we listed N-path issues: input impedance and harmonic mixing. Then, we developed an intuitive input impedance calculation, along with solutions to get rid of the input impedance issue, as the  $G_m$ -N-path that is described in section 2.4. in the last section a  $G_m$ -N-path based mixer-DAC

<sup>&</sup>lt;sup>5</sup>Uses one analog clock and as much DDFS as needed tuner

2.6. Conclusion 29

FIGURE 2.21: Mixer-DAC parallel tuners architecture

is proposed to get rid of the harmonic mixing issue. This proposed solution take advantage from the low power and area  $G_m$  N-path receiver as well as the interference robustness of the DDFS driving mixer-DAC architecture. Moreover, this architecture is power scalable, which make it a promising candidate for massively parallel reception. However, this architecture has to be compared to the FSC to determine in an analytic way, and for a FOM based comparison, which one of these two architectures is more power efficient for massively parallel reception. Comparison is drawn in chapter 3.

#### **Chapter 3**

# Massively Parallel Reception: a Power Efficiency Comparison of Mixer-DAC and Full Spectrum Capture

#### 3.1 Introduction

In the last chapter we developed a  $G_m$  N-path based mixer-DAC, that features all the targeted constraints, i.e. robustness to interferences, low power and area per receiver, and a power consumption that scales with the number of received channels (§ 2.5). Nevertheless, this architecture would be duplicated as many times as needed for each parallel tuners, making the total power increase with the number of received channels. This total power consumption could then exceed the FSC power consumption for a high number of received channels (the power consumption of the FSC is fixed and slightly depends on the number of received channels). These two architectures have therefore to be compared analytically to determine the more power efficient one.

In this chapter, we present two main massively parallel receivers architectures: FSC and Mixer-DAC. Then, we compare their power consumption for a given test case. In section 3.2, the two architectures are presented along with each one's advantages and drawbacks. In section 3.3, we present the assumptions on which the comparison was based, and the standard of comparison Data Over Cable Service Interface Specification (DOCSIS) 3.0. This standard was chosen just as a starting point to compare the two architectures, as it represents a realistic test case. The comparison will be widened to more general cases later on. Within this section, we present a detailed study of the noise contribution of each block of the two architectures and the way it is related to that block's power consumption. Then, we explain the way

FIGURE 3.1: Full Spectrum Capture architecture [9].

the total architecture power budget is split between the different blocks, and conclude on the total noise contribution of the two architectures. We finally present the power consumption comparison results based on the noise contributions study, and with respect to DOCSIS 3.0 standard. The comparison outcome targets is to define an "efficiency limit", i.e. a number of channels above which FSC is more power efficient than mixer-DAC. In section 3.4, a comparison of the two architectures with respect to standards other than DOCSIS 3.0 is presented. We choose for that to simply compare the two architectures for sweeps on DOCSIS 3.0 parameters, which is equivalent to comparing them for a wide spectrum of standards. The goal is here again to show how the efficiency limit changes over every swept parameter.

The final conclusion is that the efficiency limit for the first comparison case is 11 channels. For standards other than TV, this limit is expected to be even higher, which makes the choice of mixer-DAC architecture, for these cases, even more beneficial than FSC.

#### 3.2 Presentation of the two compared architectures

#### 3.2.1 Full Spectrum Capture

The FSC shown in fig. 3.1 was introduced in chapter 1 as an ADC-first architecture, where the ADC digitizes the whole spectrum so that the signal processing is entirely done in digital [9]. As mentioned previously, this architecture solves the problem of clean LO-generation by using one clock and DCS blocks: mixing in digital with DDFS helps overcome the harmonic mixing problem (DDFS high number of bits). However, the FSC has a high power consumption that does not scale with the received bandwidth.

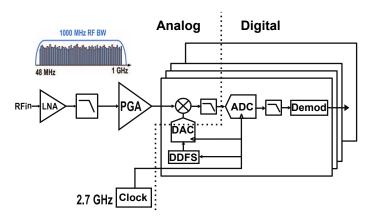

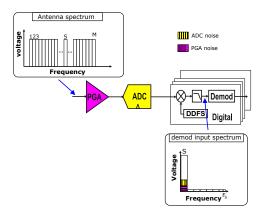

FIGURE 3.2: Mixer-DAC architecture

#### 3.2.2 Mixer-DAC receiver

The mixer-DAC architecture relies on a single central clock that drives one DDFS per channel, as shown in fig. 3.2. For each channel, the DDFS drives a mixer-DAC which downconverts the wanted channel to baseband. The channel is first selected through a LPF and then, digitized by an ADC. This architecture, being based on one central clock and DDFS blocks, allows for a clean LO generation without interference problems. The resolution of the DDFS clock determines the harmonic rejection ratio: the higher the number of bits, the higher the harmonic rejection ratio. This architecture was used in [8] to target a 60 dB dynamic range single TV receiver application, and in [18] as an alternative solution to FSC. This architecture is power scalable and uses low FOM ADCs (bellow 100 MHz  $f_s$ , as shown in fig. 1.4). However, each channel includes a high sampling frequency ( $f_s$ ) mixer-DAC. If duplicated many times, as for the massively parallel reception case, the power consumption of all the mixer-DACs can rise very high and exceed the FSC one. The mixer-DAC power consumption should therefore be compared to the FSC one, for the same input antenna spectrum and the same output SNR constraint.

## 3.3 Full Spectrum Capture and mixer-DAC power efficiency comparison in DOCSIS context

#### 3.3.1 Comparison assumptions

In fig. 3.3, the blocks that will be compared are surrounded by a dashed line. The blocks surrounded by a solid line are those that will not be taken into account in the comparison, as they are used by both architectures, and can

FIGURE 3.3: Comparison of the two architectures: FSC and mixer-DAC.

therefore be suppressed from both architecture for this comparison. The blocks surrounded by a bold line, FSC mixer and decimation blocks, will also be discarded from comparison, but at the advantage of FSC as they run at a very high frequency, which means a big power consumption and noise contribution. The aim of this paper being to prove that the mixer-DAC architecture is more adapted to the massively parallel reception, we can afford advantaging FSC. Moreover, the digital blocks power consumption is directly related to the technology, so that eliminating them avoids having a comparison that is bound to technology and makes it more general. The two architectures will be compared with respect to a custom standard derived from the DOCSIS 3.0 standard that we will call "comparison values". All values are equal to those of DOCSIS 3.0 except the number of channels where we use  $\frac{f_{\text{max}}}{RW}$  = 250, in order to have a dense spectrum, meaning that there is no single frequency band that is unused from 0 to  $f_{\text{max}}$ . Also, the output SNR was changed from the DOCSIS value of 33 dB to 60 dB to consider the uncounted blocks: for example, the first LNA is generally one of the biggest noise contributors in a receiver chain. Both "comparison values" and DOCSIS 3.0 values are depicted in table .3.1. The Peak-to-Average Power Ratio (PAPR) value, given in the table, is for one channel only. For *N* channels, the PAPR<sub>N</sub> Channels =  $10 \log(N) + \text{PAPR}_{\text{Single Channel}}$ .

In the forthcoming comparison, the goal is to sum up the noise contributions of each architecture at a node that is common to both. In our case, we chose the input of the Demod blocks as the reference node, where all noise contributions will be summed up at, and where the output SNR will be calculated.

| parameter                           | DOCSIS 3.0 | Comparison values                        |

|-------------------------------------|------------|------------------------------------------|

| output SNR [dB]                     | 33         | 60                                       |

| PAPR <sub>Single Channel</sub> [dB] | 10         | 10                                       |

| Channel bandwidth (BW)[MHz]         | 5.2        | 5.2                                      |

| $f_{\text{max}}[\text{GHz}]$        | 1.3        | 1.3                                      |

| Number of channels                  | 158        | $\frac{f_{\text{max}}}{\text{BW}} = 250$ |

TABLE 3.1: DOCSIS 3.0 parameters values

To compare the two architectures, the same input spectrum will be considered: M stacked channels with equal amplitudes and with a total power of 1 V. Each channel amplitude is then  $\frac{1}{\sqrt{M}}$  V. We consider, for simplicity sake, that the signal at the comparison reference node has an amplitude of 1 V for both architectures. This way, the signal undergoes, for both architectures, an amplification of gain  $\sqrt{M}$ .

Throughout the comparison, we go by the rule that SNR is preserved along the reception chain, i.e. for any given block. The block output signal and its noise undergo the same amplifications and therefore preserve their ratio. So, whenever it is possible, noise contribution of a given block will be expressed as a function of the output signal of that same block. When it is not the case, as for noise contributions that are independent of the signal, i.e. KT/C noise and Programmable Gain Amplifier (PGA) noise, the noise contribution has to be multiplied by the amplification gain it underwent before reaching the output node. This way, we can sum up all the noise contributions at the comparison reference node.

There are two amplification steps for both architectures:

- Amplification 1: after mixing and low pass filtering, the signal amplitude changes from  $\frac{1}{\sqrt{M}}$  V to 1 V at the reference node, so that  $\sqrt{M}$  gain is needed to get back to the 1 V amplitude at reference node.

- Amplification 2: at ADC input the signal amplitude is equal to  $\frac{1}{\sqrt{PAPR}}$  V which is the maximum value it can have before the ADC (in order to reduce the quantification noise). At reference comparison node, the signal amplitude is directly equal to 1 V, so another  $\sqrt{PAPR}$  gain is needed and will be provided digitally.

For each of the two compared architectures, the power consumption will be derived as a function of the standard parameters, such as output SNR, PAPR...

FIGURE 3.4: Mixer-DAC noise

#### 3.3.2 Mixer-DAC: noise contributions vs power consumption

As mentioned above, for the mixer-DAC architecture, we only consider 4 blocks in this comparison (fig. 3.4). Each of these blocks has its own noise contribution to the output signal and its own power consumption. The mixer-DAC block noise contribution results from mixing the antenna's spectrum channels, other than the wanted channel, with the DDFS signal spurs. These fall down to baseband on top of the wanted channel, then they add up to the low-pass filter and PGA noise contributions, and eventually to the ADC noise contribution where both quantification noise and aliasing noise should be considered.

Given a power consumption budget, in order to achieve the minimum output SNR, this budget has to be split in the optimal way between the four blocks. This is achieved through an optimization loop. Along the loop, we try to establish diagrams of minimum total noise contribution versus power budget, for a set of power budget values. The minimum total noise contribution matches the best power split scenario for a given power budget. This optimization loop is divided into two phases:

- Phase 1: establishing minimum noise contribution versus power consumption diagram for the blocks ADC+LPF.

- Phase 2: establishing minimum noise contribution versus power consumption diagram for the blocks PGA+DAC+ADC+LPF. To do so, we use the diagram established in Phase 1. Phase 2 final diagram is therefore used to interpolate the total power budget for a given output SNR value for the whole chain.

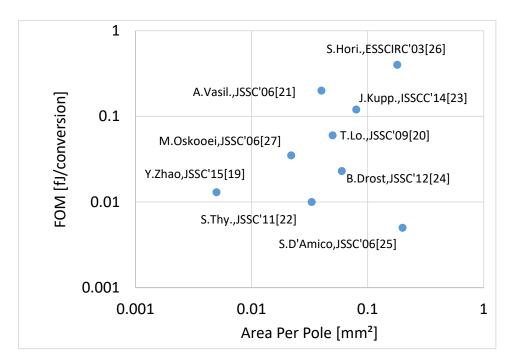

FIGURE 3.5: Low pass filters state of the art.

The final comparison between the two architectures is done by comparing the necessary power budget for a given output SNR constraint. The ADC and LPF cannot be optimized separately as the choice of ADC parameters depends on and influences the LPF parameters choice. Therefore, it is necessary to start with these two blocks in phase 1, while the order of choice for the other two blocks is arbitrary.

#### Phase 1

**Low Pass Filter noise contribution** To calculate the Low Pass Filter (LPF) noise contribution as a function of power consumption, and to keep this study general and not bound to one precise LPF architecture, we use LPF FOM [19]:

$$FOM_{LPF} = \frac{P_{LPF}}{BW \, SFDR \, O^{7/3}} \tag{3.1}$$

where:

$P_{\text{LPF}}$ : LPF power consumption

SFDR: LPF output Spurious Free Dynamic Range (SFDR)

BW: Signal bandwidth

O: LPF order

A LPF FOM survey [19]–[27] is shown in fig. 3.5, the held FOM value for our comparison is  $FOM_{LPF} = 0.01$  fJ/conversion.

**ADC noise contribution** for the ADC noise contribution we also use the ADC FOM (eq. 3.4)

The integrated quantization noise error from 0 to  $\frac{f_s}{2}$  interval can be expressed as a function of the ADC Full-Scale voltage (FS) and the number of bits (N) [28]:

$N_{\left[0, \frac{f_{s}}{2}\right]} = \frac{2^{-N} \text{ FS}}{\sqrt{12}} \tag{3.2}$

Approximating the quantification noise to be a white noise (the same approximation holds for the FSC architecture), the quantification noise over the wanted bandwidth is therefore:

$$N_{\left[0,\frac{\text{BW}}{2}\right]} = \frac{2^{-N} \text{ FS}}{\sqrt{12}} \sqrt{\frac{\frac{\text{BW}}{2}}{\frac{f_s}{2}}}$$

$$= \frac{2^{-N} \text{ FS} \sqrt{\text{BW}}}{\sqrt{12 f_s}}$$

(3.3)

The ADC FOM formula [12] is:

$$FOM_{ADC} = \frac{P_{ADC}}{f_{\text{snyq}} 2^N}$$

(3.4)

where:

$P_{ADC}$ : ADC power consumption  $f_{snyq}$ : ADC Nyquist frequency N: Number of ADC bits

including the last formula in the equation 3.3 gives:

$$N_{\left[0,\frac{\text{BW}}{2}\right]} = \frac{\text{FS FOM}_{\text{ADC}} \sqrt{\text{BW } f_s}}{\sqrt{12} P}$$

(3.5)

The full scale voltage is the sum of the wanted channel and the attenuated unwanted channels, and is equal to:

$$FS = S\sqrt{\text{PAPR}} \cdot \left(\frac{\Delta f}{f_{-3 \text{ dB}}}\right) \tag{3.6}$$

Where:

*S* : One channel amplitude

$\Delta f$ : Equivalent brick-wall filter cutoff frequency

$f_{-3\,\mathrm{dB}}$ : Actual LPF cutoff frequency

This sum depends on the LPF cutoff frequency and order. As mentioned before, the different channels are assumed equal to each other. Then, we calculate the cutoff frequency of the equivalent brick-wall-filter<sup>1</sup> to our LPF as for Equivalent Noise Band-Width (ENBW) of an LPF, we use equation 3.7:

$$\int_0^\infty |H(j\omega)|^2 d\omega = H_{\text{max}}^2 2 \pi \Delta f$$

(3.7)

where:

$H(j\omega)$ : LPF transfer function  $H_{\text{max}}$ : Maximum value of  $H(j\omega)$

Finally, the ADC quantification noise contribution to the comparison reference node can be expressed as follows:

$$N_{\left[0,\frac{\text{BW}}{2}\right]} = \frac{S\sqrt{\text{PAPR}} \cdot \left(\frac{\Delta f}{f_{-3\text{dB}}}\right) \text{FOM}_{\text{ADC}} \sqrt{\text{BW} f_s}}{\sqrt{12} P}$$

(3.8)

The ADC FOM value used for this comparison is not a fixed value. As explained above, for high frequencies, the FOM grows linearly with  $f_s$ . So, for  $f_s < 100$  MHz, a fixed value was used: FOM<sub>ADC</sub>( $f_s$ ) = 1.4 fJ/conversion, and for  $f_s > 100$  MHz, FOM<sub>ADC</sub>( $f_s$ ) = 1.4  $\frac{f_s}{100\,\mathrm{M}}$ . It is the value of FOM<sub>ADC</sub> used in the mixer-DAC architecture. The aliasing noise is given by the following equation:

$$N_{\text{Aliasing}} = S \left( \frac{1}{1 + \left( \frac{f_s}{\text{BW}} \right)^2} \right)^{O/2}$$

(3.9)

**Phase 1 optimization** In order to optimize the total power consumption, a set of total power consumption values was considered, and for every value, the optimal way of splitting this power was found, i.e. we find the ADC number of bits, sampling frequency and LPF order that give the minimum noise contribution for this given total power. Then, we get a list of noise contributions as a function of power consumption of the combination ADC and LPF.

#### Phase 2

At this step of the optimization, like in phase 1, we find the optimum power distribution, but this time we have 3 blocks: PGA, DAC and the last block is the combination of ADC+LPF. For this last block, we use the diagram obtained at phase 1; one more parameter is introduced and optimized at this

<sup>&</sup>lt;sup>1</sup>brick-wall-filter means an ideal filter that would have a transfer function with only two distinct region: a totally pass region and a totally reject region, and nothing in between them. As a transfer function made by brick-wall.

phase: the hold capacitor of the ADC. The reason why this capacitor noise contribution is included with PGA, and not ADC, is explained below.

To determine the PGA noise versus power consumption equation, we use the following equation [29]:

$$SINAD = \frac{P_{\text{signal}}}{P_{\text{noise}} + P_{hn}} = \frac{P_{\text{signal}}}{\frac{KT}{C_{\text{load}}} + \frac{1}{2}(H_n)^2(C_{\text{load}})^2}$$

(3.10)

The Signal-to-Noise And Distortion ratio (SINAD) of a simple MOS follower is a trade-off between noise and distortion depending on  $C_{load}$  value. When  $C_{load}$  goes high, the thermal noise goes high and when it goes low, the distortion power goes high.  $C_{load}$  value depends on the sizing and the technology. However, given that PGA is loading an ADC, i.e. a hold capacitor, the main contributor to the parasitic capacitor at the load node is the ADC's hold capacitor. Considering the only contributor to this node to be the hold capacitor, makes the study unbound to a specific technology.

In order to evaluate SINAD, we use the following equation [29]:

$$P_{h3} = \frac{h_3^2}{2}$$

$$= \frac{1}{2} \left(\frac{\hat{V}}{2}\right)^6 \frac{(2\pi f_{\text{sig}})^6 (C_{\text{load}} + C_{\text{tot,}w} W)^6}{I_D^6} \left(\frac{2V_{GT1}}{64}\right)^2$$

(3.11)

where:

$f_{\rm sig}$  : signal frequency

$P_{h3}$ : harmonic 3 signal power

*h*<sub>3</sub> : harmonic 3 signal amplitude

$\hat{V}$  : output signal swing

*W* : width of the output transistors

$I_D$ : bias current of the output transistor

$V_{GT}$ : overdrive voltage

$C_{\text{tot},w}$ : parasitic capacitance, per width unit

As we only consider the capacitance contribution of  $C_{hold}$  at the load node, the up said equation becomes:

$$P_{h3} = \frac{1}{2} \left(\frac{\hat{V}}{2}\right)^6 \frac{(2\pi f_{\text{sig}})^6 (C_{\text{load}})^6}{I_D^6} \left(\frac{2V_{GT1}}{64}\right)^2$$

(3.12)

This output distortion is calculated at the PGA output node, meaning that the noise in (3.11) will be amplified only by the  $\sqrt{\text{PAPR}}$  gain to be

counted at the comparison reference node, resulting in a noise contribution to the comparison reference node to be:

$$N_{h3} = \sqrt{\frac{\text{PAPR}}{2}} \left( \frac{\hat{V} \pi f_{\text{sig}} C_{\text{load}}}{I_D} \right)^3 \left( \frac{V_{GT1}}{32} \right)$$

(3.13)

Where  $N_{h3}$  is the distortion contribution of the PGA at the comparison reference node.

The KT over C noise is the thermal noise produced by the PGA and the sampling switch or block resistance, that will be integrated over the hold capacitor. Generally, the cutoff frequency of the sample-and-hold RC LPF, is fixed at  $f_s/2$ . The integrated thermal noise, at ADC output, is then given by the equation below

$$N_{\frac{KT}{C},[0,\frac{f_s}{2}]} = \sqrt{\frac{KT}{C}}$$

(3.14)

The *KT* over *C* noise being produced after the PGA in the mixer-DAC architecture, its noise contribution should not be amplified, resulting in a noise contribution for the channel bandwidth and at the comparison reference node as follows:

$$N_{\frac{KT}{C},[0,\frac{BW}{2}]} = \sqrt{\frac{KT \, BW \, PAPR}{C_{\text{hold}} \, f_s}}$$

(3.15)

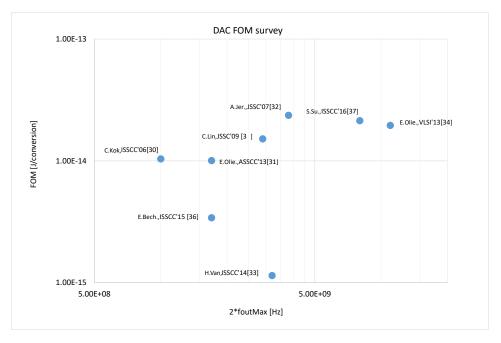

**DAC noise contribution** The DAC noise contribution vs power consumption is defined through a  $FOM_{DAC}$ .

$$FOM_{DAC} = \frac{P_{DAC}}{f_s 2^N}$$

(3.16)

The DAC power consumption is split into a dynamic and a static power, the latter being the DC current sources that charge the load. Given FOM equation, both power consumption types, static and dynamic, are directly proportional to  $f_s$  and to  $2^N$ . While this is obvious for dynamic power consumption and for static power with respect to  $2^N$ , it is less intuitive for the static part to be proportional to the sampling frequency. It can be explained as follows: the DC current is inversely proportional to the settling time of the signal, say:  $I_{DC} = cst/T_{\text{settling}}$ . The signal must be completely settled within half of the DAC clock period, i.e.  $T_{\text{settling}} < 1/(2f_s)$ . This implies:  $I_{DC} > cst \cdot 2f_s$ . Given the fact that we try to optimize power consumption, we choose:  $I_{DC} = cst \cdot 2f_s$ . The static power consumption is therefore directly proportional to sampling frequency. A DAC state of the art

FIGURE 3.6: DAC FOM state of the art.

was assembled and plotted in fig. 3.6 [30]–[37]. The FOM<sub>DAC</sub> state of the art does not resembles the ADC shown in chapter 1: the DAC FOM is flat or at least flat till a high frequency, here 5 GHz, compared to the 100 MHz corner frequency for the ADC FOM. The hold FOM value for our comparison is  $FOM_{DAC} = 3.5 \, fJ/conversion$ .

The considered noise contribution of the DAC is the quantification noise present in the sampled LO signal that DDFS generates. Every spur of this quantification noise mixes with the channel that has the same frequency. The outcome is a baseband noise whose amplitude is equal to the sum of spurs multiplied by one channel amplitude. The sum of the spurs is equal to the integrated quantification noise in equation (3.8), where Full Scale (FS) is considered to be 1, because the sampled signal is the output of the DDFS. We assume that the DDFS driving an RF DAC will obviously reach the full scale. The DAC  $f_s$  is fixed to 2.7 GHz.

The integrated mixer-DAC noise is then:

$$N_{\text{mixer-DAC}} = \frac{S 2^{-N}}{\sqrt{12}} \tag{3.17}$$

When we combine (3.16) and (3.17), the mixer-DAC integrated output noise expression becomes:

$$N_{\text{mixer-DAC}} = \frac{S F O M_{\text{DAC}} f_s}{\sqrt{12} P_{\text{DAC}}}$$

(3.18)

FIGURE 3.7: FSC counted blocks and noise contributions

This is the integrated noise contribution of the mixer-DAC over  $[0, \frac{BW}{2}]$  bandwidth, at the comparison reference node.

Finally, through an optimization loop, we calculate the minimum power consumption for the mixer-DAC architecture, as to be  $P_{\rm mixer-DAC} = 2.9 mW$ . The main power consumer in the chain is the mixer-DAC as expected.

### 3.3.3 Full Spectrum Capture: noise contributions vs power consumption

In fig. 3.7, the counted blocks of the FSC are presented along with their respective noise contributions, i.e. the PGA distortion and the hold capacitor noise contribution, as done for the mixer-DAC PGA. Then, we add the quantification noise of the ADC. Finally, the optimal way of splitting a given power budget is calculated. Note that  $f_s$  of the ADC is fixed for this architecture and is equal to 2.7 GHz. One more parameter is added to this power optimization, as in phase 2 optimization of the mixer-DAC architecture, which is the hold capacitor value.

#### Programmable Gain Amplifier

As for the mixer-DAC architecture, the Programmable Gain Amplifier (PGA) noise contribution at the PGA output is given by equation (3.13). But, for the FSC architecture, the gain is placed after the PGA block, meaning that the noise should be amplified by  $\sqrt{M}$  to be counted at the comparison reference node which results in the equation below:

$$N_{h3} = \sqrt{\frac{M \text{ PAPR}}{2}} \left( \frac{\hat{V} \pi f_{\text{sig}} C_{\text{hold}}}{I_D} \right)^3 \left( \frac{V_{GT1}}{32} \right)$$

(3.19)

The KT over C noise used in (3.15) applies also at the output of the ADC block, in the FSC architecture, except that here it must be amplified by  $\sqrt{M}$  to be counted at the comparison reference node, resulting in the equation below:

$$N_{\frac{KT}{C}, [f - \frac{BW}{2}, f + \frac{BW}{2}]} = \sqrt{\frac{M \text{ PAPR } KT \text{ BW}}{C_{\text{hold}} \frac{f_s}{2}}}$$

(3.20)

#### **ADC** noise contribution

For the FSC architecture, we only consider quantification noise. As the maximum existing channel at antenna input is assumed to be in the  $[0, \frac{f_s}{2}]$  interval, the aliasing noise is supposed to be null. The quantization noise equation is same as (3.2) where FS is now expressed as follows:

$$FS = \sqrt{M \text{ PAPR } S} \tag{3.21}$$

The integrated ADC quantification noise over the wanted channel bandwidth, can thus be expressed depending on signal amplitude as follows:

$$N_{\left[f_w - \frac{\text{BW}}{2}, f_w + \frac{\text{BW}}{2}\right]} = \frac{S\sqrt{MPAPRBW}f_s}FOM_{ADC}}{\sqrt{6}P_{ADC}}$$

(3.22)

The ADC FOM used for the FSC architecture is equal to  $FOM_{\rm ADC}(2.7G) = 1.4 \, \frac{2.7G}{100M} = 37.8 f J/conversion$  which is approximately equal to a 2.7 GHz sampling frequency ADC FOM in fig. 1.4

**Optimization** Finally, through an optimization loop, we calculate the minimum power consumption for the FSC architecture, as to be  $P_{\rm ADC} = 63mW$ . For FSC the main power consumer in the chain is the ADC as expected.

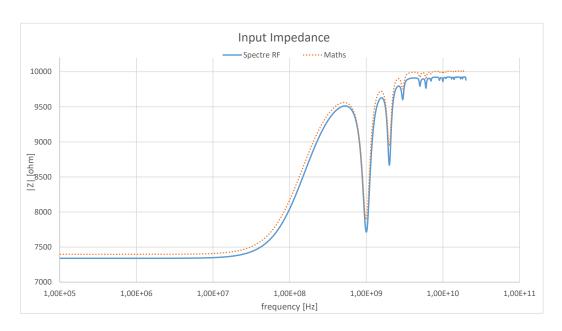

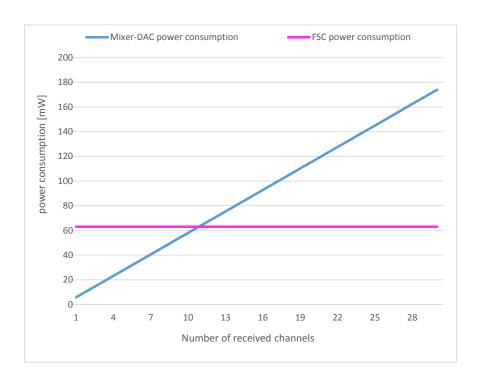

## 3.3.4 Power consumption comparison: introduction of efficiency limit concept

In fig. 3.8, we plot the power consumption of both architectures versus the number of received channels. The mixer-DAC power consumption used to draw the fig. 3.8 is equal to 2 times the one calculated above, because every image rejection receiver should include two duplicates of the mixer-DAC architecture: *I* and *Q* The mixer-DAC power consumption is proportional to the number of received channels, while the FSC has a fixed power consumption: power consumption of the digital part, which is proportional to the received channels number, has been neglected, and the only two

FIGURE 3.8: FSC and mixer-DAC power consumption as a function of number received channels

blocks kept have a power consumption that is independent of the number of channels. Fig. 3.8 shows that the mixer-DAC is less power consuming than the FSC architecture for up to 11 received channels simultaneously. This defines an efficiency limit equal to 11. Moreover the mixer-DAC architecture has a scalable power consumption with the number of received channels, making this solution more adapted to practical use cases, i.e. where the user needs to use 2 or 3 simultaneous channels most of the time, while for short time-slots a higher number of channels could be needed. The FSC is less power consuming than the mixer-DAC only if we receive more than 11 channels 100% of the time, meaning that the mixer-DAC is still more power-efficient than FSC if we receive 54 channels for 10% of the time, and 2 channels simultaneously for the remaining 90% of the time. In general we can conclude that the mixer-DAC is more power efficient than the FSC up to 11 average-simultaneously-used-channels.

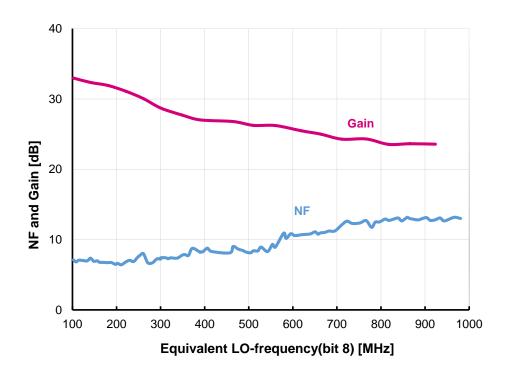

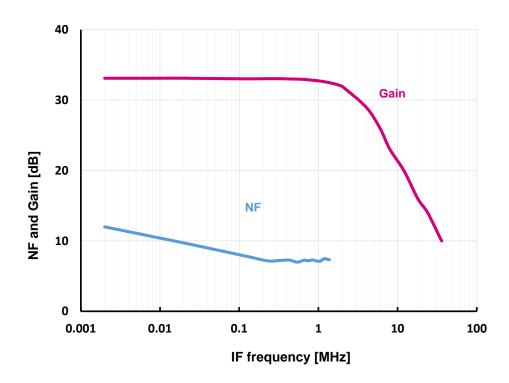

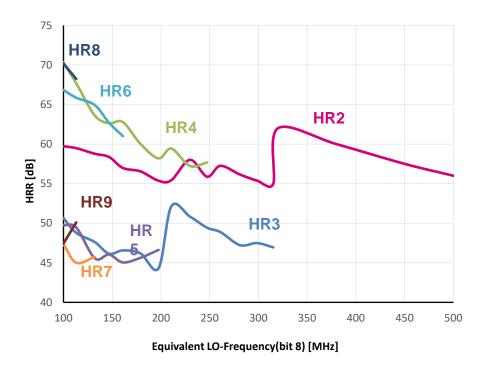

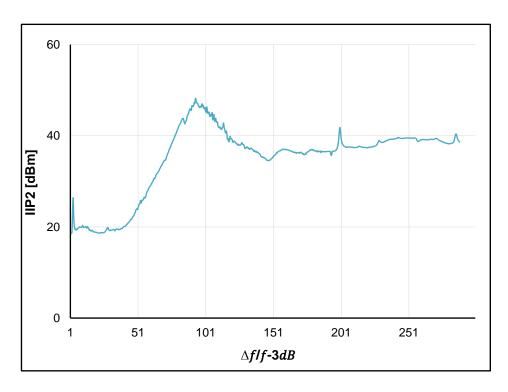

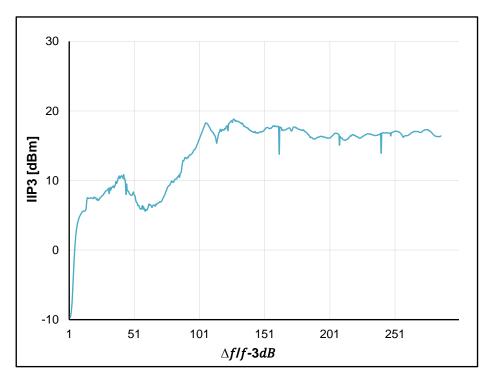

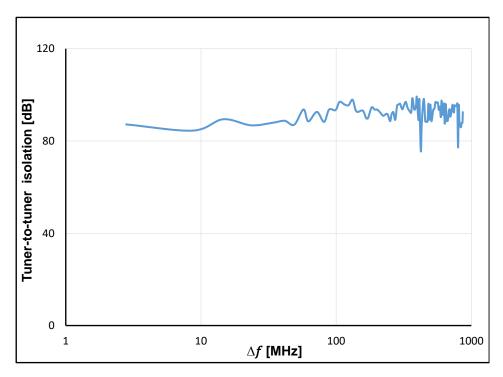

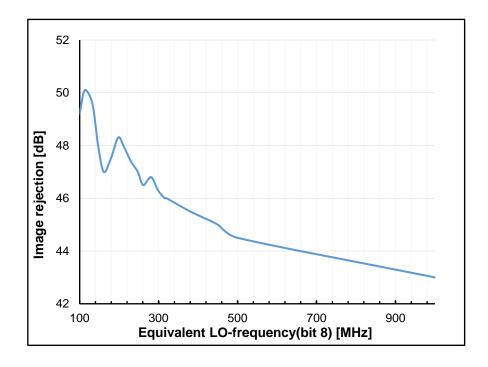

#### 3.4 Comparison for other standards