# Conception de puces multi-fonctions MMIC GaN en bande Ka

Boris Berthelot

## ▶ To cite this version:

Boris Berthelot. Conception de puces multi-fonctions MMIC GaN en bande Ka. Micro et nanotechnologies/Microélectronique. Université Toulouse 3 Paul Sabatier, 2019. Français. NNT: . tel-02494037v1

# $HAL\ Id:\ tel-02494037$ https://laas.hal.science/tel-02494037v1

Submitted on 28 Feb 2020 (v1), last revised 22 Oct 2020 (v2)

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# **THÈSE**

## En vue de l'obtention du

# DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE

Délivré par :

Université Toulouse 3 Paul Sabatier (UT3 Paul Sabatier)

Cotutelle internationale avec l'Université de Sherbrooke, Québec

# Présentée et soutenue par : BERTHELOT Boris

le lundi 25 novembre 2019

Titre:

Conception de puces multi-fonctions MMIC GaN en bande Ka

## École doctorale et discipline ou spécialité:

ED GEET : Électromagnétisme et Systèmes Haute Fréquence

Unité de recherche:

LAAS-CNRS (UMR)

Directeur/trice(s) de Thèse:

TARTARIN Jean Guy et VIALLON Christophe MAHER Hassan et BOONE François

#### Jury:

Jean Guy Tartarin/ Hassan Maher: Directeurs de thèse Christophe Viallon/ François Boone: Co-directeurs de thèse Nathalie Deltimple/ Christophe Gaquière: Rapporteurs Dominique Langrez: Examinateur Thierry Parra: Examinateur Oana Lazar: Examinateur

Dominique Drouin: Invité Rémy Leblanc: Invité

# Remerciements

Cette thèse CIFRE en cotutelle a été effectuée entre différents sites en France, dans l'entreprise OMMIC initiatrice du projet, au Laboratoire d'Analyse et d'Architecture des Systèmes du Centre National de la Recherche Scientifique (LAAS-CNRS) de Toulouse, dans le groupe Microondes Optomicroondes pour Systèmes de Télécommunications (MOST). Une partie de ces travaux a été réalisée au Québec, Canada, à l'Institut Interdisciplinaire d'Innovation Technologique (3IT) à Sherbrooke, au sein du groupe Microélectronique III-V. Je remercie M. Liviu Nicu, Directeur du LAAS-CNRS, M. Eric Tournier, Maître de Conférences, au LAAS-CNRS responsable du groupe MOST de m'avoir accueilli dans l'équipe. Je tiens aussi à remercier M. Richard Arès Directeur du 3IT et M. Hassan Maher, Professeur à l'Université de Sherbrooke, responsable du groupe Microélectronique III-V de m'avoir accueilli dans son équipe.

Mes sincères remerciements vont à Mme Nathalie Deltimple, maitre de conférences à l'université de Bordeaux, et M. Christophe Gaquière, Professeur à l'université de Lille, pour avoir évalué ce travail en la qualité de rapporteur, ainsi qu'à Mme Oana Lazar, ingénieur TAS, M. Dominique Langrez, ingénieur TAS, M. Thierry Parra, professeur à l'université de Toulouse, Mr Dominique Drouin, Professeur à l'Université de Sherbrooke et M. Rémy Leblanc, ingénieur OMMIC pour avoir accepté de prendre part à ce jury en tant qu'examinateurs.

Mes plus profonds remerciements à Jean-Guy Tartarin, Directeur de thèse et Professeur à l'Université Paul Sabatier de Toulouse III, qui m'a fait confiance avant, durant et après les travaux de thèse. Son soutien m'a permis de m'améliorer dans bien des domaines qu'ils soient scientifiques ou plus personnelles. Je ne vais pas m'étendre par écrit et préfère partager cette sympathie de vive voix.

Merci à Christophe Viallon, co-directeur de thèse pour son aide de tous les instants.

J'adresse mes remerciements à M. Hassan Maher, Directeur de thèse et Professeur à l'Université de Sherbrooke, et M. François Boone, Co-directeur de thèse, pour leur confiance et soutien.

Merci à toutes les personnes que j'ai pu rencontrer durant ces années de thèse que ce soit à Limeil Brévannes, Sherbrooke ou Toulouse.

Merci à Alexandre Rumeau pour sa disponibilité et son soutien technique. Merci à Samuel Charlot et Bernard Franc pour leur disponibilité.

Et enfin un merci à Audrey ma fidèle collègue de bureau et au bro Napoléon.

# Introduction

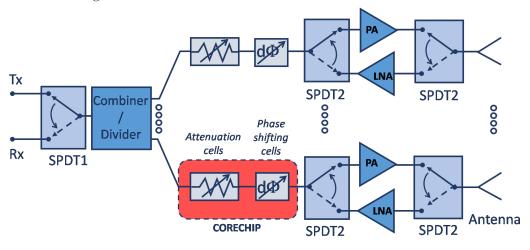

Les antennes réseaux à commande en phase (ARCP) ont traditionnellement été utilisées dans le domaine des radars. Pour ce type d'application les bandes passantes nécessaires étaient relativement étroites. Plus récemment cette contrainte a changé puisque les ARCP se sont généralisées pour des applications plus large bande exploitées dans les réseaux de télécommunications. Des techniques telles que le beamforming (conformation de faisceau) ont été déployées dans le but d'améliorer l'efficacité de la transmission des données. Cette dernière s'appuie sur des ARCP pour conformer les faisceaux plus efficacement dans une direction donnée, augmentant ainsi la qualité des bilans de liaison. Une architecture classique d'ARCP est illustrée en Figure 1. La chaîne comporte différents éléments qui se classent en deux catégories.

Figure 1 – Schéma d'une architecture d'émission réception de type ARCP

La partie front-end, qui est constituée de tout ce qui traite de l'amplification (puissance en émission, et faible bruit en réception) et la partie back-end où le traitement du signal est réalisé. Cette dernière partie regroupe les fonctionnalités dites de contrôle (atténuation et déphasage) et est entourée en rouge sur la Figure 1. L'architecture présentée peut être utilisée à la fois en émission et en réception, l'orientation du signal vers l'une ou l'autre de ces options est garantie par des commutateurs ici notés SPDT pour Single Pole Double Throw ou «Commutateur une entrée deux sorties» en français. A faibles niveaux de puissances et selon la technologie utilisée, des limiteurs et circulateurs peuvent remplacer ces commutateurs.

La partie centrale du travail exposé dans ce manuscrit réside dans l'étude des fonctions de contrôle,

vi INTRODUCTION

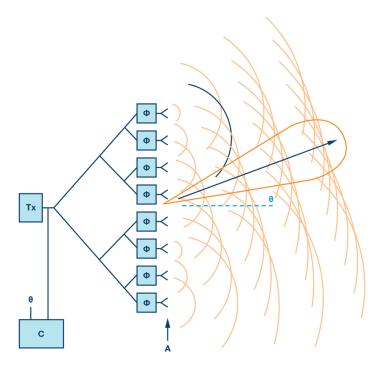

c'est-à-dire les puces MMIC regroupant ces fonctionnalités, et plus spécifiquement leur intégration en technologie GaN selon la filière développée par la société OMMIC. Ces fonctions sont souvent nommées core-chips, elles permettent un contrôle numérique de la phase et de l'atténuation des signaux transitant par ce module (il existe des versions avec un contrôle analogique des phases et atténuations). En contrôlant les paramètres de phase et d'atténuation selon une loi de commande prédéfinie sur chaque branche du système et en espaçant les différentes antennes d'une distance donnée (typiquement la demi-longueur d'onde quand l'intégration le permet), il est possible de former ou de recombiner les signaux traités par chaque antenne. De plus, le contrôle électronique individuel des antennes autorise des balayages focalisés (faisceau directif) ou larges. La Figure 2 illustre le fonctionnement d'un tel réseau avec la recombinaison des ondes en un front uniforme.

Pour implémenter le beamforming des éléments déphaseurs et atténuateurs sont nécessaires. Ces différents éléments peuvent être réalisés tout aussi bien grâce à des circuits actifs que des circuits passifs et être à commande analogique ou numérique. La première permet une couverture angulaire et modulaire continue et globale définie par la tension de polarisation. Cette dernière permet aussi de corriger des erreurs dues aux dégradations de performances liées au vieillissement ou bien à des dérives relatives à la dispersion technologique lors de la fabrication. Cependant ces avantages se font au détriment d'une consommation statique importante et d'une sensibilité aux fluctuations ou dérives de la tension d'alimentation. Pour des applications satellites, le contrôle de la tension d'alimentation est rendu plus critique car les signaux de contrôle sont principalement numériques. La conversion de ces derniers en signaux analogiques nécessite donc l'implémentation de convertisseurs numérique/analogique qui pénalisent l'optimisation de l'espace occupé.

Une solution alternative consiste en l'utilisation de circuits passifs sous forme de cellules mises en cascade réalisant chacune des pas d'atténuation et de phase discrets. On parle alors de fonctions de contrôle numériques. Cette solution s'affranchit des problèmes dus aux tensions d'alimentation du fait du fonctionnement en commutation des transistors. Cette stabilité fonctionnelle est garantie au prix de pertes d'insertion plus élevées, caractéristiques inhérentes à l'utilisation de circuits passifs. Dans ce manuscrit, nous étudierons principalement les *core-chips* passifs même si les performances de certains actifs seront présentées à titre de comparaison. Il faut tout de même préciser que les puces «passives» présentées et issues de littérature présentent une certaine consommation. Ceci est dû au fait que les auteurs considèrent alors la consommation globale du module TxRx, et pas celle du *core-chips* à proprement parler.

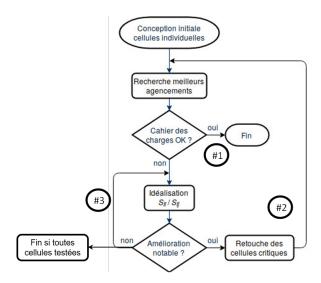

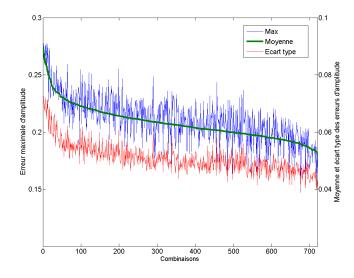

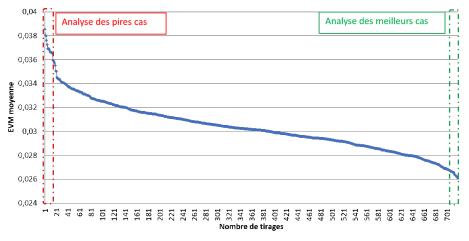

L'intégration des cellules de phase et d'atténuation dans un core-chip complet nécessite un soin particulier. En effet, les cellules n'étant pas parfaites (erreur de phase/amplitude [1] et/ou désadaptions d'impédances [2]), les performances du système finales peuvent être dégradées. Des solutions algorithmiques pour identifier les agencements aux performances les plus favorables ont déjà été mis au point [3] mais celles-ci ne vont pas plus loin que l'obtention de l'ordre optimal. Identifier les cas les plus favorables, les cellules critiques et les potentielles retouches de cellules permettrait donc de gagner un temps précieux de conception et de repousser les performances des core-chips.

Ce manuscrit est séparé en 4 chapitres. Le premier dresse un état de l'art de la littérature concernant les core-chip allant des technologies aux topologies utilisées. Puis il présente notre méthodologie de conception de core-chips GaN en bande Ka. Le second chapitre présente les simulations des cellules de déphasage et d'atténuation que nous utiliserons pour réaliser les core-chips en mode single-ended ou différentiel. Le troisième chapitre traite de la problématique de la mise en commun des cellules et nous présentons notre algorithme d'ordonnancement des cellules qui nous permet d'identifier les agencements de cellules les plus favorables ou défavorables. A cela nous ajoutons l'évaluation de l'impact d'amélioration des cellules dans l'optique d'une ou de plusieurs retouches. Enfin nous terminons dans le chapitre 4 par les mesures des circuits réalisés, 5 au total. Nous avons réalisé 2 circuits single-ended

BIBLIOGRAPHIE vii

FIGURE 2 – Schéma explicatif de la recombinaison des ondes dans un ARCP, avec C le bloc de contrôle et  $\theta$  l'angle visé et 3 circuits différentiels.

# Bibliographie

- [1] Matthew A. Morton, Jonathan P. Comeau, John D. Cressler, Mark Mitchell, and John Papapolymerou. Sources of Phase Error and Design Considerations for Silicon-Based Monolithic High-Pass/Low-Pass Microwave Phase Shifters. *IEEE Transactions on Microwave Theory and Techniques*, 54(12):4032–4040, dec 2006.

- [2] Inder J. Bahl. Control Components Using Si, GaAs, and GaN Technologies. Artech House, 2014.

- [3] Andrea Bentini, Mauro Ferrari, Walter Ciccognani, and Ernesto Limiti. A novel approach to minimize RMS errors in multifunctional chips. *International Journal of RF and Microwave Computer-Aided Engineering*, 22(3):387–393, may 2012.

# Table des matières

| R        | emer         | rciements                                                 | iii          |

|----------|--------------|-----------------------------------------------------------|--------------|

| In       | trod         | luction                                                   | $\mathbf{v}$ |

|          | Bib          | liographie                                                | vii          |

| 1        | Les          | puces multi-fonctions                                     | 1            |

|          | 1            |                                                           | 1            |

|          | 2            | La place du GaN dans les chaînes d'émission-réception     | 2            |

|          | 3            | Composition et critères d'évaluation des ARCP             | 3            |

|          | 4            | Les déphaseurs                                            | 4            |

|          | -            | 4.1 Les déphaseurs analogiques                            |              |

|          |              | 4.2 Les déphaseurs numériques                             |              |

|          | 5            | Les atténuateurs                                          |              |

|          | 6            | Les core-chips                                            |              |

|          | 7            | La place du GaN dans les puces multifonctions             |              |

|          | 8            | Méthodologie de conception                                |              |

|          | 9            | Modes de fonctionnement                                   |              |

|          |              | liographie                                                |              |

|          | <b>D</b> 10. | nograpmo                                                  |              |

| <b>2</b> | Coı          | nception des cellules de déphasage et d'atténuation       | 31           |

|          | 1            | La société OMMIC                                          | 31           |

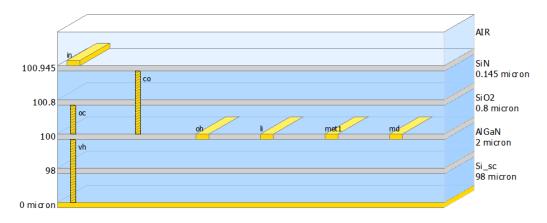

|          | 2            | Présentation du kit de conception de la filière GaN D01GH | 32           |

|          |              | 2.1 Les éléments passifs                                  |              |

|          | 3            | Description simulation EM                                 | 34           |

|          | 4            | Cahier des charges                                        |              |

|          |              | 4.1 Approche large bande                                  |              |

|          |              | 4.2 Approche mono-fréquence                               |              |

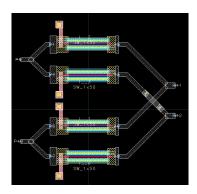

|          | 5            | Réalisation cellules individuelles single ended           |              |

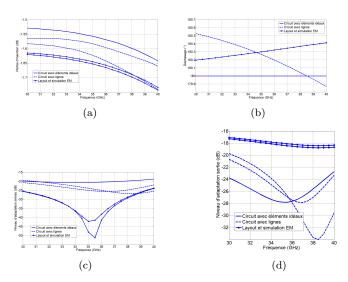

|          |              | 5.1 Cellule 11,25° single ended                           |              |

|          |              | 5.2 Résultats pour toutes les cellules single-ended       |              |

|          | 6            | Conception des cellules différentielles                   |              |

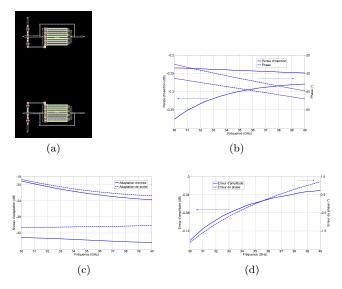

|          | Ü            | 6.1 Cellule 180° différentielle                           |              |

|          |              | 6.2 Résultats pour toutes les cellules différentielles    |              |

|          | Bib          | liographie                                                |              |

|          |              | O                                                         | -            |

| <b>3</b>                  | Mis    | en commun et optimisation de l'ordre des cellules      | <b>59</b> |

|---------------------------|--------|--------------------------------------------------------|-----------|

|                           | 1      | Choix de l'ordre des cellules                          | 59        |

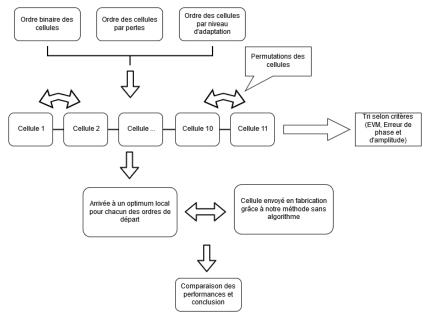

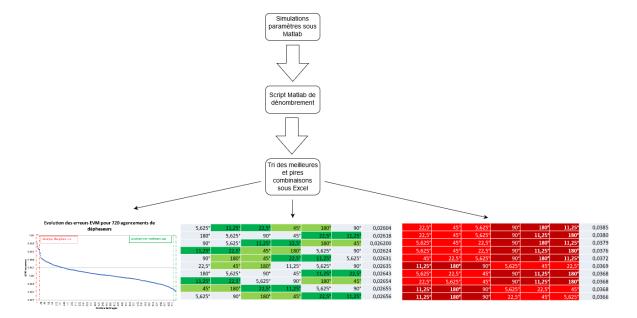

|                           | 2      | Méthodologie de mise en commun des cellules développée | 62        |

|                           |        | 2.1 Méthodologie sans algorithme                       | 63        |

|                           |        | 2.2 Méthodologie avec algorithme                       | 64        |

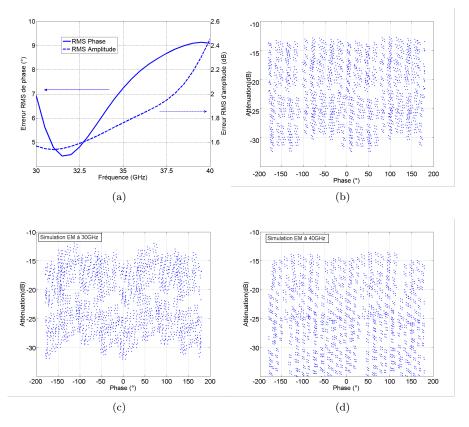

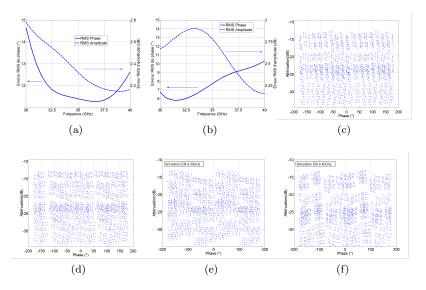

|                           | 3      | Application pour les cellules single ended             | 65        |

|                           |        | 3.1 Sans utilisation de l'algorithme                   | 65        |

|                           |        | En utilisant l'algorithme                              |           |

|                           |        | 3.3 Optimisation des cellules                          |           |

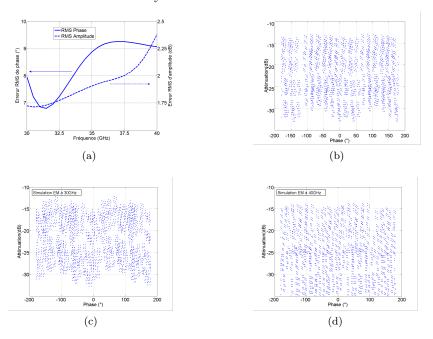

|                           | 4      | Application pour les cellules différentielles          | 90        |

|                           |        | 4.1 Sans utilisation de l'algorithme                   |           |

|                           |        | 4.2 En utilisant l'algorithme                          |           |

|                           | Bib    | ographie                                               | 99        |

|                           |        |                                                        |           |

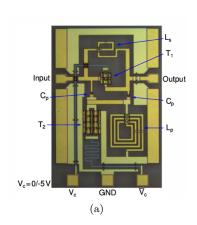

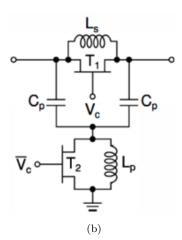

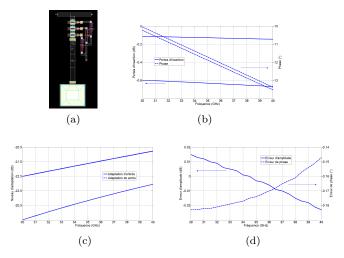

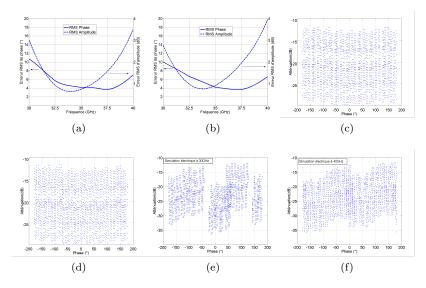

| 4                         | Me     |                                                        | 01        |

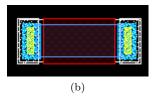

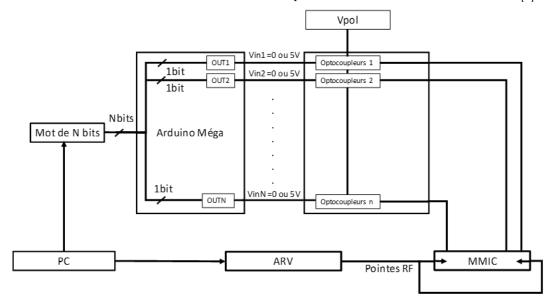

|                           | 1      | Environnement de mesures                               | 01        |

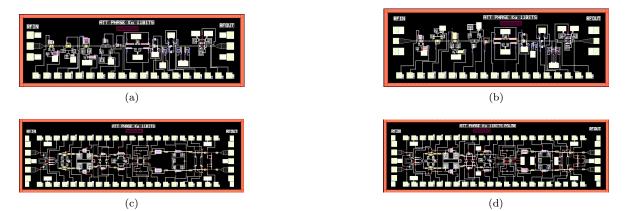

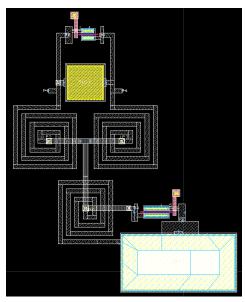

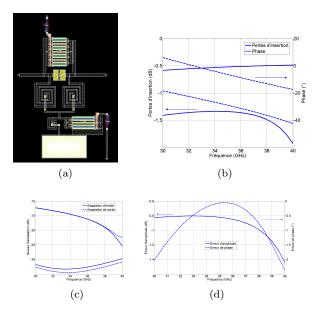

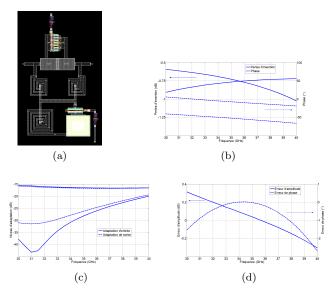

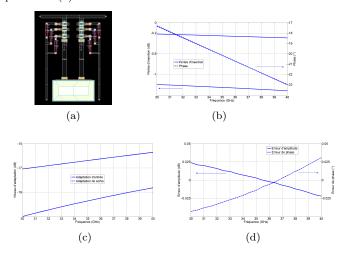

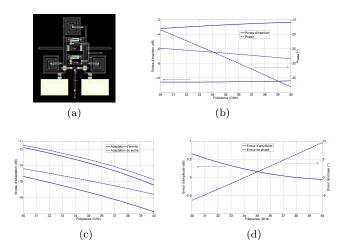

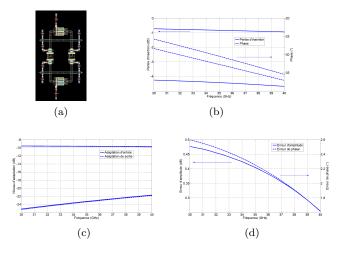

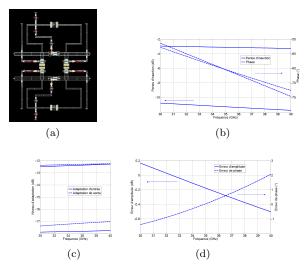

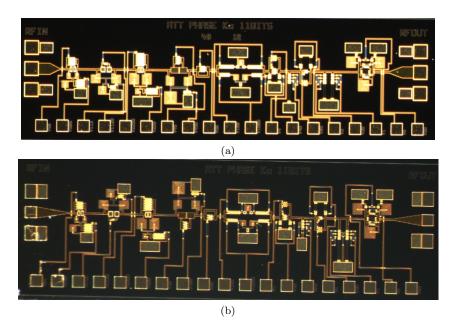

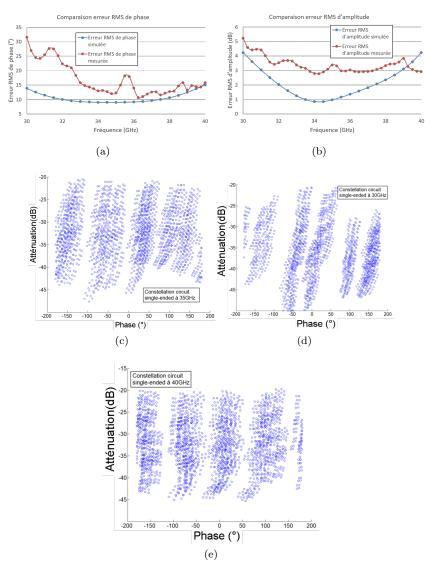

|                           | 2      | Circuits single-ended                                  | 04        |

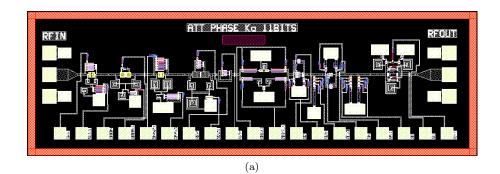

|                           |        | 2.1 Première version                                   | 05        |

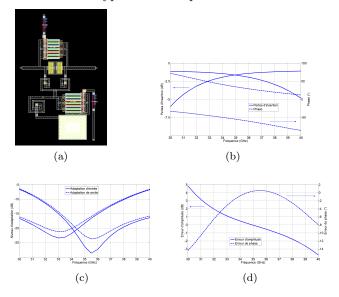

|                           |        | 2.2 Deuxième version                                   | 05        |

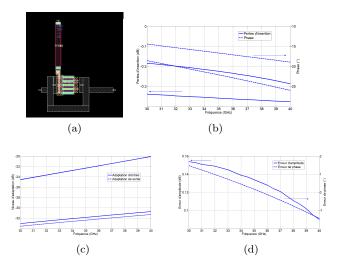

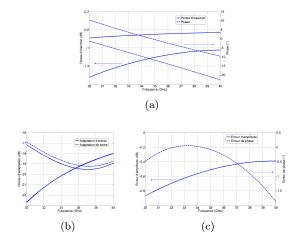

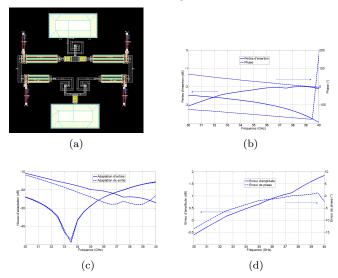

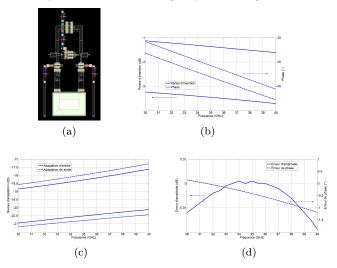

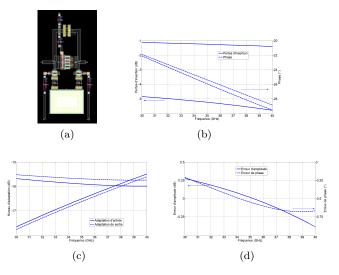

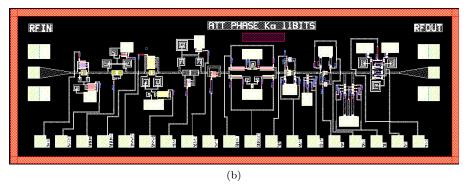

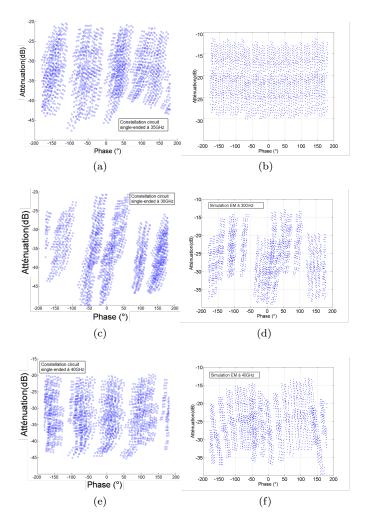

|                           | 3      | Circuits différentiels                                 | 09        |

|                           |        | 3.1 Première version                                   | 10        |

|                           |        | 3.2 Deuxième version et troisième version              | 15        |

|                           | Bib    | ographie                                               | 18        |

| C                         | onclı  | sion générale 1                                        | 19        |

| $\mathbf{R}$              | ésun   | $_{1}$                                                 | 21        |

| $\mathbf{L}_{\mathbf{i}}$ | iste d | es publications 1                                      | 23        |

# Chapitre 1

# Les puces multi-fonctions

## 1 Les technologies utilisées

La tendance allant toujours vers la miniaturisation des systèmes et vers une réduction des prix des modules électroniques RF, les concepteurs se retrouvent face à de nouvelles contraintes de conception. En effet il faut trouver des technologies et/ou des topologies répondant à la fois aux besoins qui s'expriment en termes de performances (efficacité, compacité, linéarité...) mais aussi en termes de coût pour certaines applications grand public. La technologie Silicium Germanium (SiGe) offre de grandes possibilités en termes de fonctionnalités (forte densité d'intégration par l'utilisation de technologies mixtes BiCMOS, maîtrise des erreurs de phase et d'amplitude) tout en gardant un coût bien inférieur aux technologies III-V (Arséniure et Nitrure de Gallium). Cependant, ses propriétés physiques l'empêchent de fournir des amplificateurs d'une efficacité suffisante pour la fabrication de module d'émission réception «tout SiGe». Ainsi il est nécessaire de panacher les technologies, en utilisant par exemple des core-chips SiGe associés à des modules de gestion de la puissance en GaAs ou plus récemment en GaN [1]. Ce point limite l'efficacité d'intégration initialement visée par la technologie BiCMOS. Pour des applications où le coût n'est pas un facteur limitant ferme (spatial et militaire), la technologie GaAs conserve quelques parts de marché. De par ses propriétés physiques, elle permet de réaliser à la fois les fonctions de contrôle mais aussi la gestion de puissance. Le Tableau. 1.1 recense les principales propriétés physiques des technologies majeures utilisées dans notre domaine d'étude (SiGe at GaAs).

| Technologie                                                | SiGe | GaAs | GaN  |

|------------------------------------------------------------|------|------|------|

| Bande interdite (eV)                                       | 1    | 1.4  | 3.4  |

| Mobilité des électrons $(cm^2/V.s)$                        | 2800 | 8500 | 2000 |

| Vitesse de saturation des électrons (10 <sup>7</sup> cm/s) | 2.2  | 2    | 2.5  |

| Champ de claquage $(10^6 V/cm)$                            | 0.25 | 0.4  | >5   |

| Conductivité thermique $(W.cm^{-1}.K^{-1})$                | 1.1  | 0.5  | 1.3  |

Table 1.1 – Propriétés physiques du SiGe, GaAs et GaN [2], [3]

A ce tableau est rajoutée la technologie GaN qui, à l'heure de l'initiation de nos travaux, n'était pas encore exploitée pour réaliser de telles fonction. Le GaN fait état de multiples avantages relativement aux autres technologies, en termes de bande interdite et de champ de claquage (associés à une meilleure dissipation thermique), en plus de son aptitude à fonctionner à hautes fréquences (mobilité et vitesse de saturation électroniques). La large bande interdite rend le matériau plus robuste à des perturbations

électromagnétiques externes. Le champ de claquage important implique directement des tensions et courants relatives aux ondes RF admissibles importantes, ce qui permet l'obtention de niveaux de puissance en sortie bien supérieures à ceeux obtenus par les technologies concurrentes SiGe et GaAs. La conductivité thermique élevée assure une bonne évacuation de la chaleur générée par le fonctionnement du composant, permettant ainsi une intégration plus dense que pour le GaAs.

## 2 La place du GaN dans les chaînes d'émission-réception

Dans ses travaux de thèse, Tyler Ross [4] met en évidence les intérêts d'une chaîne d'émission/réception exploitant pleinement la technologie GaN, par rapport à l'architecture conventionnelle induite par l'utilisation de technologies à faible bande interdite. Comme illustré en Figure 1.1a où les différences d'organisation de la chaîne selon la technologie utilisée apparaissent en bleu sur la Figure 1.1b, il est possible de ré-optimiser la chaîne d'émission et de réception.

FIGURE 1.1 – Différences d'agencement pour une chaîne Tx/Rx en technologie (a) non GaN (b) GaN [2]

En premier lieu, il est possible de mettre les déphaseurs au plus proche de l'antenne en raison de la meilleure tenue en puissance du GaN et de supprimer les limiteurs traditionnellement placés avant les amplificateurs faible bruit (LNA). Avec cette nouvelle disposition, le nombre de déphaseurs utilisés et donc les pertes induites sont grandement diminuées grâce à la réduction du nombre d'éléments sur la chaîne. La réduction des pertes améliore ainsi le facteur de bruit de la chaîne de réception et améliore l'efficacité de la chaîne de transmission. De plus, la capacité des systèmes passifs GaN à travailler avec des signaux à moyenne puissance, simplifie l'implémentation des amplificateurs de puissance (PA). En effet la contrainte sur le gain de ces derniers sera moins importante grâce au niveau de puissance d'entrée déjà élevé ce qui peut leur évite de travailler à des forts niveaux de compression.

Deuxièmement, OMMIC fabriquant déjà des T/R chips (composants regroupant la partie gestion de la puissance, amplificateur de puissance et amplificateur faible bruit) en GaN, nous comprenons bien l'intérêt de réaliser la partie fonction de contrôle dans cette même technologie. D'une part cela permettrait une intégration monolithique comprenant toute la chaine de réception sur une même puce. Et d'autre part, en utilisant les technologies classiques de core-chips SiGe, des incompatibilités de puissances apparaissent aux interfaces des éléments SiGe et GaN. Ces imcompatibilités menant à l'ajout d'éléments limiteurs après les LNA et des pré-amplificateurs avant les PA, ces éléments dégradant la compacité du système.

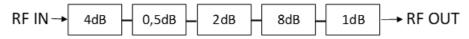

Un des objectifs initiaux de la thèse envisageait l'intégration de blocs amplificateurs de compensation des pertes au sein de la partie fonction de contrôle du *core-chip* de façon à obtenir une dynamique de 6 bits de phase (5,625° de résolution), 5 bits d'atténuation (0,5dB de résolution) et une puissance de sortie de 10dBm. Dans la continuation de cet objectif, une intégration monolithique complète de la puce d'émission réception pourrait être envisagée. En effet, les éléments d'amplification en SiGe étant bien moins performants que les technologies III-V en terme de puissance, la majorité des puces actuelles

regroupent 2 technologies (SiGe-GaAs [5] ou SiGe-GaN [1]) dont la connectique est assurée par des transitions alumines encombrantes, et de fait peu compatibles avec une intégration maîtrisée telle que le nécessite l'exploitation de la bande Ka (du fait de la faible longueur d'onde qui contraint la dimension d'antenne, qui elle-même définit l'encombrement du module  $\mathrm{Tx/Rx}$ ). Ces dernières topologies de puces présentent donc deux inconvénients majeurs qui concernent la place occupée et les pertes associées [6]. Prouver la faisabilité d'une puce  $\mathrm{Tx/Rx}$  « tout  $\mathrm{GaN}$  » présentant des tailles concurrentielles, permettrait de s'affranchir de ces transitions qui dégradent les performances finales.

Après avoir dressé le contexte d'utilisation des modules *core-chips*, et plus spécifiquement leur réalisation en technologie MMIC GaN, nous allons maintenant nous intéresser plus précisément aux éléments qui les constituent. Ensuite nous présenterons les paramètres sur lesquels les performances des fonctions de contrôle sont évaluées et nous étudierons les différentes topologies de déphaseurs et d'atténuateurs puis nous conclurons par un comparatif des performances à l'état de l'art en bande Ka des atténuateurs et déphaseurs, mais aussi des *core-chips*.

## 3 Composition et critères d'évaluation des ARCP

Pour évaluer les performances des éléments constituant les core-chips, les caractéristiques suivantes sont étudiées :

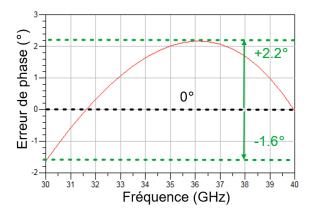

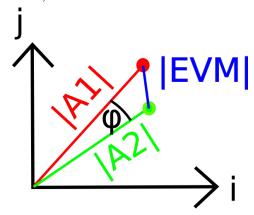

-l'erreur de phase : c'est un élément primordial inhérent à la maîtrise de la fonction même de déphasage. Elle traduit la différence entre la phase désirée et la phase obtenue. Pour des déphaseurs multi-états, cette erreur correspond à l'écart relatif entre la phase de référence mesurée ou simulée et la phase mesurée ou simulée à l'état étudié (auquel on vient enlever la phase de consigne théorique pour obtenir l'erreur relative). Cette erreur peut s'exprimer en erreur absolue en degrés mais elle est généralement exprimée par l'erreur quadratique moyenne (RMS error) en degré l'expression générale d'une erreur RMS est donnée en Equation 1.1 . Ce type d'erreur est généralement employé puisqu'il permet de quantifier une erreur relative à de multiples états de phase. La notion de moyenne dans ce calcul d'erreur implique une mauvaise description d'éventuels états réfractaires qui seraient très éloignés de leur consigne. Cette erreur correspond aussi à la différence de phase entre les deux états des atténuateurs, qui devra elle aussi être minimisée.

$$RMS = \sqrt{\sigma_x^2 + \bar{x}^2} \tag{1.1}$$

Avec  $\sigma_x$  l'écart type de l'erreur et  $\bar{x}$  la moyenne des erreurs.

-l'erreur d'atténuation : elle traduit la différence (ou le rapport) d'amplitude (en dB ou en valeur naturelle) entre les deux états de fonctionnement de chaque cellule. Elle peut également être engendrée par la fonction de déphasage, à l'instar de l'erreur de phase potentiellement générée par la fonction atténuateur. Selon le déphaseur étudié, elle sera calculée selon différents indicateurs. Pour les déphaseurs analogiques, elle correspond à l'atténuation/gain associé au changement de tension de polarisation. Pour les déphaseurs numériques, elle va correspondre à la différence de pertes d'insertion entre les deux états du déphaseur. C'est bien souvent ce paramètre qui vient complexifier le dessin du déphaseur puisqu'une erreur d'atténuation faible implique de garder des pertes d'insertion quasiment égales suivant les deux états commutés tout en garantissant une différence de phase contrôlée et plate sur la bande de fréquence. La diversité des trajets utilisés selon la consigne d'état peut ainsi avoir un impact sensible sur la différence d'atténuation d'un déphaseur. Pour les atténuateurs elle correspond à la différence entre l'atténuation obtenue et l'atténuation de consigne; c'est l'objectif principal de conception

de chaque cellule. Cette erreur est prise en compte durant le calcul de l'erreur d'atténuation globale du *core-chip* (erreur d'atténuation des atténuateurs et erreur d'atténuation des déphaseurs).

-l'adaptation en impédance des accès (généralement exprimée en dB) : ce paramètre traduit le rapport d'onde réfléchie (relativement à l'onde incidente) quand le circuit est fermé sur une impédance de référence spécifique ( $Z_0$ ). La valeur de  $Z_0 = 50\Omega$  a été choisie par convention, et ce sera sur cette charge que le niveau d'adaptation d'impédance sera exprimé si rien n'est précisé dans les sections relatives à ce paramètre dans la suite du document. Ce paramètre est particulièrement critique lors de la mise en cascade de plusieurs éléments ; en effet comme il sera détaillé dans la suite du manuscrit, le comportement d'une cellule individuelle (de phase ou d'atténuation) dépend de ses conditions d'ouverture et de fermeture (impédances placées à son entrée/sortie). Ainsi, obtenir un bon niveau d'adaptation de chaque cellule constitutive du core-chip (par exemple >20dB ou <-20dB selon les conventions utilisées) permet de limiter l'influence des cellules les unes sur les autres.

-la bande de fréquence de fonctionnement : elle se définit par la largeur de bande de fréquence (en Hz) sur laquelle les 3 paramètres précédemment cités respectent le cahier des charges. Il est aisé d'imaginer que la réalisation simultanée des critères précédemment cités sera plus difficile à maîtriser conjointement sur une bande de fréquence importante. Ceci aura une grande incidence dans le cas de notre étude.

-la linéarité : La linéarité définit la plage de puissance sur laquelle le gain d'un déphaseur analogique et les pertes d'un déphaseur/atténuateur numérique sont constants. Elle est souvent définie par le point de compression à 1dB ou par le point d'interception d'ordre 3 qui définit le produit d'intermodulation d'ordre trois. Dans le cas de ce travail, ces paramètres sont des éléments importants puisque le GaN, par ses propriétés intrinsèques, offre une linéarité et des niveaux de puissances admissibles supérieurs à ceux de ses concurrents de type GaAs et SiGe. Cependant, l'étude ne validera cet aspect de linéarité que comme étant la conséquence d'une étude exclusive sur les quatre premiers points, c'est-à-dire qu'aucune optimisation ne peut être initialement engagée sur la linéarité a priori des fonctions premières visées.

# 4 Les déphaseurs

Le contrôle de la phase du signal est un élément primordial dans un système de communication à pointage électronique. En effet, c'est du contrôle de la phase de chaque élément du réseau que dépend la précision du pointage de faisceau.

Pour réaliser la fonction de déphasage, deux possibilités existent, les dispositifs de temporisation, ou lignes à retard (*Time delay*), et les déphaseurs. Nous parlons de temporisation quand le déphasage créé est proportionnel à la fréquence de fonctionnement (lors de l'utilisation d'une longueur électrique par exemple). Les temporisations sont principalement utilisées pour des applications où des délais supérieurs à 360° (une longueur d'onde) sont nécessaires. Par exemple dans le cas de radars (ou leurres radar), ces dernières permettent de faire du traitement de signal sur de nombreuses impulsions reçues (émises), en appliquant un délai à celles-ci. Dans le cas de sources de fréquence, les temporisations peuvent permettre de synchroniser des horloges de fréquences différentes. Dans les applications que nous visons, une couverture de 360° est suffisante et permet une largeur de bande de fréquence importante, ainsi notre choix se portera plutôt vers la deuxième catégorie d'éléments de contrôle de phase : les déphaseurs. Ceux-ci se divisent en deux grandes catégories : analogiques et numériques.

#### 4.1 Les déphaseurs analogiques

Le principe général est de faire varier une charge (le plus souvent réactive) grâce à une tension permettant d'ajuster le déphasage souhaité, à l'instar des varactors. Grâce à ce principe ils peuvent

4. LES DÉPHASEURS 5

produire un déphasage continu nécessaire à certaines applications. Le déphasage réalisé est un déphasage absolu, c'est-à-dire qu'il est appliqué sans référence particulière en temps réel selon le contrôle de commande. Les déphaseurs analogiques sont à l'heure actuelle les plus utilisés, mais tendent à être remplacés par leurs homologues numériques. En termes de performances, ils sont très dépendants de la tension de polarisation comme évoqué précédemment, et donc très sensibles aux fluctuations affectant celle-ci. De plus, selon Pozar [7] les erreurs de phase et les pertes d'insertion générées par les déphaseurs analogiques dégradent le gain du réseau total.

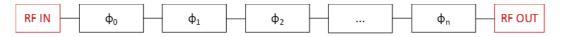

## 4.2 Les déphaseurs numériques

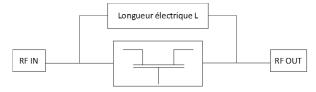

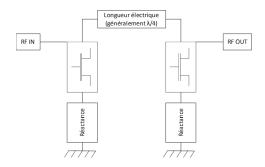

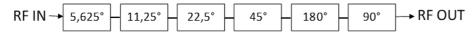

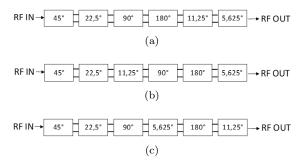

L'appellation numérique vient du fait que ces déphaseurs ont un comportement à deux états distincts assimilables à une logique binaire (ON/OFF), cependant leur fonctionnement intrinsèque reste analogique. Cette fois ci, un déphasage relatif est produit puisque celui-ci est calculé par rapport à un état de référence. Le déphasage total résulte donc de la somme de déphasages d'un ensemble de cellules individuelles. Ainsi chaque combinaison binaire est associée à un déphasage résultant de la mise à 1 ou à 0 de la cellule pilotée par le bit. Un exemple de cette configuration est donné en Figure 1.2 pour une association de n cellules individuelles, et le calcul du déphasage total est précisé en Equation 1.2. Plusieurs topologies de circuits existent et peuvent être classées en quatre catégories : les lignes à retard, les lignes chargées, les déphaseurs à filtres et les topologies réflectives. Ils existent d'autres types de déphaseurs qui sont moins utilisés dans l'industrie au vu de leurs performances moins intéressantes, ils ne seront pas traités dans cet état de l'art.

Figure 1.2 – Schéma d'un déphaseur numérique à n cellules (n bits)

$$\phi_{total} = b_0 \times \phi_0 + b_1 \times \phi_1 + b_2 \times \phi_2 + \dots + b_n \times \phi_n \tag{1.2}$$

Avec  $b_n$  la valeur du bit associé à la cellule n,  $\phi_n$  le déphasage associé à la cellule n et  $\phi_{total}$  le déphasage total.

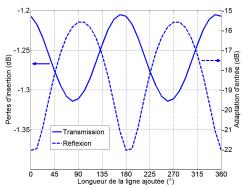

#### La ligne à retard

L'intérêt principal de cette topologie réside dans sa simplicité de conception. En effet le déphasage est produit grâce à la différence de longueur électrique entre les lignes mises en jeu : elle peut être classée dans la catégorie des temporisations car le déphasage est proportionnel à la fréquence. Lorsque la cellule est désactivée le signal passe par l'état dit de référence (le plus souvent par le transistor série). C'est l'état de phase du transistor passant qui va donc déterminer la phase initiale à partir de laquelle le déphasage de la cellule est calculé.

Un compromis apparaît vite entre le déphasage du transistor et les pertes d'insertion (le moins de signal possible doit passer dans la ligne à retard quand le transistor est passant). La ligne à retard est ensuite dimensionnée pour produire un déphasage par rapport à l'état de référence. La Figure 1.3 illustre le fonctionnement de cette topologie, celle-ci est simple de conception mais ne permet pas d'obtenir de déphasages importants, principalement à cause de l'encombrement engendré par la ligne qui devient vite problématique avec l'augmentation du déphasage souhaité. De plus, la longueur électrique variant avec la fréquence, la différence de longueur électrique entre la ligne de référence et la ligne à

retard n'est pas constante, l'équation décrivant le fonctionnement de ce type de déphasage est donnée en Equation 1.3.

Figure 1.3 – Topologie de déphaseur à base d'une ligne à retard de longueur électrique L

Ceci empêche l'obtention d'un déphasage constant sur toute le bande de fréquence. Toutefois, lorsque des déphasages moins importants sont nécessaires cette topologie offre une facilité d'adaptation et de faibles pertes d'insertion assimilables au premier ordre à celles des commutateurs composant l'élément. La mise en parallèle d'un transistor en commutation et d'une ligne entraı̂ne automatiquement une résonance due à la capacité  $C_{off}$  du transistor. Pour éviter que ce comportement se manifeste dans la bande de fréquence d'intérêt, le couple transistor/ligne est soigneusement choisi. Il n'y a pas de limitation physique au déphasage atteignable mais le plus souvent cette topologie est utilisée pour des déphasages inférieurs à  $20^{\circ}$ .

$$\Delta \phi = \frac{2 \times \pi \times f}{v_p} \times (l_{transistor} - l_{ligne}) \tag{1.3}$$

Avec  $\Delta \phi$  le déphasage souhaité, f la fréquence du signal de porteuse,  $v_p$  la vitesse de phase et  $l_{transistor}$  et  $l_{liqne}$  correspondant respectivement aux longueurs électriques du transistor et de la ligne.

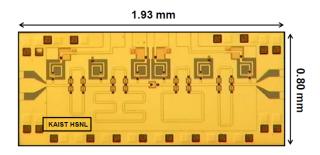

Il est rare de trouver des circuits MMIC exploitant uniquement une cellule de déphasage et utilisant une ligne à retard. Et même dans le cas contraire, il est rare d'obtenir des renseignement sur la cellule individuelle, en raison de la simplicité de mise en œuvre d'un tel système. En effet cette topologie peu complexe ne nécessite pas d'aménagement circuit particulier. Il existe cependant des déphaseurs utilisant uniquement des topologies à base de ligne à retard [8] [9] [10]. Le plus souvent, l'élément de commutation utilisé est la diode PIN. Malgré sa facilité d'intégration et sa haute tenue en puissance, sa consommation statique lui fait perdre l'avantage face à un transistor en commutation. En Figure 1.4 est donné un exemple de ce type de topologie. Un grand nombre de diodes PIN est utilisé, celles-ci devant être pilotées par des courants typiques de 20mA, la consommation statique de l'ensemble est très importante. Les différences de longueur de ligne (haut et bas) sont bien visibles et sont responsables du déphasage des cellules successives (respectivement de  $180^\circ$ ,  $90^\circ$ ,  $45^\circ$ ,  $22.5^\circ$ ,  $11.25^\circ$  et  $5.625^\circ$  de la gauche vers la droite). L'espace occupé de  $32.4\text{mm}^2$  en fait une puce extrêmement encombrante à cette fréquence.

La Figure 1.5 illustre la faisabilité de circuit beaucoup plus compact grâce à des lignes à retard (1.544mm²). Cependant cette réduction de taille s'explique par l'augmentation de la fréquence et donc de la réduction de la longueur d'onde du signal. Les applications visées par ce type de circuits sont plutôt les radars alors que le circuit de la Figure 1.4 semble plus approprié pour des applications de télécommunications de type 5G.

Une réalisation de lignes à retard exploitant des transistors comme élément de commutations est présentée en Figure 1.6. Dans le cas de ce circuit, les transistors utilisés sont dits non résonnants, cela se traduit par une isolation de l'élément de commutation bien moins dépendante de la capacité  $C_{off}$  du transistor utilisé. Du fait de leur grande taille et de leur consommation statique importante dans certains cas, ce type de topologie est rarement utilisée pour obtenir des performances à l'état de l'art.

4. LES DÉPHASEURS 7

FIGURE 1.4 – Exemple de déphaseur 6 bits AlGaAs à base de ligne à retard fonctionnant de 27.5 à 29.5 GHz pour une taille de 7.34\*4.41mm² [1]

Figure 1.5 – Exemple de déphaseur 4 bits InGaAs fonctionnant à 81GHz [9]

#### La ligne chargée

Cette topologie consiste à utiliser une ou plusieurs charges réactives en shunt placées à un niveau stratégique du circuit comme illustré en Figure 1.7. Cette charge va, quand elle est connectée, influer sur la phase du circuit tout en préservant l'amplitude du signal. Les pertes d'insertion de ce type de topologie sont encore une fois déterminées par les pertes des commutateurs. En effet, ceux-ci ne peuvent présenter ni charge purement réactive à l'état OFF ni de résistance nulle à l'état passant  $(R_{on})$ , ces commutateurs fixent donc les limites du circuit. Selon [11] après l'étude de la matrice chaîne du quadripôle formé par le circuit, trois paramètres sont à déterminer : l'impédance de la ligne, la valeur des susceptances des charges et la longueur électrique de la ligne entre les deux charges. Cette topologie est généralement utilisée pour des déphasages inférieurs à 45° et propose une meilleure platitude de phase. Cependant, il est souvent nécessaire que la distance entre les deux charges soit de l'ordre de  $\lambda/4$  ( 2.9mm à 35GHz), et la taille devient donc un facteur préjudiciable au choix de cette topologie. Ces raisons font que cette topologie est rarement utilisée à la fréquence d'intérêt.

Ce type de topologie n'est que très rarement utilisée en bande Ka. La Figure 1.8 montre un exemple d'utilisation de cette topologie, le repère spatial en bas de la figure confirme bien la taille bien trop importante (6cm de longueur) de ce type de circuit. Malgré la fréquence bien en deçà de la fréquence ciblée, ces topologies ne sont pas citées dans le tableau regroupant les performances à l'état de l'art des différents types de déphaseurs.

$FIGURE\ 1.6-Exemple\ de\ déphaseur\ 4\ bits\ InGaAs\ HJFET\ fonctionnant\ entre\ 33\ et\ 36\ GHz\ pour\ une\ taille\ de\ 2.5*2.2mm^2\ [10]$

Figure 1.7 – Topologie de déphaseur à base de type ligne chargée

FIGURE 1.8 – Exemple de topologie à base de ligne chargée proposant un déphasage de  $90^\circ$  à  $1.8 \, \mathrm{GHz}$  [12]

### Topologies à filtre(s)

La topologie dite à filtre utilise les propriétés en phase des filtres passe-haut et/ou passe-bas. Ils proposent des déphasages constants sur de larges bandes de fréquences. Même si la topologie simple qui propose une commutation entre un chemin électrique de référence et un filtre ne peut pas dépasser un déphasage absolu de 90°, en commutant entre deux filtres proposant chacun un déphasage allant jusqu'à 90° et -90° il est possible d'obtenir un déphasage de 180°. Pour ce dernier déphasage, cette topologie est la plus adaptée puisqu'elle offre les meilleures performances en termes de platitude de phase et de largeur de bande. Ce qui en fait la topologie la plus utilisée dans les *core-chips*. Selon la

4. LES DÉPHASEURS 9

fréquence d'intérêt le choix entre filtre passe-bas et filtre passe-haut est fait. Sachant que pour les passe-haut, la capacité sur la ligne série peut être réalisée grâce à la capacité  $C_{off}$  du transistor. Pour garder un bon contrôle de la capacité série équivalente, la mise en parallèle du transistor et d'une capacité fixe est préférable. Il faut garder à l'esprit que le transistor détermine aussi les pertes d'insertion, avec le  $R_{on}$  présenté à l'état passant du transistor ; un compromis est donc à faire pour trouver la meilleure capacité en fonction des pertes d'insertion visées. La topologie en Figure 1.9 illustre un fonctionnement idéal, cependant quand le transistor série est passant, le filtre présente une impédance trop faible et dégrade les pertes d'insertion du système.

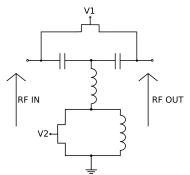

Figure 1.9 – Topologie de déphaseur à base de filtre commuté

Pour s'affranchir de cet effet il est nécessaire de fermer les branches shunt du filtre sur des circuits ouverts et non sur des masses. Néanmoins les masses sont nécessaires à l'état actif de la cellule, c'est pourquoi un second transistor est obligatoire. Ce dernier connecte les deux branches shunt du filtre, et assure une mise à la masse pour l'état actif de la cellule et une mise en haute impédance pour l'état bloqué de la cellule. Pour réaliser la mise à haute impédance on crée un « circuit bouchon » en mettant une inductance en parallèle au transistor. Ces masses et circuits ouverts n'étant pas parfaits, les performances du circuit sont dégradées.

Pour étudier ce type de topologies, il faut d'abord s'intéresser aux propriétés en phase des différents filtres. Les deux types de filtres les plus utilisés sont les topologies en T et les topologies en  $\pi$ . Ces filtres sont composés d'éléments réactifs (capacité et inductance) responsables du décalage en phase du signal qui les traverse. Selon la nature de l'élément placé sur la voie directe (inductif ou capacitif), le filtre sera qualifié de passe-bas (inductance) ou passe-haut (capacité). Les 4 différentes possibilités de filtres sont répertoriées en Figure 1.10a à 1.10d.

FIGURE 1.10 – Topologies à base de filtres commutés (a) en T<br/> passe-haut (b) en T<br/> passe-bas (c) en  $\pi$  passe-haut (d) en  $\pi$  passe-bas

Les formules permettant de trouver les valeurs des éléments du filtre sont données en Equation 1.4 et 1.5 pour les topologies en T et en Equation 1.6 et 1.7 pour les topologies en  $\pi$ .

$$Passe - haut : L = \frac{Z_0}{\omega \sin(\phi)} \quad ; \quad C = \frac{\sin(\phi)}{\omega Z_0 (1 - \cos(\phi))}$$

(1.4)

$$Passe - bas : L = Z_0 \frac{(1 - \cos(\phi))}{\omega \sin(\phi)} \quad ; \quad C = \frac{\sin(\phi)}{\omega Z_0}$$

(1.5)

$$Passe - haut : L = \frac{Z_0 \sin(\phi)}{\omega (1 - \cos(\phi))} \quad ; \quad C = \frac{1}{\omega Z_0 \sin(\phi)}$$

(1.6)

$$Passe - bas : L = Z_0 \frac{\sin(\phi)}{\omega} \quad ; \quad C = \frac{1 - \cos(\phi)}{\omega Z_0 \sin(\phi)}$$

(1.7)

Avec,  $\phi$  le déphasage souhaité,  $\omega$  la pulsation et  $Z_0$  l'impédance sur laquelle le circuit sera adapté. Une fois le déphasage ciblé obtenu, un élément de commutation est nécessaire pour choisir ou non de déphaser le signal. Dans ce type de topologie, le transistor en commutation est mis en parallèle au filtre, sa réactance doit donc être prise en compte lors de la simulation du filtre. Comme expliqué précédemment, la capacité  $C_{off}$  du transistor peut être utilisée pour un dispositif passe-haut. Cependant dans le cas d'un dispositif passe-bas, il faut veiller à ce que l'inductance série ne fasse pas résonner le transistor. De plus selon la fréquence de fonctionnement étudiée, certaines valeurs de composants seront impossibles à atteindre (spatialement ou juste trop importante). La topologie choisie devra donc prendre en considération les valeurs accessibles à la technologie GaN.

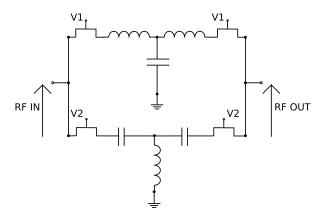

Il a été expliqué plus tôt que lorsque la cellule ne déphase pas, les branches parallèles des différents filtres doivent avoir l'extrémité non connectée au transistor série mise à la masse. Dans le cas contraire l'impédance présentée par le filtre viendrait perturber l'état de référence de la cellule. Un circuit bouchon est généralement utilisé pour réaliser cette fonction. La Figure 1.11 résume le fonctionnement de la cellule avec l'ajout du circuit bouchon.

Figure 1.11 – Topologie en T passe-haut avec circuit bouchon

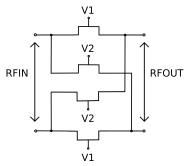

Les deux tensions de polarisation de grille  $V_1$  et  $V_2$  sont complémentaires et vont tour à tour rendre passant et bloqué les transistors concernés. Lorsque V1 est égale à 0V le transistor en série est passant, le filtre en T est donc court-circuité par la résistance  $R_{on}$  équivalente dudit transistor. La tension V2 est quant à elle inférieure à la tension de pincement  $(V_{off})$  du transistor shunt, ce qui le met dans l'état bloqué. La mise en parallèle de la capacité  $C_{off}$  du transistor shunt et de l'inductance entraîne une résonance à la fréquence souhaitée. La haute impédance ainsi présentée permet de réduire l'influence du filtre sur l'impédance vue par le signal d'entrée. La cellule ne déphase pas et est dite à l'état de référence.

4. LES DÉPHASEURS 11

Lorsque  $V_1$  est égale à  $V_{off}$  le transistor série est bloqué et la capacité  $C_{off}$  équivalente vient s'ajouter en parallèle à la branche série du filtre.  $V_2$  est égale à 0V, la branche shunt du filtre est donc mise à la masse par la résistance  $R_{on}$  équivalente du transistor. La cellule est activée et se place dans la configuration de déphasage. Les Figures. 1.12a et 1.12b illustrent les deux états de la cellule par les schémas électriques équivalents. Le modèle en T choisi n'est qu'un exemple, le fonctionnement selon deux états du circuit est le même quelles que soient la configuration et la topologie choisies.

Théoriquement le circuit bouchon ne doit pas avoir d'influence sur l'état de phase de la cellule, en réalité il n'est pas possible d'obtenir un circuit ouvert et un court-circuit parfait. Pour cela, il est nécessaire de trouver un circuit bouchon permettant simultanément un respect de la consigne de phase et une bonne résonance, responsable d'une bonne adaptation et de pertes d'insertion réduites. Le choix de la tension  $V_{off}$  va fixer l'ondulation RF acceptable sans changement d'état du transistor. Elle est donc directement liée à la compression du circuit.

FIGURE 1.12 – Topologie en T passe-haut (a) à l'état de référence, le circuit bouchon résonne (b) le circuit bouchon se comporte comme un fil vers la masse

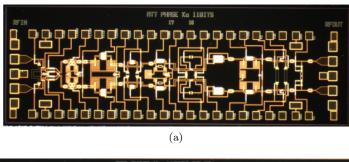

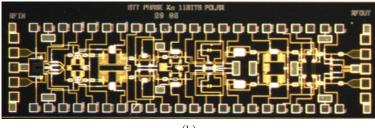

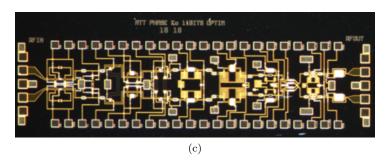

Cette topologie est la plus utilisée en bande Ka du fait de la platitude de phase sur la bande de fréquence et de la compacité des éléments lors d'intégrations monolithiques. Nous allons maintenant présenter quelques réalisations de déphaseurs utilisant ce type de topologies. La majorité des réalisations sont conçues en technologie SiGe et GaAs [13]-[14] et sont intégrées à des puces d'émission/réception (Tx/Rx), il est rare de trouver des déphaseurs seuls. La Figure 1.13a illustre un exemple de cellule réalisée en GaN. On peut voir qu'une grande partie de la surface du circuit est occupée par les différentes inductances (d'autant plus grandes en bande X).

Pour obtenir des déphasages supérieurs à 90°, il existe la possibilité de mettre en cascade deux déphaseurs dont la somme des variations en phase dépasse les 90° ou alors d'utiliser les propriétés en avance et retard de phase des filtres comme évoqué précédemment. En effet, en utilisant le retard en phase des filtres passe-bas et l'avance en phase des filtres passe-haut il est possible, en les disposant en parallèle, d'obtenir des déphasages supérieurs à 90° et ce avec une seule cellule. En commutant entre les deux voies, le déphasage obtenu sera la somme des valeurs absolues des déphasages respectifs de chaque filtre. L'élément assurant la commutation ne doit pas influer sur le déphasage de chaque filtre, et doit garantir une isolation suffisante pour que les deux états de phase possibles du circuit soient indépendants. La topologie en  $\pi$  est schématisée en Figure 1.14; il y a été choisi deux topologies en T, ce qui n'est bien entendu pas imposé. De même pour la commutation, un simple transistor série est la solution la plus simple bien que des topologies de type Single Pole Double Throw (SPDT) bien plus élaborées puissent être préférées pour privilégier la linéarité, l'isolation ou d'autres paramètres. L'étude des SPDT est détaillée dans un chapitre entier de [16], nous ne nous intéresserons pas plus aux SPDT qui sont des commutateurs dont l'utilisation est plus orientée vers des applications de type puissance.

La seule obligation régissant cette topologie est d'avoir un déphasage positif sur un bras et négatif sur l'autre. L'utilisation de telles structures peut être envisagée pour notre application, cependant du fait de la mise en série de deux transistors (au moins) sur la voie passante les pertes d'insertion sont

FIGURE 1.13 – Exemple de cellule de déphasage  $(22.5^{\circ})$  en GaN (a) circuit réalisé en bande X de dimension  $0.448 \times 0.678 \text{mm}^2$  (b) modélisation électrique de la topologie en T passe-bas [15].

Figure 1.14 – Topologie filtre passe-haut/passe-bas en T

grandement augmentées. Néanmoins cette structure se base sur le déphasage relatif entre deux filtres, ainsi le déphasage du transistor (identique sur les deux voies) n'entre pas en compte dans le déphasage total de la cellule, en dehors d'éventuelles dispersions technologiques qui peuvent généralement être simulées si les modèles statistiques associés au kit de conception sont disponibles. La platitude de phase est donc améliorée. Un compromis apparaît donc entre platitude de phase et pertes d'insertion du circuit. Les équations utilisées pour trouver la valeur des éléments des filtres sont les mêmes que celles régissant les topologies passe-haut et passe-bas simples étudiées plus haut (équations 1.4 à 1.7 et Figure 1.10a à 1.10d).

Des variantes à cette topologie peuvent être utilisées comme l'illustrent par exemple les travaux de Zhou [13] et Zheng [17]. Dans ce type de configuration, le délai ou l'avance en phase est obtenue d'un côté par un filtre et sur l'autre branche par un élément de type ligne ou coupleur par exemple. La difficulté consiste à obtenir un niveau d'adaptation et de pertes d'insertion égal dans les deux états de fonctionnement du déphaseur.

4. LES DÉPHASEURS 13

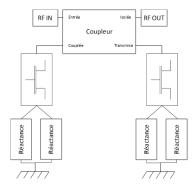

#### Topologie "réflective"

La dernière topologie dite réflective, utilise les propriétés en phase des coupleurs comme l'illustre la Figure 1.15. A la sortie des ports transmis et couplé sont placées deux charges identiques calculées de telle façon à ce qu'elles présentent un coefficient de réflexion bien connu vis-à-vis de l'impédance du coupleur. Ces deux voies étant chacune déphasée de 90° par rapport à l'autre, nous pouvons exprimer la valeur du déphasage du signal de sortie par le port isolé (vers où les ondes couplées et transmises seront réfléchies). Ces déphaseurs permettent aussi d'atteindre des changements de phase allant jusqu'à 180°. Cependant, ils ont une bande de fonctionnement assez étroite, et occupent un espace plus large. De ce fait, les charges présentées à leurs sorties peuvent être variables et contrôlées en tension, de façon à pouvoir obtenir plusieurs déphasages différents avec la même structure. Dans ce cas les structures exploitent un fonctionnement analogique.

Figure 1.15 – Topologie de déphaseur dit "réflectif"

Bien que nous ayons vu précédemment que les topologies réflectives de déphaseurs (RTPS) sont plutôt utilisées dans des configurations de circuits analogiques, il est intéressant d'étudier certaines structures, et de les implémenter pour un fonctionnement assimilable à une application à commande numérique. Un élément reste commun à toutes ces structures, le coupleur. En effet les améliorations sur les topologies RTPS viennent pour l'essentiel d'une complexification des charges de sortie pour obtenir les performances souhaitées (déphasage, faible perte d'insertion, compacité...). De nombreuses publications [18]-[19] s'intéressent à l'optimisation des charges de sortie et des propriétés du coupleur pour obtenir des déphasages très importants (jusqu'à 360°), tout en gardant des pertes d'insertion inférieures à celles des topologies de types filtres commutés. En effet, commuter entre deux chemins différents, et devoir cascader plusieurs cellules pour augmenter la résolution du déphaseur dégrade fortement les pertes de celui-ci. Bien que les solution RTPS ne soient pas toujours aptes à des intégrations monolithiques, elles présentent des performances à l'état de l'art.

### Autres topologies de déphaseurs

Il existe des types de déphaseurs plus exotiques, à base de microsystèmes électromécaniques (MEMS) [20]–[21], ou bien de ferrites [22]. Nous avons placé ces références à titre purement informatif et elles ne seront pas considérées dans l'état de l'art en raison de leurs performances insuffisantes, à l'heure actuelle, en bande Ka; et également parce qu'elles ne sont pas implémentées dans le procédé technologique utilisé.

#### Comparatifs des performances de déphaseurs en bande Ka

Maintenant que nous avons présenté les différents types de topologies utilisables pour la conception des déphaseurs, nous pouvons comparer les performances de celles-ci selon la technologie choisie. Le Tableau. 1.2 présente les performances des déphaseurs micro-ondes à l'état de l'art. Dans ce tableau, nous avons jugé judicieux de ne pas inclure les performances des déphaseurs contenus dans les corechips. En effet dans plusieurs travaux, les déphaseurs ne sont jamais implémentés individuellement mais ils sont plutôt intégrés au sein de core-chips. Il ne nous a pas semblé juste de les comparer puisque tous les aspects notamment de type consommation et, compacité sont faussés par l'intégration du déphaseur dans un système complet. Ces déphaseurs seront traités dans le comparatif sur les corechips. Nous pouvons clairement voir que le CMOS présente de meilleurs performances que les circuits III-V présentés, que ce soit sur les erreurs fonctionnelles ou sur la compacité. Les seuls points négatifs sont la bande de fréquence de fonctionnement (seulement 28GHz) et le point de compression qui n'est pas indiqué mais qui est certainement plus bas que celui des déphaseurs III-V.

| Référence               | [18]               | [23]                | [10]               | [17]                 | [24]                  |

|-------------------------|--------------------|---------------------|--------------------|----------------------|-----------------------|

| Technologie             | 65nm CMOS          | GaAs pHEMT          | GaAs HJFET         | InGaAs pHEMT         | InGaAs PIN Diode      |

| Topologie               | RTPS               | Filtres             | Lignes à retard    | Filtres et RTPS      | Filtres               |

| Fréquence (GHz)         | 28                 | 32-37               | 33-36              | 31-40                | 26-30                 |

| Erreur RMS Phase        | 0.3°               | 3.5°                | 7°                 | 4.7°                 | 5.6°                  |

| Erreur RMS Amplitude    | 0.3 dB (non RMS)   | 0.4dB               | 0.9dB (@34.5 GHz)  | 0.6 dB               | 0.7dB                 |

| Pertes d'insertion (dB) | 8.05               | 7                   | 15                 | 8.8                  | 7.8                   |

| Adaptation (dB)         | 6.7                | 7                   | 10dB (@34.5 GHz)   | 9                    | 9                     |

| Résolution Phase        | 11.25°             | 11.25°              | 22.5°              | 11.25°               | 11.25°                |

| Compacité               | $0.16 \text{mm}^2$ | 1.41mm <sup>2</sup> | 5.5mm <sup>2</sup> | 3.315mm <sup>2</sup> | 2.3436mm <sup>2</sup> |

| Consommation (W)        | 0                  | 0                   | 0                  | 0                    | 0,                    |

| $P_{1db}$ (dBm)         | Non spécifié       | 20                  | Non spécifié       | 16 (sortie)          | 21 (entrée)           |

Table 1.2 – Etat de l'art des déphaseurs en bande Ka

Maintenant que nous avons présenté les différentes topologies de déphaseurs nous pouvons nous intéresser aux seconds constituants des *core-chips* les atténuateurs.

### 5 Les atténuateurs

Selon l'application visée, les atténuateurs peuvent tenir plusieurs rôles :

-les systèmes de leurre : le principe est de faire croire aux récepteurs ennemis qu'un élément se trouve à une position, alors qu'il se trouve à une position décalée. Atténuer volontairement un signal peut permettre de réaliser cette fonction en remplaçant la signature électromagnétique réelle d'un objet (en amplitude ici, donc en faussant la distance perçue) par la signature factice générée.

-Le pointage électronique d'antenne : même si dans cette configuration l'objectif est d'obtenir un bilan de liaison au gain maximum, atténuer certains signaux alimentant un réseau d'antennes permet d'augmenter la directivité du faisceau en réduisant la puissance transmise aux lobes secondaires [7].

Dans cette partie nous étudierons les différents types d'atténuateurs micro-ondes existant :

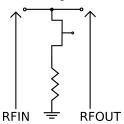

Pour atténuer le signal, l'utilisation d'éléments résistifs (dissipatifs) est incontournable. Il existe plusieurs agencements de résistances qui répondent à la fonction recherchée. La topologie la plus simple est de placer une résistance en shunt sur la voie RF comme illustré en Figure 1.16. Cette résistance ne doit pas être du même ordre de grandeur que la résistance série de la ligne. En connectant ou déconnectant cette résistance, nous obtenons un atténuateur numérique. Plus la résistance shunt est grande plus l'atténuation est faible. Cependant, cette topologie ne permet pas d'obtenir des atténuations élevées puisque très vite les pertes d'insertion augmentent. Le gros avantage de cette technique, au-delà de sa

simplicité de mise en œuvre, est la très faible phase d'insertion générée. Dans les circuits de contrôle, les erreurs croisées (erreur de phase de l'atténuateur et erreur d'atténuation du déphaseur) sont très importantes. En effet, celles-ci rentrent en compte dans le calcul des erreurs RMS de la structure finale. Pour les atténuateurs, la phase d'insertion générée provient de la différence entre les deux chemins empruntés par le signal. L'utilisation de transistor en commutation introduit immanquablement des éléments réactifs qui perturbent la phase. Cet effet est d'autant plus important si le nombre de transistors sur les voies est différent, ou bien si ceux-ci sont de tailles différentes. La première topologie proposée en Figure 1.16 engendre peu de déphasage puisqu'il n'y a pas de transistor sur la voie directe et que le transistor shunt est vu comme un circuit quasi ouvert quand il est OFF. Cependant, en distribuant les résistances le long de la ligne directe (plusieurs transistors shunt en parallèle pour réduire la résistance équivalente shunt présentée), la gestion de cette phase devient plus compliquée ; c'est aussi pour cette raison que les niveaux d'atténuation importants sont inaccessibles avec cette topologie.

Figure 1.16 – Mise en série d'une résistance pour atténuer le signal incident

Lorsqu'une dynamique d'atténuation plus importante est nécessaire, deux topologies émergent : les réseaux résistifs en T et en  $\pi$ . Elles sont assez similaires et il est assez aisé de passer mathématiquement de l'une à l'autre, elles sont représentées en Figure 1.17. Ces topologies sont les plus utilisées car elles sont simples à mettre en œuvre et couvrent une très large gamme d'atténuation. Pour des applications numériques, la topologie en  $\pi$  est peut-être avantageuse, puisqu'une partie de la résistance série du réseau peut être obtenue grâce à la résistance  $R_{on}$  du transistor série. Comme explicité plus tôt, commuter entre une ligne simple et une cellule d'atténuation va engendrer une différence de phase ; c'est pour cela qu'intégrer la voie passante directement à l'atténuateur est une bonne alternative non seulement pour la réduction de la phase d'insertion mais aussi pour l'amélioration de la compacité du circuit. Une autre considération lors du choix entre  $\pi$  et T concerne les valeurs des résistances mises en jeu. En effet, pour des résistances à valeurs trop élevées, celles-ci peuvent présenter des comportements distribués, ce qui influe donc sur la phase des signaux.

FIGURE 1.17 – Topologie proposant des atténuation plus importantes : (a) réseau en  $\pi$  (b) réseau en T

Les formules théoriques régissant ces atténuateurs sont données en équations 1.8 et 1.9. Avec ce type de topologie, pour des niveaux d'atténuation importants, il est nécessaire de compenser la phase qui est différente entre les deux états.

Rseau en

$$\pi: R_1 = \frac{Z_0}{2} \cdot \frac{10^{A/10} - 1}{10^{A/20}}; \quad R_2 = Z_0 \cdot \frac{10^{A/20} + 1}{10^{A/20} - 1}$$

(1.8)

Rseau en

$$T: R_1 = Z_0 \cdot \frac{10^{A/20} - 1}{10^{A/20} + 1}; \quad R_2 = 2 \cdot Z_0 \cdot \frac{10^{A/20}}{10^{A/10} - 1}$$

(1.9)

Avec A l'atténuation souhaitée en dB (A=10. $\log(P_{in}/P_{out})$ ), et  $Z_0$  l'impédance caractéristique sur laquelle adapter le réseau.

Obtenir une atténuation constante sur la bande de fréquence n'est pas la contrainte la plus critique. En effet, une résistance même non idéale présente peu de parasites réactifs qui pourraient faire varier son comportement en fréquence. La taille de cette dernière en revanche ne doit pas être trop importante pour éviter les problèmes d'effets distribués. La contrainte principale lors de la conception d'atténuateur est la phase d'insertion entre les deux états. En effet lors du calcul des valeurs de résistances, aucune phase n'est prise en compte. Néanmoins, du fait de la taille du circuit (différentes longueurs électriques parcourues par le signal selon l'état de la cellule), de l'ajout de transistors pour assurer la commutation, ou de lignes pour relier les éléments du circuit entre eux, des phases parasites viennent s'ajouter. Cette considération est d'autant plus sensible à hautes fréquences (bande Ka dans notre étude). Pour limiter ces effets, diverses solutions sont envisageables. La plus simple et de rajouter de la longueur électrique sur le chemin de référence. Cette solution fonctionne au prix de pertes d'insertion plus importantes. D'autres solutions ont été adoptées pour réduire cette phase d'insertion parasite [25]-[26]. Par exemple ajouter un élément réactif (plutôt capacitif dans la branche shunt du réseau), ou bien allonger les lignes d'accès (ajout d'une inductance) à la résistance en haut des circuits de la Figure 1.17 pour compenser l'écart de phase [27]. Cependant cette dernière solution augmente grandement les pertes d'insertion du circuit. Les performances d'un atténuateur sont évaluées sur les mêmes critères que ceux pour juger des performances des déphaseurs. Le poids de chaque performance étant cependant différent selon l'application voulue.

D'autres topologies d'atténuateurs, telle que le *Bridge T-Attenuator* peuvent être utilisées, mais sont plus exotiques et parfois difficilement conciliables avec les paramètres de notre étude. Pour le *Bridge T-Attenuator* par exemple, la nuance avec un simple *T-Attenuator* réside l'ajout d'une résistance parallèle sur la voie série. Cette légère nuance n'apporte pas grand-chose au circuit étant donné que nous plaçons déjà un transistor parallèle pour réaliser la commutation, ce qui revient quasiment à une topologie *Bridge-T*. Ces topologies sont présentées dans [28]. Le nombre de topologies d'atténuateurs étant plus restreint que ceux des déphaseurs, nous présentons directement dans le tableau 3 les atténuateurs à l'état de l'art. Comme pour les déphaseurs, ne figurent dans ce tableau que les atténuateurs « seuls » et pas ceux intégrés à un *core-chip*.

Une fois les deux éléments constitutifs des *core-chips* identifiés et présentés, nous pouvons nous intéresser à la mise en commun de ces éléments pour l'obtention de la fonction finalisée atténuation/déphasage numérique. Pour cela il faut regrouper toutes les cellules individuelles, avec les cellules de poids fort (dynamique) et de poids faible (sélectivité) de chaque fonction, et comme il est explicité dans la section suivante cela nécessite une méthodologie particulière.

# 6 Les core-chips

Dans cette section nous n'étudierons pas la mise en commun des cellules; en effet cet aspect nécessite une analyse plus complète qui sera détaillé dans le Chapitre 3 et sera suivie de la méthodologie d'intégration que nous avons développée. Dans cette partie nous étudierons les *core-chips* en tant que système, de leur fonctionnement général vers les réalisations existantes à l'état de l'art.

6. LES CORE-CHIPS 17

| Référence               | [29]               | [23]               | [30]                 | [26]                   |

|-------------------------|--------------------|--------------------|----------------------|------------------------|

| Technologie             | GaAs pHEMT         | GaAs pHEMT         | GaAs pHEMT           | SiGe BiCMOS            |

| Fréquence (GHz)         | DC-35              | 0.1-31             | 20-40                | 19-24                  |

| Erreur RMS Amplitude    | 0.2dB              | 0.9dB              | 1.2dB                | $0.5 \mathrm{dB}$      |

| Erreur RMS Phase        | 12°                | NC                 | 7.2°                 | 4.1°                   |

| Pertes d'insertion (dB) | 4.5                | 4.2                | 8.8                  | NC                     |

| Adaptation (dB)         | 12                 | 9                  | 15                   | 19                     |

| Résolution Amplitude    | 1dB                | $0.5 \mathrm{dB}$  | $0.5 \mathrm{dB}$    | 0.5 dB                 |

| Compacité               | 4.1mm <sup>2</sup> | $0.94 \text{mm}^2$ | $1.47 \mathrm{mm}^2$ | $0.51 \mathrm{mm}^{2}$ |

| Consommation (W)        | 0                  | 0                  | 0                    | 0                      |

| $P_{1db} (dBm)$         | 20 (entrée)        | NC                 | 24 (entrée)          | NC                     |

Table 1.3 – Etat de l'art des atténuateurs

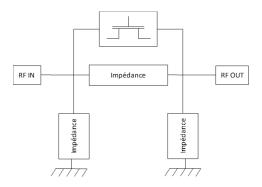

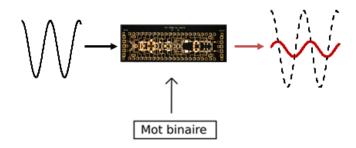

Pour décrire grossièrement un core-chip, il est possible de le considérer comme un système avec une entrée et une sortie. Sur l'entrée sera envoyé un signal, et selon la commande appliquée par un mot binaire, ce signal sera transmis en sortie affecté d'une combinaison phase/amplitude. La précision atteinte sur la commande de phase et d'amplitude dépend de la résolution du core-chip. Cette dernière est associée à la taille du mot binaire d'entrée (et plus précisément aux bits de poids faibles). La Figure 1.18 illustre le fonctionnement du système. Pour évaluer les performances d'un core-chip, il suffit de regarder les performances des déphaseurs et atténuateurs ensembles. Ainsi le core-chip présentera une erreur globale de phase et une erreur globale d'amplitude. Attention cependant à bien préciser quelles erreurs sont prises en compte, car dans certaines documentations techniques l'erreur de phase du core-chip est évaluée uniquement sur les états du déphaseur et inversement l'erreur d'amplitude est calculée que sur les états d'atténuation.

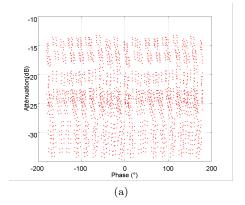

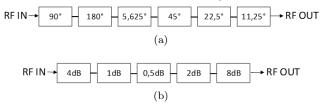

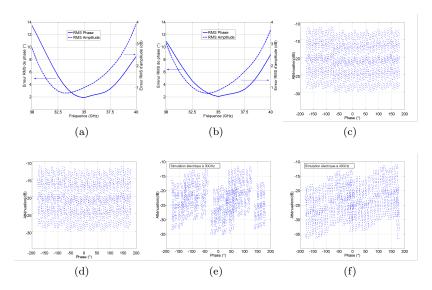

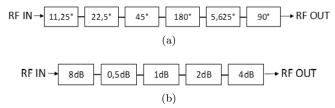

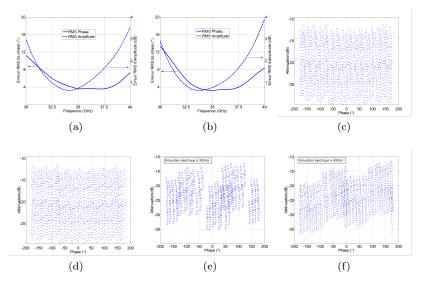

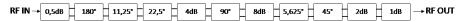

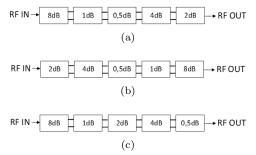

Concernant la résolution, la dynamique globale du core-chip est morcelée en niveau de phase et d'atténuation respectant le plus souvent une loi binaire. Par exemple, un core-chip ayant une résolution en phase de 6 bits et en amplitude de 4 bits présentera 6 cellules de déphasage et 4 cellules d'atténuation. La couverture maximale pour ce type de système étant de 360°, la cellule au déphasage le plus important sera de 180° puis dans un ordre décroissant les cellule suivantes auront un déphasage divisé par 2 (90°, 45°,..., 180/2n -1°). De même pour l'atténuation, excepté que le choix se fait plutôt selon la plus petite atténuation ('pas' d'atténuation, ou résolution). Ainsi la dynamique d'atténuation sera de  $A_1 + A_2 + ... + A_n$  ( $A_i$  en dB), avec  $A_1 = A_1.2n - 1$  (avec n>1) et  $A_1$  l'atténuation minimale choisie. Ainsi pour le core-chip cité plus haut, 6 bits de phase donnent une résolution de 5.625° et une dynamique de 360°, tandis que 4 bits d'atténuation peuvent conduire à une dynamique de 4 dB en choisissant une résolution de 0.5dB, contre 16 dB avec 6 bits en conservant la même résolution.

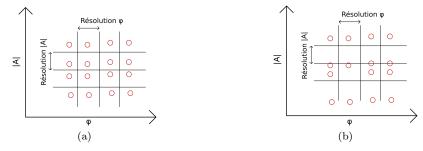

Instinctivement, l'idée d'augmenter le nombre de cellules pour avoir une résolution maximale vient à l'esprit. Cependant, augmenter la résolution s'accompagne nécessairement d'une augmentation des pertes d'insertion du fait de la mise en commun d'un nombre plus important de cellules. Pour garantir une résolution significative, il faut que l'erreur soit inférieure à la moitié de la résolution. Ce critère devient donc très contraignant, spécialement en phase où par exemple, pour des résolutions de 5.625°, l'erreur ne doit pas dépasser 2.8°. La Figure 1.19 illustre cette contrainte de manière explicite avec des gabarits de résolution de phase et d'amplitude. Lors de l'examen d'un document technique ou lors de la conception d'un core-chip, il faut donc veiller à ce que l'erreur respecte bien cette contrainte de façon à pouvoir exploiter pleinement le nombre de cellules du core-chip réalisé, et optimiser ainsi les pertes globales du module conçu.

Les core-chips réalisent des fonctions de contrôle, fonctions intégrées dans un système plus global

Figure 1.18 - Schéma de principe d'un core-chip n bits

d'émission réception in fine. Ainsi, dans la littérature, les performances des core-chips sont évaluées à travers la puce globale Tx/Rx dans laquelle ils sont intégrés. Malgré tout, les performances individuelles du core-chip sont importantes puisque, les autres éléments de la chaîne (amplificateur faible bruit, amplificateur forte puissance...) n'impactent pas les performances en phase et en amplitude.

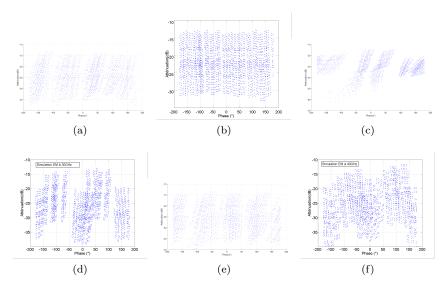

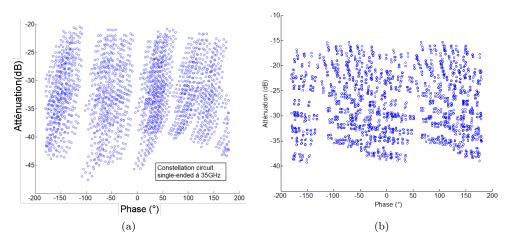

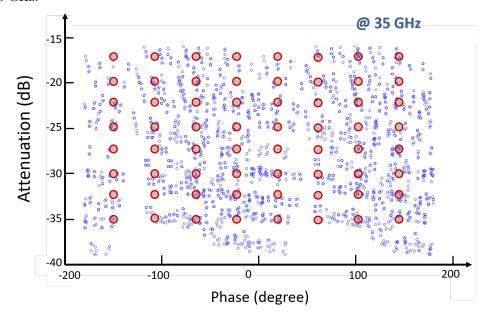

Figure 1.19 – Exemple de constellations d'états de phase/atténuation (cercle rouge) où (a) la résolution théorique visée (quadrillage) est cohérente avec la résolution finale synthétisée (O) (b) la résolution théorique est inférieure à la résolution finale synthétisée

En effet, lors de l'analyse d'une puce Tx/Rx, l'erreur RMS de phase et d'amplitude correspondent à celles du core-chip. Il est donc justifié de réaliser une revue bibliographique sur les puces Tx/Rx entières. Nous avons regroupé dans le Tableau. 1.4 les performances des core-chips à l'état de l'art. Il est intéressant de noter l'absence de la technologie GaN dans le Tableau. 1.4, et dans la littérature. Il n'existe pas à notre connaissance de core-chip réalisé en GaN. Il est assez facilement compréhensible qu'il ne puisse pas concurrencer le SiGe en terme d'intégration et de coût. Cependant, vis à vis du GaAs, rien ne l'empêche de se positionner comme une alternative concurrente puisqu'au-delà des fonctions de contrôle, le GaN présente de meilleures performances en puissance que son vis-à-vis le GaAs. Dans la partie suivante nous nous intéresserons plus particulièrement à l'utilisation du GaN pour réaliser des fonctions de contrôle en vue d'une intégration totale des éléments d'une puce Tx/Rx.

# 7 La place du GaN dans les puces multifonctions

En analysant le Tableau. 1.4, on s'aperçoit de l'absence du GaN pour des réalisations de *core-chip* à l'état de l'art. Comme explicité plus tôt, le GaN génère un réel engouement dans le domaine de micro-ondes, pour des applications actives de puissances (*front-end*). En effet, comme nous l'avons évoqué précédemment, des composants « discrets » tels que des déphaseurs ou des atténuateurs [2]

| Référence            | [14]                     | [13]                | [31]              | [32]                     |

|----------------------|--------------------------|---------------------|-------------------|--------------------------|

| Technologie          | 0.13μm SiGe BiCMOS       | GaAs pHEMT          | GaAs pHEMT        | 0.13μm SiGe BiCMOS       |

| Fréquence (GHz)      | 30-40                    | 32-38               | 32-34             | 34-39                    |

| Erreur RMS Phase     | 4°                       | 3.8°                | 3°                | 12°                      |

| Erreur RMS Amplitude | 0.6dB                    | $0.7 \mathrm{dB}$   | $0.5 \mathrm{dB}$ | 0.9dB                    |

| Gain (dB)            | Rx :17 Tx :14            | Rx :9 Tx :11.5      | Rx :30 Tx :30     | Rx :-1 Tx :2             |

| Adaptation (dB)      | 9                        | 9                   | NC                | 8                        |

| Résolution Phase     | 11.25°                   | 11.25°              | NC                | 11.25°                   |

| Résolution Amplitude | Pas d'atténuateur        | 0.5dB               | NC                | Pas d'atténuateur        |

| Compacité            | 7mm <sup>2</sup>         | 12mm <sup>2</sup>   | NC                | $4 \mathrm{mm}^2$        |

| Consommation (W)     | Rx: 0.528 Tx: 1.587      | 0.15                | Rx : 0.6 Tx : 2.5 | Rx: 0.142 Tx: 0.171      |

| $P_{1dB}$ (dBm)      | Rx :-1 Tx :20.5 (sortie) | Rx:-3 Tx:0 (sortie) | NC                | Rx :-18 Tx :4.7 (sortie) |

Table 1.4 – Etat de l'art des core-chips en bande Ka

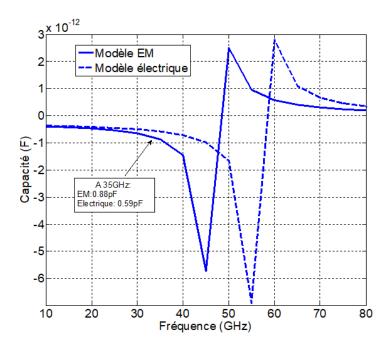

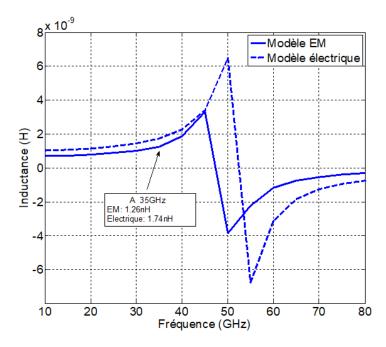

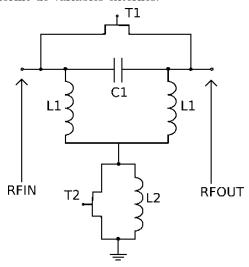

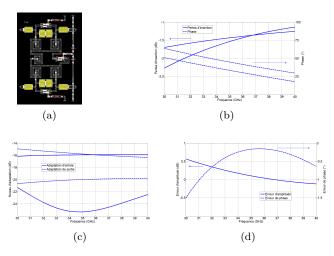

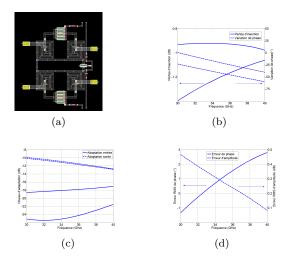

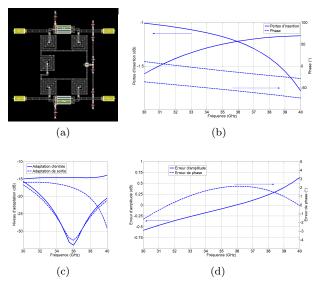

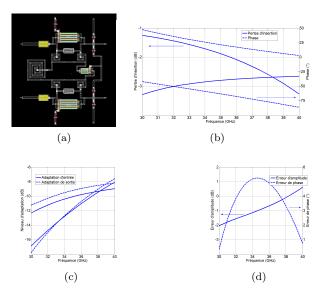

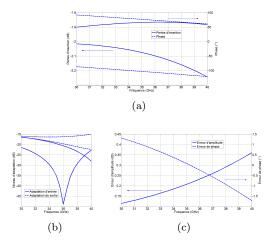

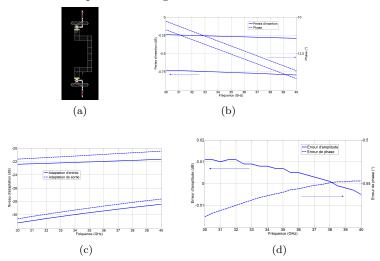

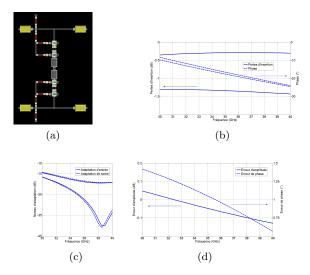

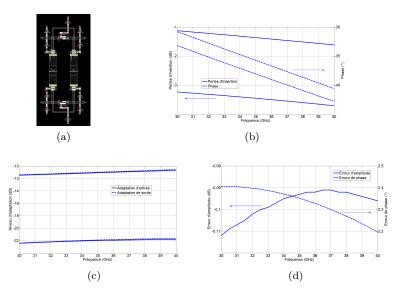

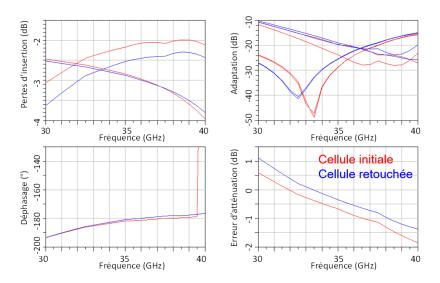

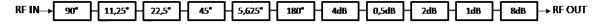

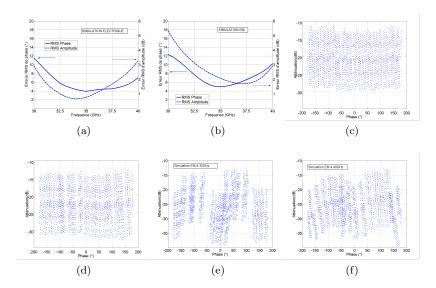

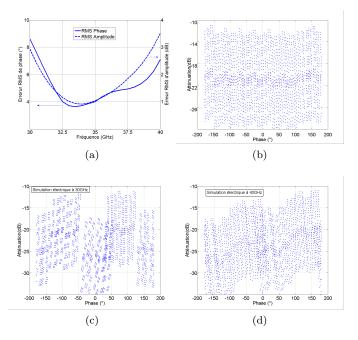

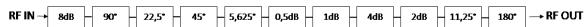

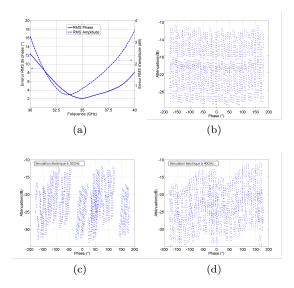

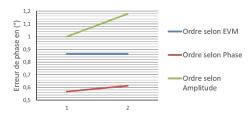

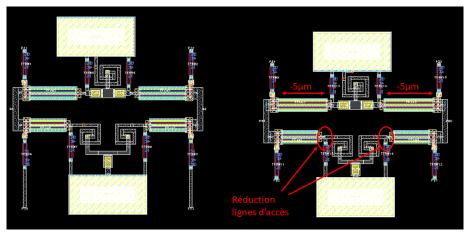

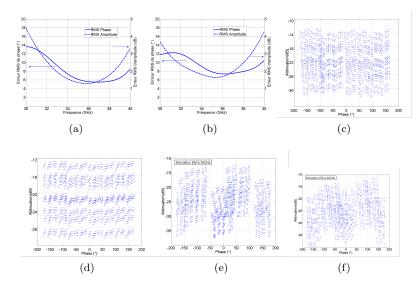

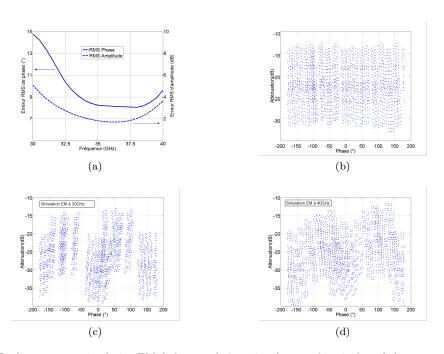

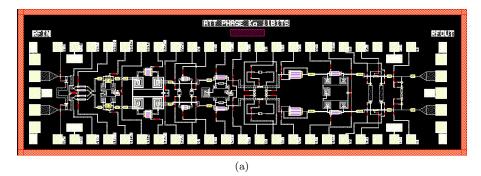

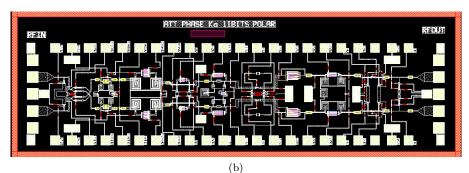

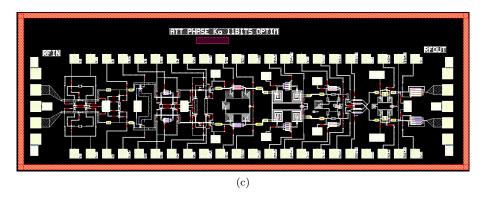

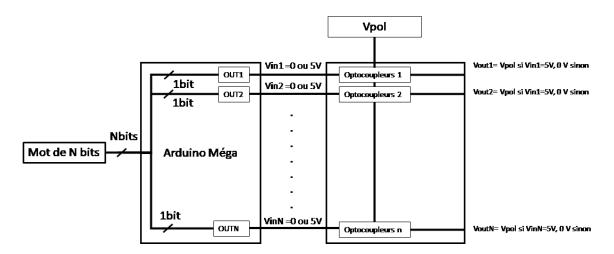

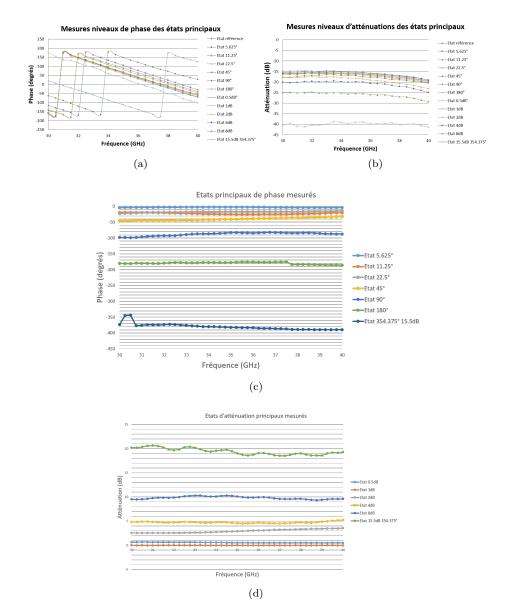

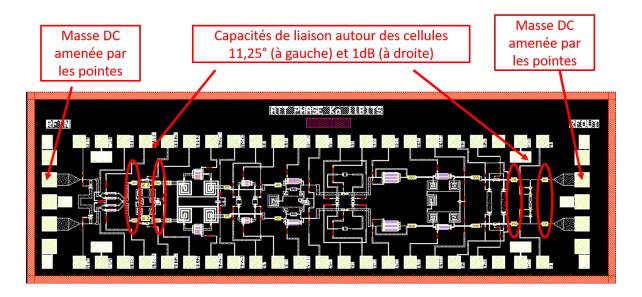

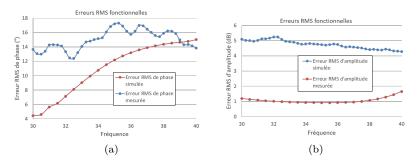

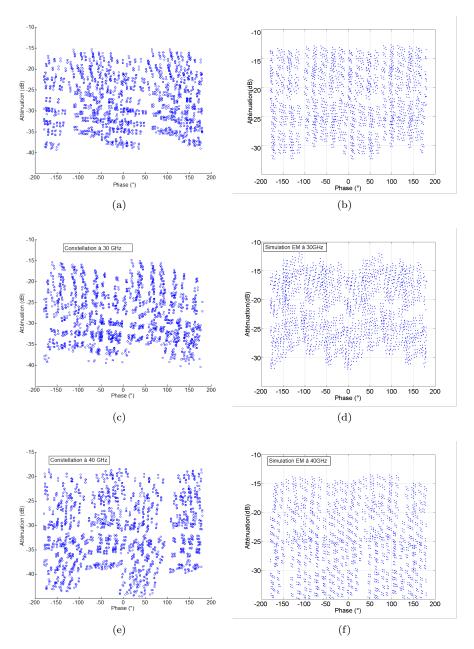

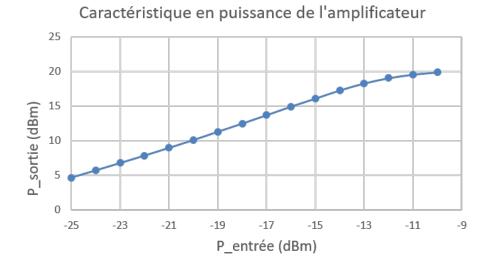

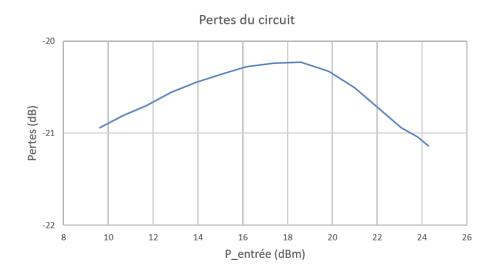

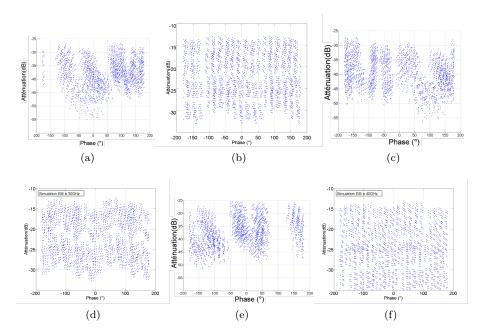

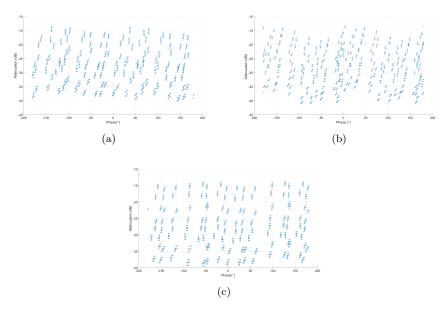

ont été réalisés individuellement. Cependant, il n'existe pas à notre connaissance de *core-chip* en GaN regroupant ces fonctions. Ce travail de thèse se positionne donc, à notre connaissance, comme un travail pionnier pour la réalisation de puce multi-fonctions en GaN.