## Qualité de protection des circuits intégrés contre les décharges électrostatiques

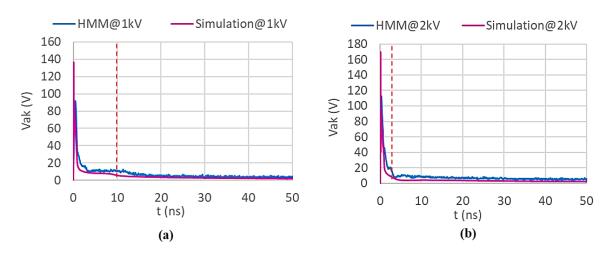

Mouna Mahane

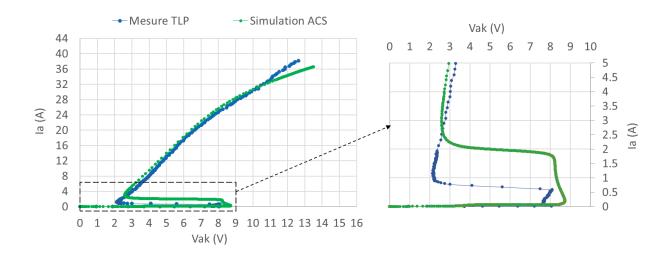

#### ▶ To cite this version:

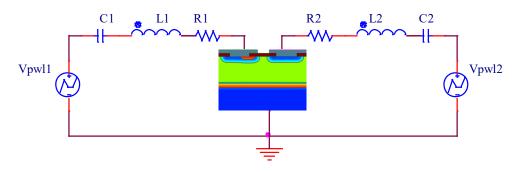

Mouna Mahane. Qualité de protection des circuits intégrés contre les décharges électrostatiques. Micro et nanotechnologies/Microélectronique. Université Toulouse 3 - Paul Sabatier, 2020. Français. NNT : . tel-03222666v1

## HAL Id: tel-03222666 https://laas.hal.science/tel-03222666v1

Submitted on 10 May 2021 (v1), last revised 23 Jun 2022 (v2)

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# **THÈSE**

## En vue de l'obtention du DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE

Délivré par l'Université Toulouse 3 - Paul Sabatier

## Présentée et soutenue par Mouna MAHANE

Le 10 décembre 2020

Qualité de protection des circuits intégrés contre les décharges électrostatiques

Ecole doctorale : **GEET - Génie Electrique Electronique et Télécommunications : du système au nanosystème**

Spécialité : Composants et Systèmes de gestion de l'Energie

Unité de recherche:

LAAS - Laboratoire d'Analyse et d'Architecture des Systèmes

Thèse dirigée par

#### **David TREMOUILLES**

Jury

M. Olivier LATRY, Rapporteur

M. Arnaud BOURNEL, Rapporteur

Mme Louise TRAVE-MASSUYES, Examinatrice

Mme Hélène FREMONT, Examinatrice

M. Frédéric MORANCHO, Examinateur

M. Fabrice ROQUETA, Examinateur

M. David TREMOUILLES, Directeur de thèse

M. Emilien BOUYSSOU, Encadrant industriel

Mme Marise BAFLEUR, Invitée

#### Résumé

Les travaux de cette thèse s'inscrivent dans un contexte concurrentiel, où les concepteurs de systèmes électroniques exigent que les solutions de protection contre les décharges électrostatiques (ESD) soient les plus performantes possibles. Dans ces travaux, les critères qui définissent la qualité de protection sont détaillés et de nouvelles méthodes de test sont développées. Nous exposons les critères associés à la conception d'un dispositif de protection complet (dimension, robustesse, efficacité et transparence). Une nouvelle approche de conception est donc proposée. Elle vise à adresser une large gamme d'applications en s'appuyant sur une technologie de protection « flexible ». L'idée est d'exploiter les compromis géométriques et technologiques existants, en se basant sur des outils d'apprentissage machine et de simulation physique. In fine, l'objectif est d'obtenir des pistes d'optimisation rapides, avec un maximum de flexibilité durant la phase de conception.

Mots-clés : Décharge électrostatique (ESD), qualité de protection, simulation physique, apprentissage machine.

\_\_\_\_\_\_

#### **Abstract**

This work has been done in a highly competitive context, where electronic-system designers require electrostatic discharge (ESD) protection devices providing high performance levels. The purpose of protection devices is to make circuits robust against ESD events, while being totally invisible to the system during normal operation. In this work, several aspects of ESD protection device are discussed, and new testing methods are proposed. An overview of design issues related to the several aspects of ESD protection is outlined. A new design approach is proposed which aims to address a large range of applications and is based on a «flexible» technology of protection. We achieve this challenge using machine learning tools and physical simulations to explore and yield profit from the existing compromises between designs and process parameters. The final goal is to allow maximum design flexibility, while providing guidance to easily adapt ESD protection to the targeted application-requirements.

Key words: Electrostatic discharge (ESD), quality of protection, physical simulation, machine learning.

## Remerciements

Ce travail de thèse s'inscrit dans le cadre d'une convention CIFRE subventionnée par l'Association Nationale de la Recherche Technique (ANRT), en collaboration entre le groupe d'Intégration de Systèmes de Gestion de l'Énergie (ISGE) au Laboratoire d'Architecture et d'Analyse des Systèmes (LAAS-CNRS) et la société STMicroelectronics.

A ce titre, je tiens à remercier Messieurs Jean Arlat et Liviu Nicu, directeurs successifs du LAAS-CNRS, ainsi que Monsieur Alain Cazarré et Madame Maria Pietrzak-David directeurs successifs de l'école doctorale GEET pour m'avoir accueillie au sein de leur unité de recherche.

Je tiens à remercier Patrick Galloy pour m'avoir permis d'effectuer mes travaux au sein de la société STMicroelectronics. J'adresse mes remerciements les plus sincères à Eric Bernier, directeur du département R&D, pour avoir accepté de m'accueillir dans son service, ainsi que pour son support et ses encouragements qui ont grandement contribué à l'aboutissement de ces travaux.

Je tiens à remercier les membres du jury pour le temps et l'attention portée à ce travail : merci à Monsieur Olivier Latry Professeur à l'université de Rouen et Monsieur Arnaud Bournel Professeur à l'université Paris-Sud qui, en qualité de rapporteurs, se sont impliqués dans la relecture et l'évaluation de ce mémoire. Merci aux examinatrices, Madame Louise Travé-Massuyès, directrice de recherche au LAAS-CNRS et Madame Hélène Frémont Professeur à l'université de Bordeaux pour l'intérêt qu'elles ont porté à ces travaux de recherche. Un grand merci à l'expert CAD Fabirce Roqueta, en sa qualité d'examinateur pour sa relecture méticuleuse et ses conseils avisés. Merci à Monsieur Frédéric Morancho Professeur à l'université Paul Sabatier de Toulouse, en sa qualité d'examinateur et de présidant du jury. Un grand merci également à Marise Bafleur qui a accepté de co-diriger cette thèse et qui, bien que partie à la retraite, m'a fait l'honneur de faire le déplacement pour assister à ma soutenance.

Je remercie infiniment mon directeur de thèse, David Trémouilles, qui par ses qualités pédagogiques, son champ de compétences et son questionnement curieux et pointilleux, a rendu ce travail de recherche agréable et passionnant. Je ne le remercierai jamais assez pour sa patience, sa bienveillance et la confiance qu'il a su m'accorder durant toutes ces années. Un grand merci également à Marianne Diatta et Emilien Bouyssou qui m'ont si bien accueillie dans l'équipe WLR, une première fois comme stagiaire et une seconde fois comme thésarde. Ils ont successivement assuré l'encadrement côté industriel et je les en remercie.

Je tiens à adresser un profond remerciement à Christine Anceau pour m'avoir acceptée dans son équipe à la fin de mon contrat CIFRE et pour son implication dans mon embauche au sein du laboratoire de caractérisation. Dans ce sens, je réitère mes remerciements à mon encadrant de thèse

Emilien Bouyssou qui m'a aidé à mettre en avant mon travail, ainsi qu'à mes collègues du laboratoire de Caractérisation qui m'ont chaleureusement accueillie.

Je pense aussi à mes collègues de STMicroelectronics qui ont participé à ces travaux de recherche. Je remercie en premier lieu Benjamin Thon, inventeur du banc "pulse-sweep", avec qui j'ai eu la chance de travailler et dont les compétences techniques et les qualités humaines ont beaucoup contribué à la réalisation de ce travail. Dans le même esprit, je remercie l'expert CAD, Lionel Jaouen pour sa disponibilité et son précieux support en simulation TCAD. Je remercie plus généralement toutes les personnes qui ont contribué de près ou de loin à l'orientation et à l'avancement de ces travaux : merci à Agnes Prunet pour l'animation des réunions projets, qui au fil du temps m'ont aidé à comprendre la problématique de développement des protections ESD. Je remercie également les experts de la R&D et en particulier Patrick Poveda pour ses critiques objectives, ainsi que Françoise Lauron pour toutes ses explications sur la codification et la gestion des lots. Je remercie également les designers, Denis Berthiot et Eric Laconde pour leur collaboration et pour m'avoir aidé à comprendre les contraintes inhérentes à la conception des circuits de protection. J'adresse un remerciement spécial à Denis Jurado pour son aide dans la relecture du manuscrit et j'élargis mes remerciements à tous mes collègues de la CAD, du Produit et de l'ASE, que j'ai pu côtoyer au cours de ma thèse et qui ont contribué à enrichir cette expérience. Un grand merci à mes collègues du marketing qui m'ont si chaleureusement accueillie dans leur service et dont je garderai un très bon souvenir.

J'en profite également pour remercier le personnel administratif de l'école doctorale GEET et de STMicroelectronics, en particulier Marie Estruga et Marie Pascale-Cavelier pour leur sympathie et leur réactivité. Je remercie également Bertrand Debuisne et Rodolphe Pillet pour leur support et leur efficacité.

Je remercie chaleureusement mes collègues du laboratoire de WLR et de Caractérisation avec qui j'ai eu le plaisir de travailler et de partager de bons moments au quotidien.

Une pensée aux stagiaires, doctorants et post-doctorants du groupe ISGE et de STMicroelectronics, que j'ai croisé au cours de ma thèse et avec qui j'ai eu la joie de discuter et d'échanger. Une pensée également pour mes amis de l'ENSA et du GSAT que j'ai eu le plaisir de revoir pendant la période de thèse et ce malgré la distance. J'en profite aussi pour remercier mon Professeur Monsieur Moulay Tayeb Belghiti qui a su nous inculquer sa passion pour la science et la recherche.

Enfin, je remercie très affectueusement ma famille et mes proches pour leur soutien inconditionnel et la confiance qu'il m'ont toujours témoignée.

Merci à toutes les personnes que j'aurais oubliées de citer et qui ont contribué de près ou de loin à ce travail.

## Table des matières

| Introduct | on générale                                                        | 9  |

|-----------|--------------------------------------------------------------------|----|

| Chapitre  | 1 Généralités sur les protections ESD                              | 11 |

| 1. Ty     | pe de perturbations et origines des ESD                            | 11 |

| 2. M      | odélisation des décharges ESD                                      | 14 |

| 2.1.      | Normes au niveau composant                                         | 15 |

| 2.2.      | Normes au niveau système                                           | 18 |

| 3. Ou     | tils de caractérisation ESD industriels                            | 25 |

| 3.1.      | Test TLP                                                           | 25 |

| 3.2.      | Test VF-TLP et corrélation avec les tests de qualification         | 27 |

| 4. Sta    | ratégies de protection ESD                                         | 28 |

| 4.1.      | Types de protections                                               | 28 |

| 4.2.      | Classification des protections                                     | 30 |

| 4.3.      | Caractéristiques électriques et composants de base des protections | 32 |

| 5. Qu     | alité de la protection ESD                                         | 38 |

| 5.1.      | Critères de qualité                                                | 38 |

| 5.2.      | Outils graphiques d'évaluation                                     | 40 |

| 6. Co     | nclusion                                                           | 42 |

| Chapitre  | 2 Qualité de protection du dispositif DTSCR                        | 45 |

| 1. De     | escriptif du dispositif de protection DTSCR                        | 45 |

| 1.1.      | Structure                                                          | 46 |

| 1.2.      | Principe de fonctionnement                                         | 47 |

| 1.3.      | Caractéristique Courant-Tension                                    | 48 |

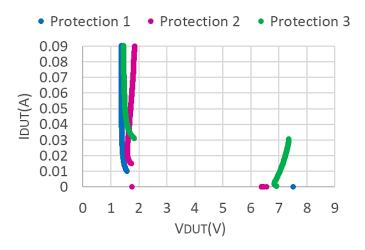

| 2. Ca     | ractéristiques électriques du DTSCR                                | 48 |

| 2.1.      | Enjeux industriels                                                 | 49 |

| 2.2.      | Point de maintien                                                  | 50 |

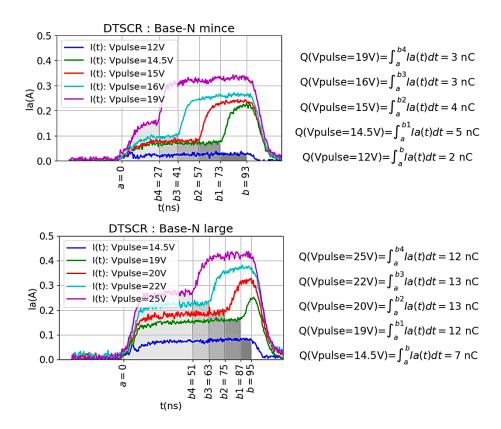

| 2.3.      | Rapidité et temps de déclenchement                                 | 66 |

| 3. Co     | empromis : Efficacité, Transparence et Robustesse                  | 78 |

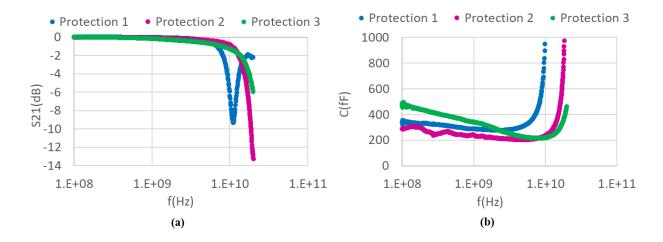

| 3.1.      | Transparence                                                       | 80 |

| 3.2.      | Efficacité                                                         | 81 |

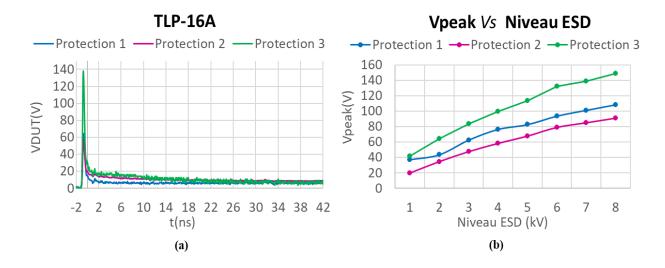

|    | 3          | .3.    | Robustesse                                                                         | 84   |

|----|------------|--------|------------------------------------------------------------------------------------|------|

|    | 3          | .4.    | Bilan                                                                              | 84   |

| 4  | ļ.         | Con    | npromis : Performances électriques et dessin technologique                         | 84   |

|    | 4          | .1.    | Structure                                                                          | 85   |

|    | 4          | .2.    | Performances électriques                                                           | 85   |

|    | 4          | .3.    | Bilan                                                                              | 86   |

| 5  | <i>.</i>   | Con    | nclusion                                                                           | 87   |

| Ch | api        | itre 3 | Prédiction de la qualité de la protection par la simulation physique               | 89   |

| 1  | . •        | Env    | rironnement de simulation                                                          | 89   |

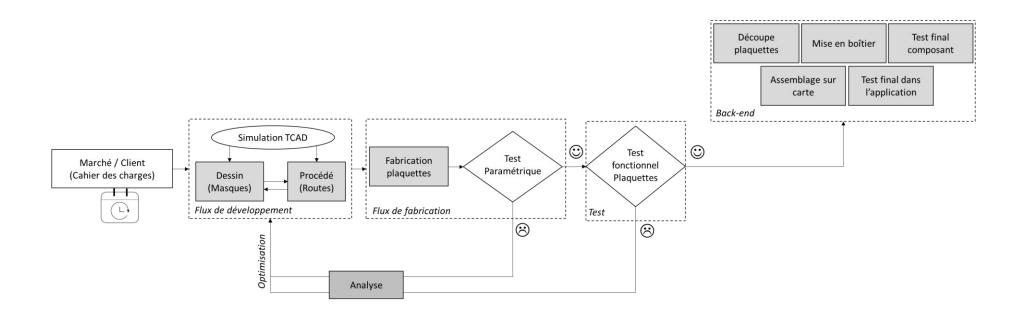

| 2  | 2.         | Dér    | oulement du projet                                                                 | 92   |

| 3  | 8.         | Gén    | nération de la structure de test                                                   | 93   |

|    | 3          | .1.    | Chargement du masque                                                               | 93   |

|    | 3          | .2.    | Description du procédé technologique                                               | 93   |

|    | 3          | .3.    | Simplification de la structure                                                     | 94   |

|    | 3          | .4.    | Maillage de la structure                                                           | 96   |

| 4  | ļ.         | Sim    | ulation électrique et électrothermique                                             | 98   |

|    | 4          | .1.    | Conditions aux limites                                                             | 98   |

|    | 4          | .2.    | Choix des modèles physiques                                                        | 98   |

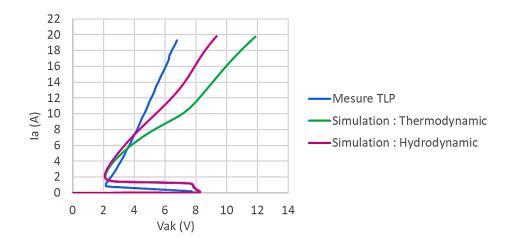

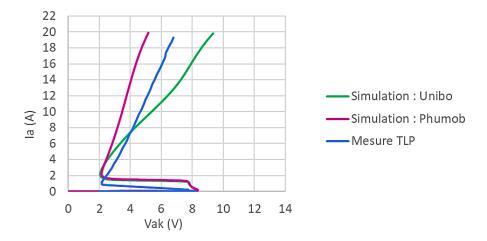

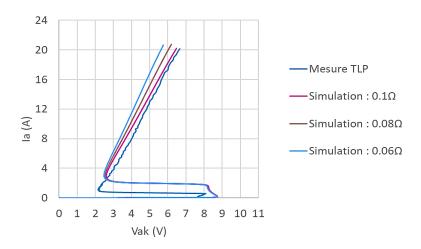

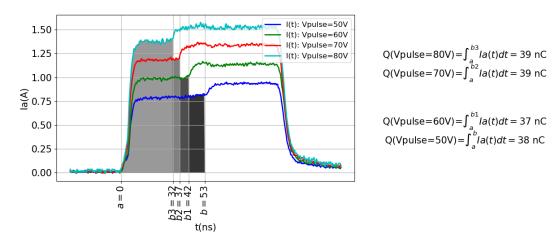

| 5  | j.         | Rés    | ultats et discussions                                                              | .100 |

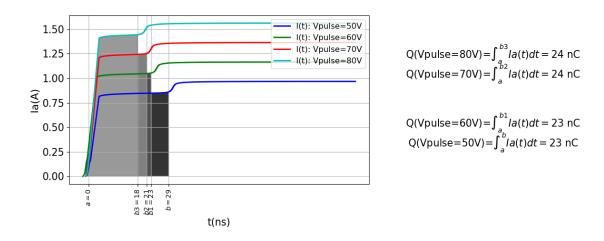

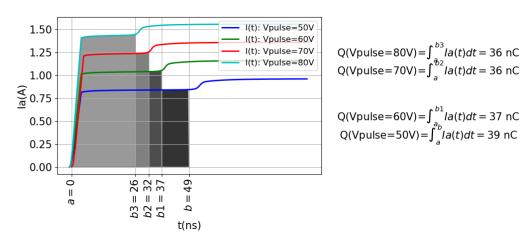

|    | 5          | .1.    | Prédiction de la transparence de la protection                                     | .101 |

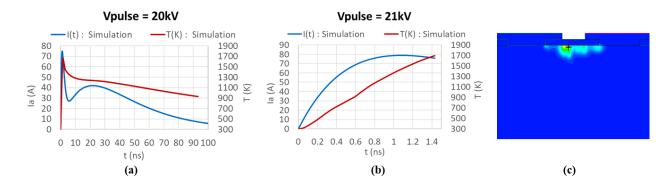

|    | 5          | .2.    | Prédiction de l'efficacité de la protection                                        | .106 |

|    | 5          | .3.    | Prédiction de la robustesse de la protection                                       | .120 |

| 6  | ).         | Bila   | nn des résultats                                                                   | .126 |

| 7  | <b>'</b> . | Cor    | nclusion                                                                           | .128 |

| Ch | api        | itre 4 | Prédiction et optimisation de la qualité de protection par l'apprentissage machine | .131 |

| 1  | . •        | Intr   | oduction à l'apprentissage automatique                                             | .131 |

| 2  | 2.         | Pro    | blématiqueblématique                                                               | .132 |

| 3  | 8.         | Obj    | ectif de l'étude                                                                   | .136 |

| 4  | <b>l.</b>  | Env    | rironnement de développement                                                       | .136 |

|    | 4          | .1.    | Outils de développement Python                                                     | .136 |

| 5  | ;          | Col    | lecte des données                                                                  | .137 |

| 5.1.        | Choix des motifs                                 | 138 |

|-------------|--------------------------------------------------|-----|

| 5.2.        | Choix des caractéristiques électriques de sortie | 139 |

| 5.3.        | Choix des paramètres physiques d'entrée          | 140 |

| 6. Pré      | traitement des données                           | 144 |

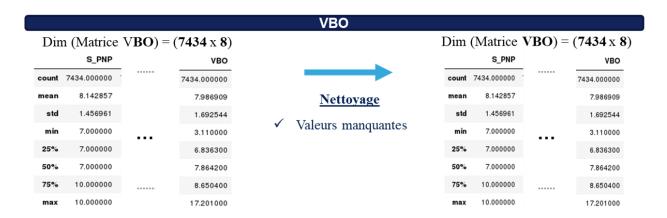

| 6.1.        | Jeu de données initial                           | 144 |

| 6.2.        | Nettoyage des données                            | 145 |

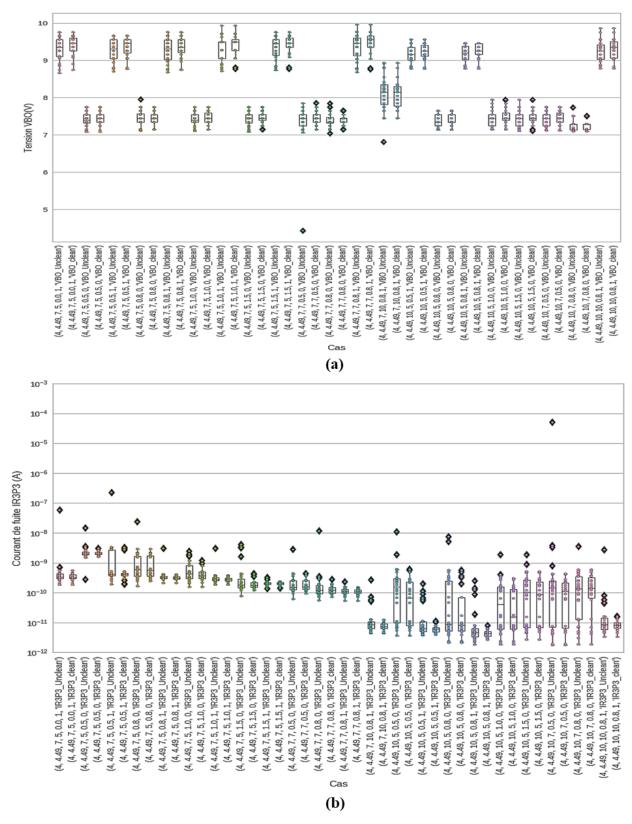

| 6.3.        | Données d'apprentissage et données de test       | 148 |

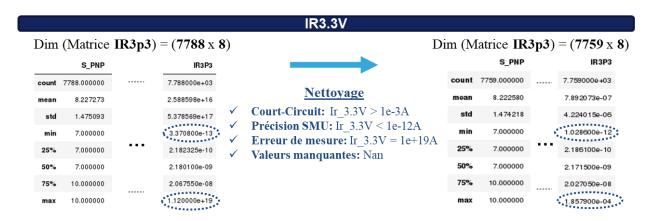

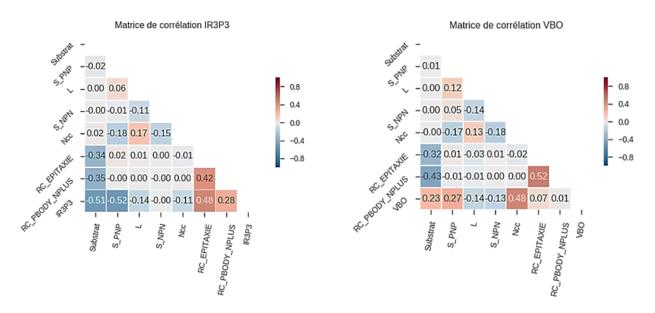

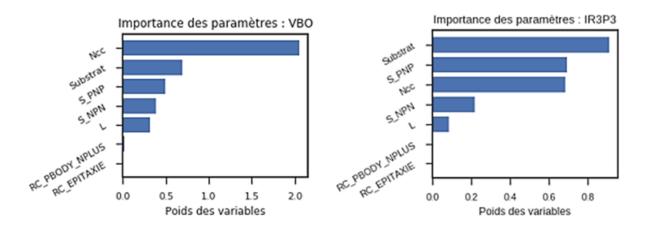

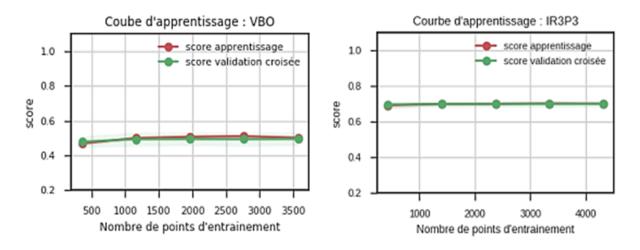

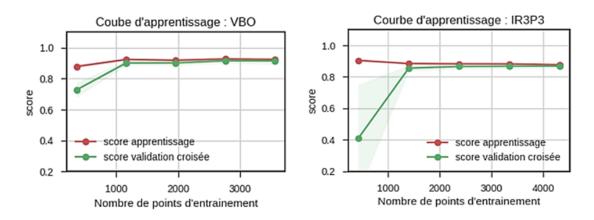

| 6.4.        | Visualisation des données                        | 149 |

| 7. Ch       | oix du modèle d'apprentissage                    | 150 |

| 7.1.        | Régression linéaire                              | 152 |

| 7.2.        | Régression polynomiale                           | 156 |

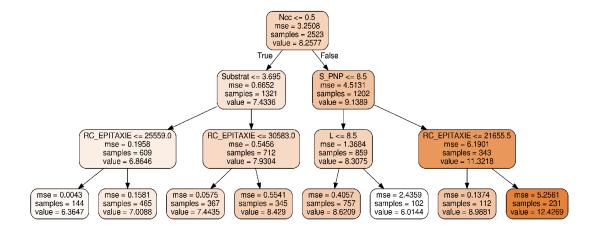

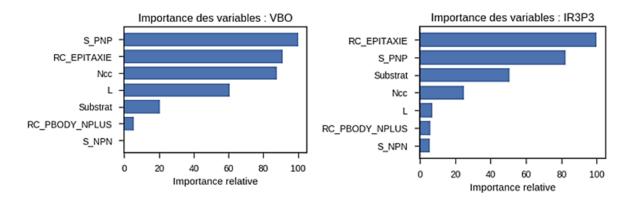

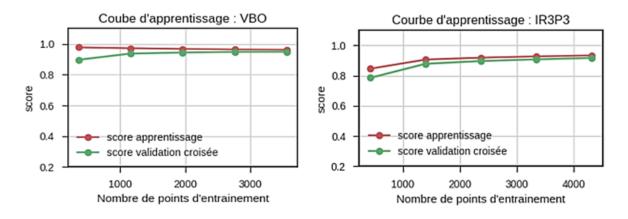

| 7.3.        | Forêts aléatoires                                | 158 |

| 8. Op       | timisation                                       | 164 |

| 8.1.        | Paramètres d'entrée avec contrainte              | 165 |

| 8.2.        | Définition de la fonction de coût                | 165 |

| 8.3.        | Algorithme d'optimisation                        | 166 |

| 9. Co       | nclusion et perspectives                         | 171 |

| Conclusio   | n générale                                       | 172 |

| Bibliograp  | ohie                                             | 175 |

| Liste des 1 | oublications                                     | 185 |

## Introduction générale

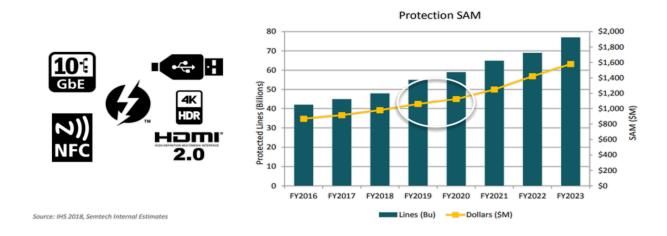

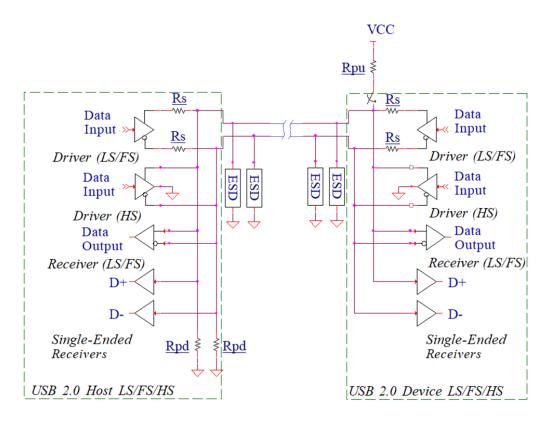

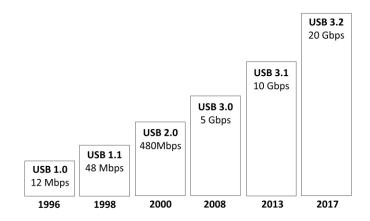

Le risque de décharges électrostatiques (ESD, *ElectroStatic Discharge*) est omniprésent tout au long du cycle de vie du composant. Pour protéger les systèmes électroniques des ESD, les concepteurs placent des protections dans les zones les plus exposées de leurs circuits. Ces protections servent à absorber les décharges et éviter qu'elles n'atteignent les circuits intégrés. Avec l'évolution numérique, les contraintes imposées aux protections discrètes sont de plus en plus nombreuses. En effet, avec le développement de l'internet des objets et des systèmes intelligents, les appareils électroniques sont de plus en plus connectés, le volume et le partage des données évoluent et la liste des fonctionnalités se rallonge d'année en année. A titre d'exemple, dans le marché de l'économie numérique, l'engouement autour du smartphone et l'évolution de ce dernier donnent une vision sur les nombreuses contraintes à considérer dans la conception des produits de protection. En effet, le smartphone intègre désormais de nombreuses fonctionnalités, comme l'internet mobile (4G, 5G ...), la géolocalisation (GPS), les applications multimédia, les communications courtes distance (NFC, Bluetooth...) et les applications de monétisation (RFID). Toutes ces fonctionnalités requièrent un débit de données plus important, une autonomie de batterie plus longue et un spectre de radiofréquences plus large. Au niveau système, cela se traduit par une multitude de puces et de circuits qui engendrent un encombrement plus conséquent. Pour réduire la complexité, le coût et l'encombrement du système, les concepteurs développent des circuits RF multistandards et des interfaces haut-débit universelles, qui assurent à la fois l'alimentation, l'échange de données et la transmission du flux audio et vidéo. Dans le contexte ESD, la tendance « nomade » de ce type d'appareils, associée à leurs nombreuses fonctionnalités, les rend particulièrement exposés aux décharges. En termes de qualité de protection, cela se traduit par des exigences ascendantes sur les performances de robustesse et d'efficacité. Face à cela, les limitations de l'encombrement requièrent une miniaturisation extrême des protections, avec des boîtiers réduits et des fonctionnalités bidirectionnelles et multilignes. D'un autre côté, les contraintes associées à la consommation d'énergie et à l'extensibilité du spectre de fréquences engendre une sensibilité accrue du système vis-à-vis des perturbations externes, ce qui exige une transparence maximale au niveau de la qualité de protection. A toutes ces considérations, se rajoutent celles du coût et des possibilités technologiques dont il faut tenir compte lors de la conception des produits de protection.

Dans ce contexte, il s'avère essentiel de repousser les limites technologiques des dispositifs de protection actuels, en proposant des solutions technologiques innovantes ou en améliorant les méthodologies de conception usuelles de manière à se recentrer sur la qualité de protection globale. Dans ces travaux de recherche, nous avons opté pour la seconde approche afin d'évaluer différentes pistes d'optimisation permettant d'améliorer les performances électriques d'un dispositif de protection de type *Diode Triggered Silicon Controlled Rectifier* (DTSCR). Le travail présenté dans ce manuscrit se divise en quatre chapitres :

Le premier chapitre présente un état de l'art des décharges électrostatiques et des moyens industriels mis en place pour les modéliser. Il décrit également les stratégies déployées dans la protection des circuits électroniques et précise sur les différents aspects qui définissent la qualité de la protection ESD.

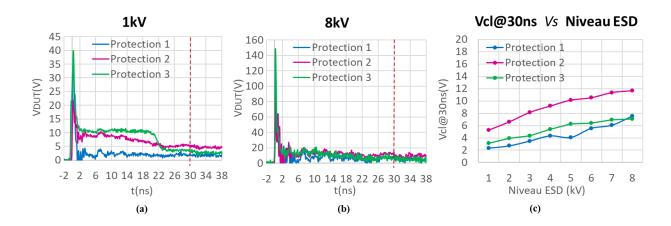

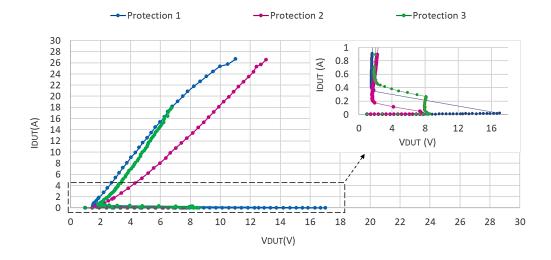

Le second chapitre se focalise sur l'étude de la qualité de protection pour une solution à retournement de type DTSCR. Une description de son mode de fonctionnement et de ses paramètres limitants y est détaillée et de nouvelles méthodes de tests sont proposées pour mieux les caractériser. Enfin, les résultats d'une étude comparative réalisée sur un échantillon de composants de protections illustrent les difficultés associées à la conception d'un produit optimal, à la fois en termes de transparence, de robustesse et d'efficacité.

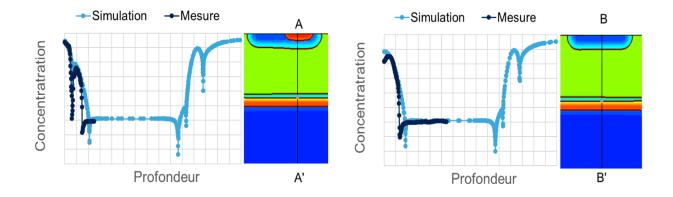

Le troisième chapitre s'inscrit dans une optique d'optimisation des performances électriques du DTSCR à l'aide de la simulation TCAD. On y décrit les méthodes déployées pour simuler les différents aspects de la qualité de protection ESD et la procédure d'étalonnage utilisée pour aboutir à un jumeau numérique du dispositif étudié. Les points forts et les limitations de cette approche sont donnés en conclusion.

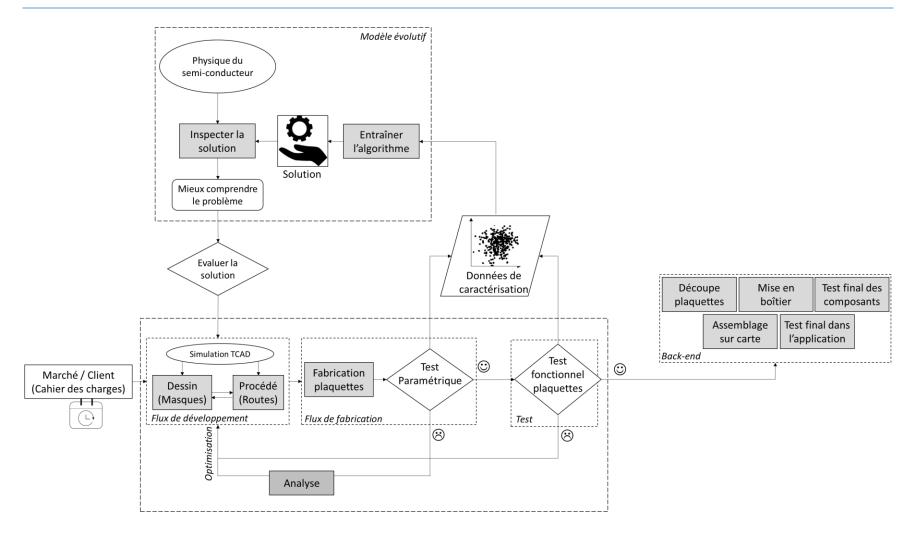

Le dernier chapitre s'inscrit également dans une approche d'optimisation du DTSCR, mais, cette fois-ci, en adoptant une nouvelle approche basée sur l'apprentissage machine. L'idée est de mettre à profit l'ensemble des connaissances acquises tout au long du développement de la technologie de protection. Pour cela, la démarche consiste à exploiter les différents compromis existants entre les paramètres géométriques et technologiques de la protection, afin d'aboutir à des solutions optimales adaptées au cahier des charges ciblé.

## Chapitre 1

## Généralités sur les protections ESD

Au quotidien, les décharges électrostatiques passent souvent inaperçues et se manifestent parfois sous la forme d'une étincelle ou d'un picotement ressenti par la personne impliquée. Dans l'industrie du semiconducteur, ces mêmes décharges peuvent endommager les composants électroniques et entraîner des coûts importants. Ce chapitre dresse un état de l'art sur l'origine des décharges électrostatiques (ESD) et les moyens de caractérisation mis en place pour l'analyse et la qualification des composants. Il s'ensuit une présentation des stratégies de protection mises en œuvre pour améliorer la robustesse des circuits électroniques. En dernière partie, une attention particulière est accordée aux différents aspects servants à définir la qualité d'un composant de protection.

#### 1. Type de perturbations et origines des ESD

Une ESD correspond à un transfert de charges entre deux corps ayant des potentiels électrostatiques différents. A grande échelle, le phénomène le plus connu est la foudre. A plus petite échelle, les décharges se manifestent sous la forme d'un arc électrique, comme lorsqu'une personne chargée touche la poignée d'une porte (figure 1.1).

Figure 1.1: L'ESD à l'échelle atmosphérique (foudre) [Adaptée de [DAN 90]], et l'ESD à l'échelle humaine (arc électrique)

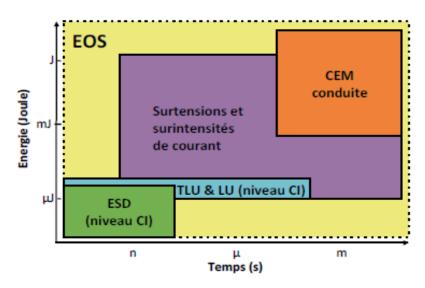

Dans la famille des surcharges électriques EOS (*Electrical Overstress*), les décharges électrostatiques sont les évènements les plus rapides et les moins énergétiques (figure 1.2). En microélectronique, il existe deux mécanismes majeurs à l'origine des ESD :

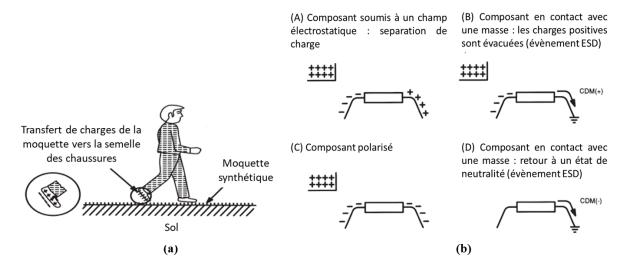

> Electrification par triboélectricité: un transfert de charges peut se produire lorsque deux matériaux différents sont mis en contact puis séparés. C'est le cas d'un composant qui glisse dans une barrette de transport, ou d'une personne qui accumule des charges en frottant ses chaussures contre le sol (figure 1.3-a).

Figure 1.2: Illustration des gammes de temps et d'énergie pour différentes surcharges électriques, EOS (Electrical overstress) [BAF 18]

> Electrification par induction : une séparation de charges se produit dans un objet électriquement neutre, soumis à l'influence du champ électrique émis par un objet chargé, se trouvant à proximité. C'est le cas par exemple lorsqu'un papier ou un gobelet en polystyrène sont chargés électriquement et placés à proximité d'un composant (figure 1.3-b) [BAF 18].

Figure 1.3: Electrification par triboélectricité [Adaptée d'après [DAN 90]] (a), électrification par induction [Adaptée d'après [VIN 98]] (b)

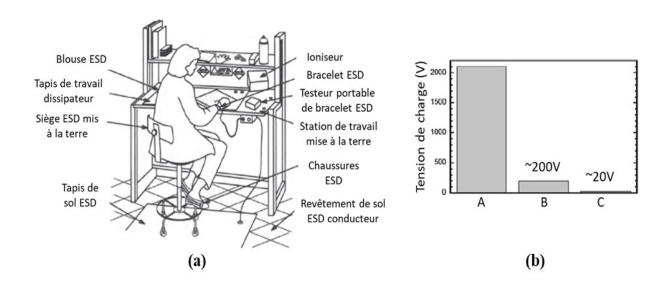

Le risque d'ESD étant omniprésent tout au long du cycle de vie du composant, différentes approches ont été développées pour s'en prémunir. La première consiste à réduire le risque dans les lignes de fabrication. Cela se traduit par la mise en place de zones dites EPA (ESD Protected Area), où plusieurs précautions sont prises pour minimiser la génération et l'accumulation de charges (figure 1.4). La seconde approche consiste à accroître la robustesse des circuits électroniques en y intégrant des protections, ainsi ils deviennent moins sensibles aux décharges électrostatiques. Dès lors, pour évaluer la vulnérabilité des circuits face à ce type de perturbations, plusieurs modèles ont été développés pour reproduire les décharges électrostatiques en laboratoire.

Figure 1.4: (a): zone de protection ESD [Adaptée d'après [DAN 90]], et (b): impact des différentes méthodes de contrôle ESD sur la tension de charge d'une personne dans un environnement industriel: sans contrôle ESD (A), avec un revêtement de sol ESD (B), et avec des chaussures ESD (C) [Adaptée d'après [VAS 14]]

#### 2. Modélisation des décharges ESD

Les modèles de décharges électrostatiques servent à reproduire les perturbations rencontrées par le composant dans son environnement de fabrication ou d'utilisation. Chaque modèle se caractérise par une forme d'onde de courant spécifique, dont les caractéristiques sont décrites dans des documents normatifs, définis par plusieurs comités dont les principaux sont : JEDEC (*Join Electron Device Engineering Council*), l'IEC (*International Electrotechnical Commission*), l'ANSI/ESD (*American National Standards Institute*) et MIL-STD (*United States Military Standard*).

La partie qui suit liste les principaux modèles de décharges utilisés pour définir la robustesse des protections dans les documentations techniques. Ces modèles sont listés et groupés selon deux catégories :

- Les tests destructifs qui obéissent à des normes bien définies et qui sont déployés dans la qualification des composants et des systèmes dans les domaines ESD et EOS.

- Les tests de caractérisation alternatifs qui sont moins bien normés et communément utilisés pour comprendre le fonctionnement des protections face à des décharges ESD.

#### 2.1. Normes au niveau composant

#### 2.1.1. Modèle d'une personne chargée (HBM)

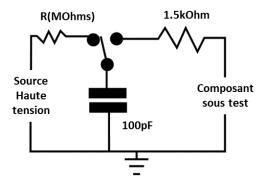

Le modèle HBM (*Human Body Model*) simule la décharge d'une personne électriquement chargée lorsqu'elle touche du doigt un composant électronique connecté à la masse. Le testeur HBM s'apparente à un circuit RLC, composé d'une capacité de 100 pF en série avec une résistance de  $1.5 \text{ k}\Omega$  (figure 1.5).

Figure 1.5: Schéma électrique du modèle de test HBM [Adaptée d'après [ESD 10]]

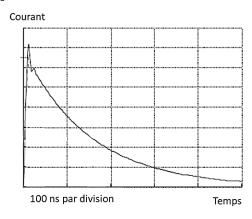

La figure 1.6 illustre une forme d'onde HBM standard. Elle se caractérise par un temps de montée allant de 2 ns à 10 ns, suivit d'une décroissance exponentielle du courant qui s'étend sur une centaine de nanosecondes. L'amplitude du courant varie en fonction de la tension de précharge appliquée. Pour la qualification d'un composant électronique, les niveaux de tenue HBM généralement requis pour immuniser les composants électroniques lors des étapes de fabrication sont de 1 kV à 2 kV [ESD 16].

Figure 1.6: Forme d'onde typique du courant de décharge HBM sur un court-circuit [Adaptée d'après [ANS 14]]

#### 2.1.2. Modèle d'un équipement chargé (MM)

Le modèle MM (*Machine Model*) reproduit la décharge d'une machine électriquement chargée qui vient au contact d'un composant électronique relié à la masse. Son schéma électrique est un circuit RLC comparable à celui du modèle HBM. Sa forme d'onde est caractérisée par des oscillations sinusoïdales qui montrent un amortissement dans le temps. Toutefois, cette forme d'onde dépend fortement de l'équipement, ce qui pose un problème de reproductibilité d'un testeur à l'autre et rend la qualification difficile et le test MM de plus en plus obsolète [IND 10].

#### 2.1.3. Modèle d'un composant chargé (CDM)

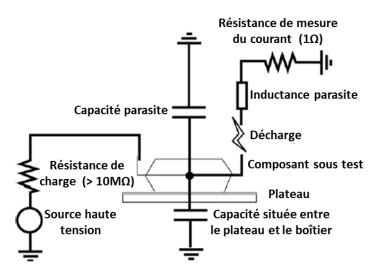

Le modèle CDM (*Charged Device Model*) simule la décharge d'un composant au contact d'un objet ou d'une surface connectée à la masse. Contrairement aux tests MM et HBM où le stress est initié par une source externe, le stress CDM résulte du composant lui-même. Ce dernier accumule des charges par induction ou frottement lors des différentes étapes de fabrication, de stockage et de transport. La décharge du composant est modélisée par un circuit RLC dont les valeurs sont faibles et fortement dépendantes du type de boîtier, de ses dimensions, du chemin de décharge et des conditions de test (figure 1.7) [GOE 05] [SAL 05].

Figure 1.7: Schéma électrique du modèle de test CDM [Adaptée d'après [ESD 10]]

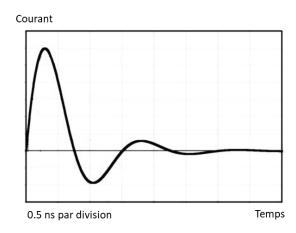

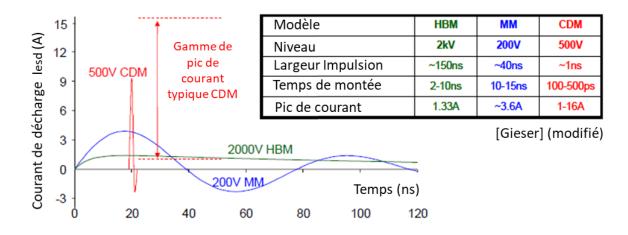

La forme d'onde associée au test CDM est illustrée dans la figure 1.8. Elle se caractérise par des oscillations fortement amorties, avec un temps de montée très court et un pic de courant très important (une dizaine d'ampères).

Figure 1.8: Forme d'onde typique du courant de décharge CDM [Adaptée d'après [ANS 18]]

Comparé aux tests HBM et MM, le stress CDM est moins énergétique, avec une signature de défaillance qui se traduit principalement par un claquage des diélectriques (figure 1.9).

Figure 1.9: Comparaison des allures des formes d'ondes en courant de décharge HBM (2 kV), CDM (500 V) et MM (200 V) [IND 09]

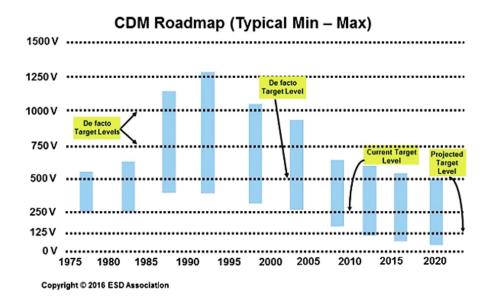

Pour la qualification des composants électroniques, le niveau de tenue CDM minimum généralement recommandé est de 250V [ESD 16] (figure 1.10). Toutefois, les spécifications des industriels ne font pas état des tests CDM de manière systématique, étant donné la complexité de ces mesures et des coûts associés [GUI 02].

Figure 1.10: Evolution du niveau de tenue CDM des composants électroniques [ESD 16]

#### 2.2. Normes au niveau système

Dans les sous-sections suivantes nous allons décrire les normes : IEC61000-4-2, HMM et IEC61000-4-5.

#### 2.2.1. Modèle IEC61000-4-2

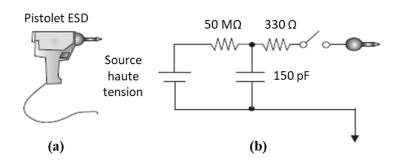

Le modèle IEC61000-4-2 simule la décharge d'une personne dans un système à travers un objet métallique. Cette décharge est reproduite avec un pistolet ESD, composé d'une source haute tension qui charge une capacité de 150 pF à travers une résistance de plusieurs megaohms. Cette capacité se décharge ensuite par l'intermédiaire d'un relais à travers une résistance de 330  $\Omega$  (figure 1.11).

Figure 1.11: Pistolet IEC61000-4-2 (a), et schéma électrique équivalent (b) [Adaptée d'après [VOL 16]]

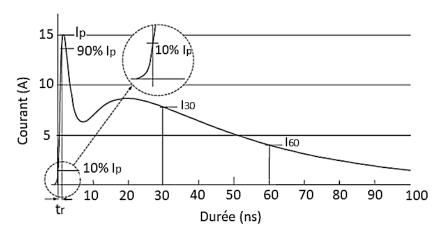

La norme IEC61000-4-2 spécifie la forme d'onde standard à respecter (figure 1.12 – tableau 1.1). Celle-ci se caractérise par deux pics de courant successifs. Le premier peut atteindre une dizaine d'ampères, avec un temps de montée très court (≤1 ns). Il est souvent à l'origine des claquages d'oxyde dans les circuits intégrés [VAS 14]. Le second est relevé à 30 ns, il s'étale sur une dizaine de nanosecondes, avec un niveau de courant plus bas et une quantité d'énergie plus importante. Pour protéger efficacement un système électronique contre ce type de décharges, le dispositif de protection doit s'amorcer très rapidement pour écrêter le premier pic, tout en ayant le niveau de robustesse requis pour supporter la quantité d'énergie injectée par le second pic, qui correspond aux niveaux de tension ciblés.

Figure 1.12: Forme d'onde du courant de décharge IEC61000-4-2 au contact à 4 kV dans une impédance équivalente à 2  $\Omega$  [Adaptée d'après [IEC 08]]

| Tension de charge (kV) | Courant 1 <sup>er</sup> pic<br>Ip ±15 % (A) | Temps de montée<br>tr ±25 % (ns) | Courant à 30 ns<br>I30 ±30 % (A) | Courant à 60 ns<br>I60 ±30 % (A) |

|------------------------|---------------------------------------------|----------------------------------|----------------------------------|----------------------------------|

| 2                      | 7,5                                         | ,                                | 4                                | 2                                |

| 4                      | 15                                          | 0.0                              | 8                                | 4                                |

| 6                      | 22,5                                        | 0,8                              | 12                               | 6                                |

| 8                      | 30                                          |                                  | 16                               | 8                                |

Tableau 1.1: Paramètre de la forme d'onde de courant de décharge IEC61000-4-2 au contact [Adaptée d'après [IEC 08]]

La robustesse exigée par la norme IEC61000-4-2 est répertoriée selon quatre niveaux décrits dans le tableau 1.2. Ces niveaux sont différents selon la méthode de test appliquée : « en contact » ou

« dans l'air » (figure 1.13). Les deux méthodes donnent généralement une robustesse similaire, voire supérieure lorsqu'il s'agit de décharges « dans l'air » [NEX 18].

Figure 1.13: Exemple de décharges au pistolet ESD : au contact (a) et dans l'air (b) [VAS 14]

| Niveaux<br>ESD | Tension de décharge<br>IEC61000-4-2 au contact<br>(kV) | Tension de décharge<br>IEC61000-4-2 dans l'air<br>(kV) |

|----------------|--------------------------------------------------------|--------------------------------------------------------|

| 1              | 2                                                      | 2                                                      |

| 2              | 4                                                      | 4                                                      |

| 3              | 6                                                      | 8                                                      |

| 4              | 8                                                      | 15                                                     |

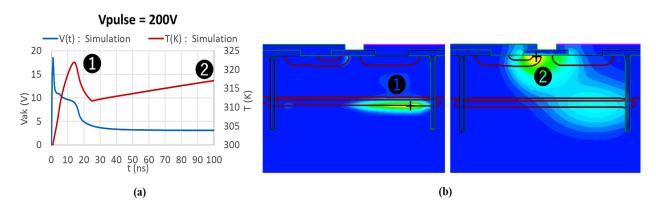

Tableau 1.2: Niveaux de conformité ESD selon la norme IEC61000-4-2

Pour produire des résultats répétables, la norme IEC61000-4-2 spécifie les équipements, les procédures d'étalonnage et les conditions de tests à respecter. Toutefois, ces spécifications concernent uniquement les tests appliqués au système, or la demande des concepteurs se focalise désormais sur le test du composant lui-même, l'idée étant que sa robustesse est garante de la tenue du système qu'il protège. Pour standardiser le test des composants en configuration système, une nouvelle norme appelée HMM a été mise en place par l'association ESDA [ANS 09].

#### 2.2.2. Modèle HMM

Le modèle HMM (*Human Metal Model*) permet d'appliquer une décharge système de type IEC61000-4-2 directement au niveau du composant. A l'origine, la norme IEC ne concerne que les

mesures système. Or la nécessité d'effectuer ces caractérisations sur des produits discrets a poussé les industriels à développer leurs propres solutions de test, en se basant sur des boîtiers et des cartes spécifiques, l'objectif étant de garantir la conformité de l'onde IEC au plus près du composant [ANS 09] (figure 1.14).

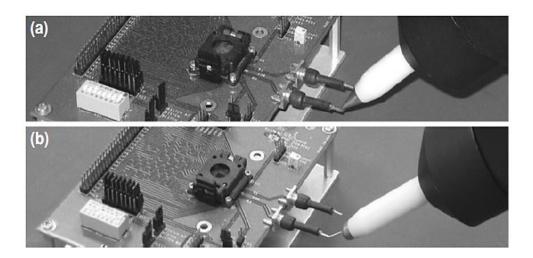

Figure 1.14: Mesure IEC61000-4-2 au niveau composant

La complexité de ce type d'approche et son manque de reproductibilité a nécessité la mise en place d'un standard HMM qui normalise la procédure de test et facilite son application aux composants discrets. Deux configurations de test HMM sont envisageables :

#### 2.2.2.1. <u>Configuration HMM avec pistolet ESD</u>

Cette approche consiste à utiliser un pistolet ESD conformément aux spécifications IEC61000-4-2. Dans cette approche, la pointe du pistolet vient au contact d'un point de décharge du circuit imprimé sur lequel se trouve le composant à tester. L'ensemble est monté sur une plaque métallique horizontale, connectée au retour de masse du pistolet [VAS 14] (figure 1.15). L'autre approche consiste à réaliser le montage HMM avec une plaque métallique verticale qui fait office de bouclier contre les perturbations électromagnétiques émises par le pistolet pendant la décharge ESD [VAS 14] [BAF 18].

Figure 1.15: Configurations de test HMM avec pistolet ESD : simplifiée (a) et verticale (b) [Adaptée de [ANS 09]]

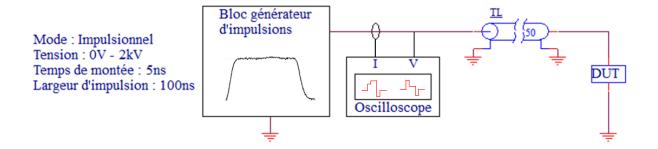

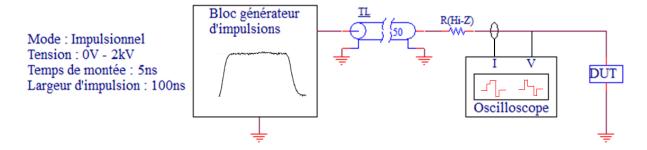

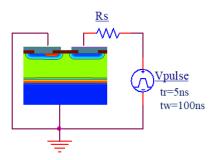

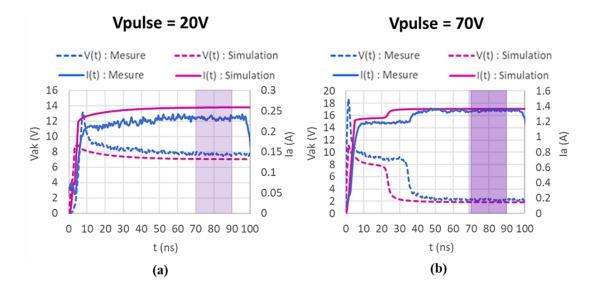

#### 2.2.2.2. <u>Configuration HMM adaptée 50 Ω</u>

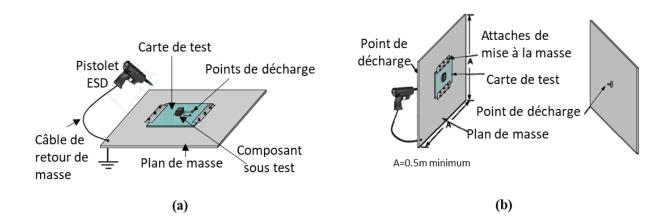

Dans cette configuration, le pistolet ESD est remplacé par un générateur d'impulsion, d'impédance 50  $\Omega$  de type TLP (figure 1.16-a). Il s'agit d'une alternative de test qui permet d'améliorer la reproductibilité des mesures, tout en s'affranchissant des radiations électromagnétiques du pistolet ESD. Elle offre également la possibilité de réaliser des mesures sous-pointes pour évaluer la robustesse des composants durant la phase de conception. Le problème des testeurs « HMM-50 $\Omega$  » réside dans les phénomènes de réflexion résultant de la désadaptation d'impédance liée à la charge. Ces réflexions peuvent être à l'origine de perturbations au niveau du générateur d'impulsions, ce qui peut mener à une divergence de résultats par rapport au pistolet ESD (figure 1.16-c) [VAS 14]. Les testeurs type « HMM-IEC » se basent sur un circuit de décharge type IEC61000-4-2 avec une impédance de 330  $\Omega$  similaire à celle du pistolet ESD (figure 1.16-b) [VAS 14]. Les tests HMM s'effectuent alors aussi bien sous pointes qu'en boîtier.

Figure 1.16: Schéma de principe du testeur HMM-50 $\Omega$  (a) et HMM-IEC (b) pour une configuration de test sous-pointes. Comparaison des formes d'ondes en courant sur un court-circuit, pour un niveau de décharge HMM équivalent de 1 kV (c) [Adaptée de [VAS 14]]

La robustesse exigée par la norme HMM est répertoriée selon quatre niveaux décrits dans le tableau 1.3.

| Niveaux HMM | Tension de décharge IEC61000-4-2 équivalente (kV) |

|-------------|---------------------------------------------------|

| I           | 1                                                 |

| II          | 2                                                 |

| III         | 4                                                 |

| IV          | 6                                                 |

| V           | 8                                                 |

| X           | Spécial                                           |

Tableau 1.3: Niveaux de conformité ESD selon la norme HMM [Adaptée de [ANS 09]]

#### 2.2.3. Modèle IEC61000-4-5 (Norme EOS)

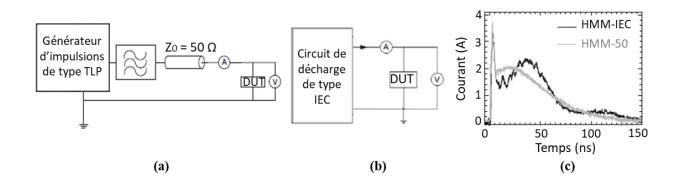

Le modèle IEC61000-4-5 reproduit des surcharges électriques plus lentes et plus énergétiques que les décharges IEC61000-4-2. Ces surcharges sont attribuées à des phénomènes transitoires comme les surtensions dans le système d'alimentation, qui résultent de défauts de court-circuit, de commutations ou de variations de charges. Le circuit permettant de modéliser les décharges IEC61000-4-5 est composé d'une source haute tension qui charge une capacité Cc à travers une résistance  $R_C$ . Cette capacité se décharge ensuite à travers un circuit  $R_L$  composé d'une résistance d'adaptation d'impédance  $R_m$ , une résistance  $R_S$  et une inductance  $L_r$  qui contrôlent respectivement la durée et le temps de montée de la forme d'onde générée [VAS 14] (figure 1.17).

U : Source haute tension

Re: Résistance de charge

Cc: Condensateur de stockage d'énergie

Rs: Résistance déterminant la durée de l'impulsion

Rm: Résistance d'adaptation d'impédance

Lr : Inductance déterminant le temps de montée

Figure 1.17: Schéma de principe simplifié du circuit du générateur d'ondes IEC61000-4-5 [Adaptée de [IEC 17]]

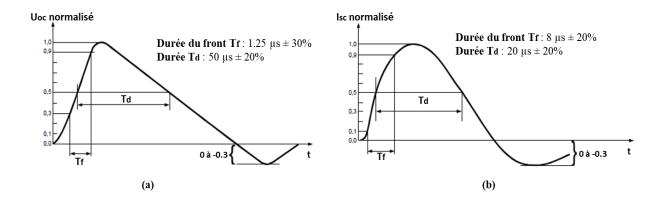

La forme d'onde générée par le circuit IEC61000-4-5 est illustrée dans la figure 1.18 en régime faible impédance et forte impédance (configurations court-circuit et circuit-ouvert). La durée et le temps de montée de la forme d'onde résultante sont respectivement de 8/20 µs et 1.2/50 µs, avec un pic de courant pouvant aller de 250 A à 2 kA [VAS 14].

Figure 1.18: Formes d'onde de tension en circuit ouvert (1.2/50 μs) (a), et forme d'onde du courant de court-circuit (8/20 μs) (b) [Adaptée de [IEC 17]]

La robustesse exigée par la norme IEC61000-4-5 est répertoriée selon quatre niveaux décrits dans le tableau 1.4

| Classe | Environnement                                                                                                                                                                                                                          | Niveau de tension   |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 0      | Environnement électrique bien protégé, souvent celui d'une salle spéciale.                                                                                                                                                             | 25 V                |

| 1      | Environnement électrique partiellement protégé                                                                                                                                                                                         | 500 V               |

| 2      | Environnement électrique pour lequel les câbles sont bien séparés, même sur des parcours de faible longueur.                                                                                                                           | 1 kV                |

| 3      | Environnement électrique pour lequel le parcours des câbles est parallèle.                                                                                                                                                             | 2 kV                |

| 4      | Environnement électrique pour lequel les interconnexions se font par des câbles extérieurs, à côté des câbles d'énergie et pour lequel les câbles sont utilisés à la fois pour des circuits électroniques et des circuits électriques. | 4 kV                |

| 5      | Environnement électrique pour du matériel électronique relié à des câbles de télécommunications et à des lignes électriques aériennes d'une zone qui n'est pas très peuplée.                                                           | Niveau<br>d'essai 4 |

| X      | Conditions particulières stipulées dans les spécifications de produit.                                                                                                                                                                 | -                   |

Tableau 1.4: Classification et niveaux de tension correspondants selon la norme IEC61000-4-5 [Adaptée d'après [IEC 17] [STM 13]]

#### 3. Outils de caractérisation ESD industriels

Dans les sous-sections suivantes nous allons décrire les outils de caractérisation déployés dans l'étude du fonctionnement des produits de protection : TLP et VF-TLP.

#### 3.1.Test TLP

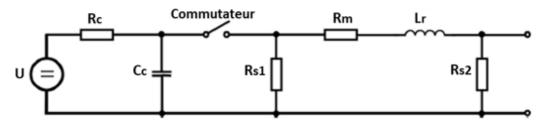

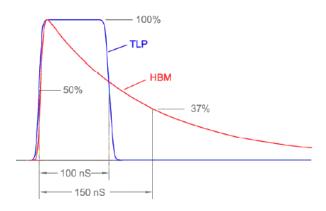

Les tests ESD comme l'HBM et le CDM sont des tests destructifs de type « go / no go ». Ils servent dans la qualification et l'évaluation de la robustesse d'un composant électronique. Pour autant, ces tests ne permettent pas d'analyser le comportement du composant face à des décharges ESD. Or l'étude des mécanismes qui gèrent son fonctionnement en régime fort courant peut s'avérer nécessaire dans la conception et l'optimisation des solutions de protection. Pour remédier à cette limitation, le test TLP (*transmission line pulse*) applique des impulsions carrées dont l'énergie est comparable à celle d'une décharge HBM (figure 1.19). Le caractère « quasi-statique » des tests TLP se traduit par une durée d'impulsion limitée, à la fois courte pour éviter les phénomènes d'échauffement et suffisamment longue pour permettre une stabilisation des courants-tensions dans le composant.

Figure 1.19: Comparaison des formes d'onde TLP et HBM [BAR 15]

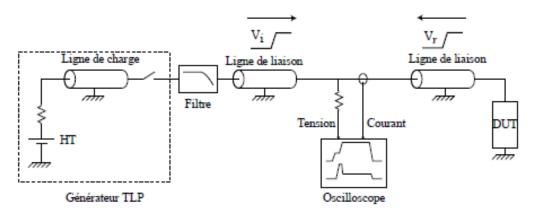

Le schéma de principe du banc TLP est illustré dans la figure 1.20. Le testeur est composé d'une ligne de transmission  $50~\Omega$ , qui se charge via une alimentation haute tension. La fermeture du relais permet de décharger la ligne de transmission dans le composant de test. La durée de l'impulsion et son temps de montée sont ajustés via la longueur du câble coaxial et un filtre passe-bas. La propagation de l'impulsion le long des lignes de transmission entraîne des phénomènes de réflexion, qui dépendent de la variation d'impédance du composant au bout de la ligne. Un oscilloscope permet la mesure simultanée de l'onde incidente et réfléchie. La superposition des deux permet d'obtenir les réponses en tension et en courant du composant.

Figure 1.20: Schéma de principe du testeur TLP [BAF 18]

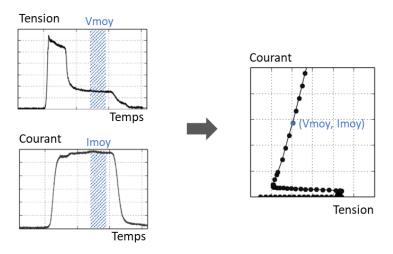

La procédure de test TLP consiste à appliquer une succession d'impulsions carrées, décorrélées les unes des autres et d'amplitude croissante. La durée d'une impulsion standard est de 100 ns avec un temps de montée variable, allant de 300 ps à 10 ns. A chaque impulsion TLP, les réponses en

tension et en courant sont moyennées dans la partie stable des courbes, suivant une fenêtre de temps prédéfinie (figure 1.21). Les moyennes des courants et tensions obtenues permettent de tracer point par point la caractéristique I-V du composant. Celle-ci est associée à une mesure de courant de fuite à la fin de chaque impulsion TLP, pour vérifier l'état de dégradation du composant.

Figure 1.21: Reconstruction point par point de la caractéristique I-V quasi-statique, à partir des formes d'ondes dynamiques en courant et en tension

#### 3.2. Test VF-TLP et corrélation avec les tests de qualification

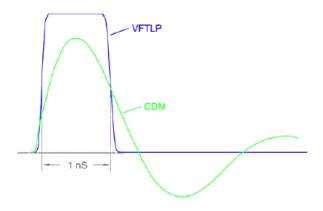

Le VF-TLP (*Very Fast TLP*) est un outil de caractérisation qui vise à étudier le comportement des composants face à des perturbations rapides comme le CDM. Pour ce faire, les impulsions appliquées sont de courtes durées, avec un temps de montée d'une centaine de picosecondes (figure 1.22).

Figure 1.22: Comparaison des formes d'onde VF-TLP et CDM [BAR 15]

Pour générer ce type impulsions, le testeur se base sur un montage TLP avec une longueur de câble réduite, pour diminuer les largeurs d'impulsions. Le montage est également optimisé de sorte à limiter les éléments parasites et augmenter la bande passante du système d'acquisition (sondes et oscilloscope).

La mesure VF-TLP permet de tracer la courbe I-V du composant, pour en extraire les paramètres dynamiques et le courant de destruction. Toutefois, aucune correspondance ne peut être établie entre les niveaux de défaillances CDM et VF-TLP. En effet, pour ce dernier, l'impulsion est appliquée entre deux broches d'entrée/sortie, tandis qu'en CDM, l'impulsion est générée par le composant lui-même tout en tenant compte de la contribution du boîtier. Le composant se décharge ensuite à travers l'une des broches connectées à la masse. Pour contourner les limitations du VF- TLP, une nouvelle méthode de caractérisation appelée CC-TLP (*Capacitively coupled TLP*) a été développée [WOL 05]. Elle permet de prendre en compte l'effet du boîtier, tout en affichant une bonne corrélation avec les signatures de défaillance et les courants de pic CDM [BAF 18].

#### 4. Stratégies de protection ESD

Dans les sous-sections suivantes, nous allons décrire deux types de protections : internes et externes. Leurs modes de fonctionnement unidirectionnel et bidirectionnel dans l'application seront également présentés. Nous allons décrire ensuite quelques composants de base pour les produits de protections, dont les dispositifs à effet thyristor qui feront l'objet de cette étude.

#### 4.1. Types de protections

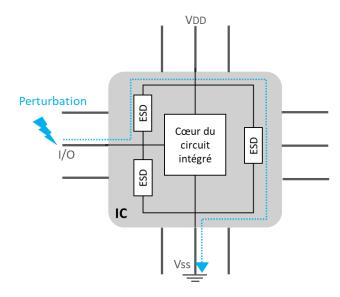

#### 4.1.1. Protections internes

Le risque ESD est présent tout au long du cycle de vie du composant, du fondeur à l'utilisateur final. Pour neutraliser les agressions ESD et éviter d'éventuelles dégradations du composant, les concepteurs ajoutent des protections dites « on-chip » dans le masque de conception du circuit intégré (figure 1.23). Ces protections sont placées à l'extérieur de la puce, aux niveaux des plots de connexion et d'alimentation. L'objectif est d'orienter le courant ESD vers la masse et éviter qu'il n'atteigne le cœur du circuit intégré.

Figure 1.23: Illustration simplifiée d'un réseau de protections internes du circuit intégré

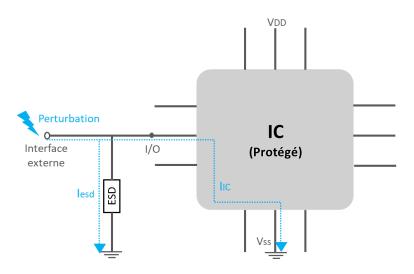

#### 4.1.2. Protections externes

Un système électronique est généralement composé de plusieurs circuits imprimés, ayant chacun un niveau de tolérance ESD différent [VIN 03]. Lorsqu'une perturbation ESD se produit, elle peut aussi bien provoquer une défaillance matérielle que fonctionnelle dans le système. La stratégie de protection consiste alors à augmenter la robustesse de ce dernier, en y ajoutant des protections externes, comme illustré dans la figure 1.24.

Figure 1.24: Illustration simplifiée d'une stratégie de protection externe

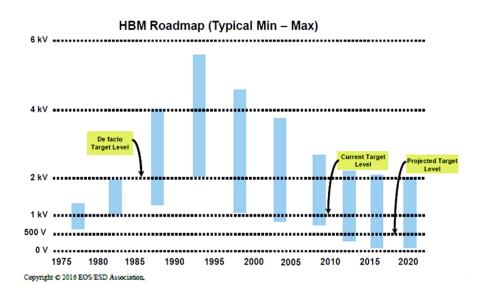

Cette combinaison entre les stratégies « on-chip » et « off-chip » est largement employée et pour cause, l'optimisation des performances du circuit intégré se fait parfois au détriment de sa tenue ESD [QIA 13]. De plus, le niveau de robustesse requis sur les entrées/sorties des composants électroniques est désormais inférieur aux 2kV-HBM usuels et ce niveau de tenue ESD est appelé à baisser pour les futures générations de protections internes selon l'association ESD (figure 1.25) [ESD 16]. Ainsi, les protections externes rajoutées aux entrées/sorties des systèmes électroniques permettent d'évacuer la majeure partie du courant de décharge et garantir un niveau de robustesse ESD global.

Figure 1.25: Evolution du niveau de tenue HBM des composants électroniques [ESD 16]

#### 4.2. Classification des protections

La configuration de la protection dépend du type d'application à protéger : unidirectionnelle ou bidirectionnelle.

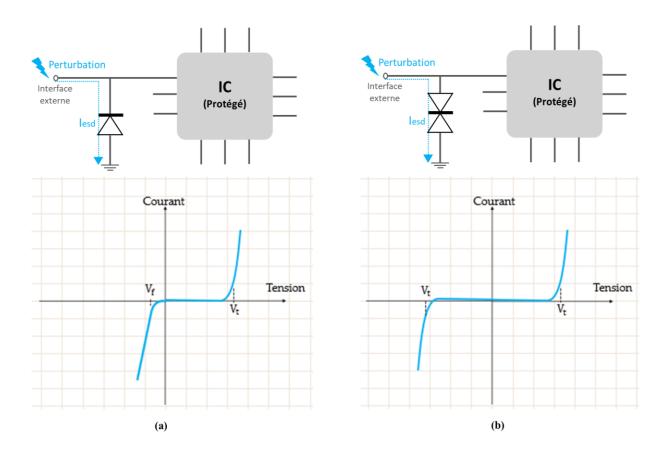

#### 4.2.1. Protections unidirectionnelles

Une protection unidirectionnelle conduit dans un sens et écrête dans l'autre. Même si le terme « unidirectionnel » peut prêter à confusion, ce dernier fait référence à la direction du signal applicatif [DUV 15]. Sur le plan électrique, la caractéristique I-V de la protection est asymétrique, avec une tension de seuil inverse proche de 0 V (figure 1.26-a). Dans l'application, les protections unidirectionnelles sont destinées à protéger des lignes unipolaires dont la tension nominale est

positive (e.g. : 0 V < Vsignal < 5 V). Elles peuvent également s'employer pour protéger les lignes bipolaires, à condition de les monter tête-bêche pour symétriser la structure.

#### 4.2.2. Protections bidirectionnelles

Une protection bidirectionnelle écrête dans les deux sens, quelle que soit la polarité du stress ESD. Sur le plan électrique, elle se caractérise par une courbe I-V symétrique, avec une tension d'avalanche qui peut être identique pour les deux modes de fonctionnement direct et inverse (figure 1.26-b). Sur le plan applicatif, les protections bidirectionnelles protègent les lignes unipolaires dont la tension varie en positif (ex : 0 V < Vsignal < 5 V). Elles protègent également les lignes bipolaires qui alternent à la fois des valeurs de tensions nominales positives et négatives (ex : -5 V < Vsignal < 5 V) [INF 19]. L'inconvénient majeur de ce type de protections réside dans le ratio performances/surface, qui se traduit par une robustesse réduite et un encombrement plus important dans le circuit [TEX 19] [LIM 13] [COU 15].

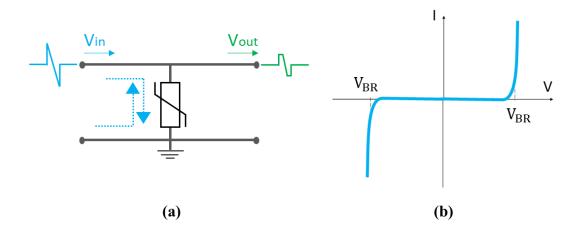

Figure 1.26: Schéma applicatif et caractéristique I-V d'un dispositif de protection : unidirectionnel (a) et bidirectionnel (b)

#### 4.3. Caractéristiques électriques et composants de base des protections

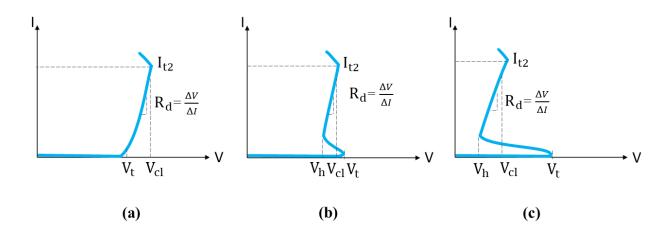

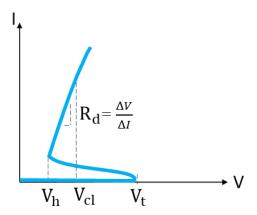

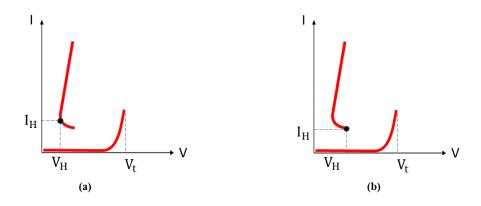

Le choix d'un dispositif de protection dépend de sa caractéristique électrique et de sa conformité vis-à-vis des spécifications du circuit à protéger. La figure 1.27 illustre les allures typiques des caractéristiques courant-tension, qui résument les différentes possibilités de protections externes : le premier cas (a) correspond à une protection « type-diode », avec une caractéristique I-V de type diode. Ses principaux paramètres sont : la tension d'avalanche (Vt), la résistance passante (Rd), la tension d'écrêtage (Vcl) et le courant de destruction (It2). Les cas (b) et (c) correspondent à des protections de « faible » et « fort » retournement, avec une caractéristique I-V de type-S. Les paramètres clés dans ce cas sont : les points de déclenchement et de maintien, la résistance passante et le courant de destruction.

Figure 1.27: Allures typiques des caractéristiques I-V des protections externes : type-diode (a), faible retournement (b) et fort retournement (c) [Adaptée de [INF 19]]

Les avantages et les domaines d'application de chacune des trois caractéristiques ci-dessus sont donnés dans le tableau récapitulatif 1.5.

| Caractéristique<br>I-V | Avantages                                                                                                                                 | Type d'applications                                                                                                                                            |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Type-diode             | <ul> <li>Fonctionnement simple, facile à utiliser</li> <li>Bonnes performances de protection</li> <li>Ecrêtage des surtensions</li> </ul> | <ul> <li>Applications nécessitant un déclenchement rapide</li> <li>Applications polyvalentes et faible débit : boutons, interrupteurs, audio, GPIO,</li> </ul> |

| Faible<br>retournement        | <ul> <li>› Performances de protection optimisées (V<sub>cl</sub>)</li> <li>› Faible capacité parasite (C<sub>L</sub>)</li> <li>› Bon compromis entre la tension maximale de fonctionnement (V<sub>WM</sub>) et la tension d'écrêtage (V<sub>cl</sub>)</li> </ul> | <ul> <li>Même applications que pour les<br/>protections type-diode, en plus des<br/>applications RF et haut-débit.</li> </ul>                                                                                                                                                |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fort retournement (Thyristor) | <ul> <li>Meilleures performances de protection toutes catégories confondues (V<sub>cl</sub>)</li> <li>Faible capacité parasite (C<sub>L</sub>)</li> </ul>                                                                                                        | <ul> <li>Applications RF</li> <li>Applications avec plus d'exigences sur le V<sub>cl</sub>:         <ul> <li>Applications haut-débit, LVDS (Transmission différentielle basse-tension)</li> <li>Technologies avancées des systèmes-sur puces SoC (nm)</li> </ul> </li> </ul> |

Tableau 1.5: Récapitulatif des caractéristiques et des applications pour les différentes possibilités de protections externes [INF 19]

Dans la famille des protections externes, on trouve cinq principaux types de composants : les diodes polarisées en direct, les diodes polarisées en inverse, les composants à effet thyristor et dans certains cas les varistances [GRA 98]. A noter qu'une combinaison sur silicium de plusieurs de ces composants semi-conducteurs est également possible ; il s'agit généralement de technologies brevetées [GRA 98]. Dans ce qui suit nous décrivont certains de ces composants et leurs principales caractéristiques.

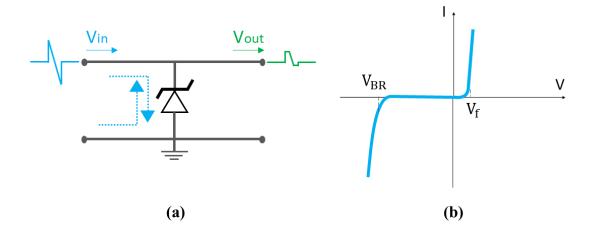

#### **4.3.1. Diode TVS**

Une diode TVS (*Transient Voltage Suppressor*) est assimilée à une diode Zener optimisée, avec un temps de réponse rapide et une capacité parasite réduite qui convient aux applications RF [VIN 03]. Il s'agit du composant le plus connu du marché de la protection, bien qu'il soit commercialisé sous plusieurs appellations : Transil pour STmicroelectronics, TranZorb pour Vishay, ou encore TVS pour NXP [BEN 10]. Une illustration de la caractéristique I-V de la diode TVS est donnée dans la figure 1.28.

Figure 1.28: Impulsion résiduelle (Vout) résultante de la tension d'écrêtage de la protection unidirectionnelle TVS (a), et caractéristique I-V unidirectionnelle correspondante (b)

Le caractère unidirectionnel des diode TVS se traduit par un fonctionnement en mode inverse, avec une tension d'avalanche supérieure à la tension nominale du circuit à protéger. Pour les applications bidirectionnelles, deux diodes TVS sont placées tête-bêche dans un même boîtier, afin de symétriser la caractéristique I-V du dispositif (figure 1.29).

Figure 1.29: Impulsion résiduelle (Vout) résultante de la tension d'écrêtage de la protection bidirectionnelle TVS (a), et caractéristique I-V bidirectionnelle correspondante (b)

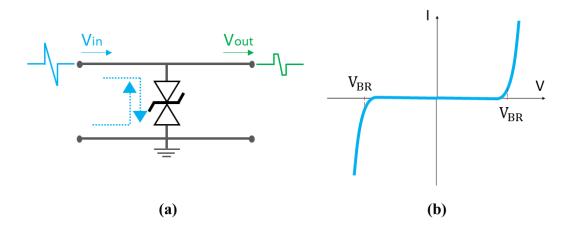

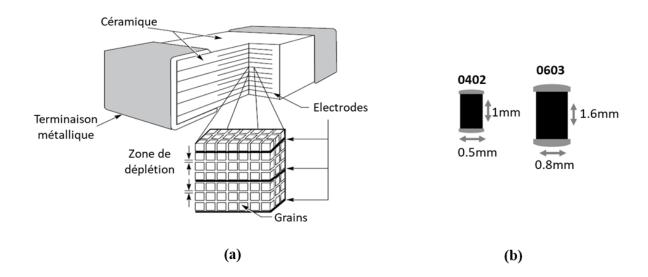

#### 4.3.2. Varistance

Une varistance est une résistance variable, non linéaire, qui dépend de la tension appliquée à ses bornes [GRA 93]. Il s'agit d'un composant bidirectionnel avec une caractéristique I-V symétrique,

qui s'étend sur une grande plage de courant et de tension. A l'état bloqué, la varistance oppose une impédance élevée qui chute très rapidement au-delà d'une certaine tension de seuil (figure 1.30).

Figure 1.30: Impulsion résiduelle (Vout) résultante de la tension d'écrêtage de la protection bidirectionnelle MOV (*Metal Oxide Varistor*) (a), et caractéristique I-V bidirectionnelle correspondante (b)

A l'origine, les varistances sont conçues pour limiter les surtensions transitoires, dans les applications moyennes et hautes tensions (ex : protection contre la foudre) [GRA 93]. La commercialisation d'une nouvelle technologie de varistances multicouches MLV (*Multi-layer varistor*) a permis d'étendre l'utilisation de ce type de protections aux applications basse tension [EAT 17] [LIT 16]. Ainsi, la variation de certains paramètres géométriques de la varistance, comme la surface et l'épaisseur, permet d'augmenter l'énergie de décharge absorbée par cette dernière, tout en diminuant sa tension de seuil. De plus, la miniaturisation des varistances a permis de réduire les dimensions des boîtiers, ce qui facilite leur implantation dans les circuits électroniques qui requièrent un encombrement réduit [EAT 17] (figure 1.31). Dans les applications à hautes fréquences, l'utilisation de la varistance se limite à la protection des bus d'alimentation, en raison de la capacité parasite non négligeable, qui entraîne une déformation des signaux sur les lignes de données haut-débit [BEN 10] [VIN 03].

Figure 1.31: Structure d'une varistance (MLV) (a) [Adaptée de [LIT 16]], et dimensions des boîtiers proposés pour ce type de protections (b) [Adaptée de [LIT 10]]

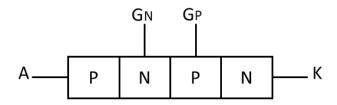

#### 4.3.3. Dispositifs à effet thyristor

Le thyristor ou *Silicon Controlled Rectifier* (SCR) est un composant bipolaire unidirectionnel, utilisé à la base comme interrupteur commandé en électronique de puissance. Son concept a été repris et adapté au domaine de la protection ESD, en raison de ses performances en termes de robustesse, courant de fuite, capacité parasite et résistance à l'état passant [BAF 18].

D'un point de vue technologique, le thyristor est un composant multicouche, formé par une succession de zones alternativement dopées (P-N-P-N) (figure 1.32). Ces quatre zones forment au total trois jonctions, dont une « centrale » polarisée en inverse. La mise en avalanche de cette jonction permet l'amorçage du thyristor. Des circuits auxiliaires de déclenchement peuvent être associés à la structure SCR au niveau de ses gâchettes GP et GN (figure 1.32).

Figure 1.32: Structure de base d'un dispositif SCR

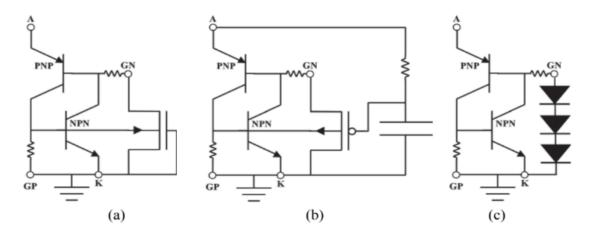

Ces circuits permettent entre autres d'ajuster la tension de déclenchement du thyristor en fonction du type d'application à protéger. Cela donne lieu à de nouvelles technologies de protection (figure 1.33), comme le DTSCR qui fait l'objet de cette étude.

Figure 1.33: Protections ESD à base d'une structure SCR, déclenchée à l'aide d'un : GGNMOS (a), PMOS déclenché par un circuit RC (b), et d'une chaine de diodes (c) [BAF 18]

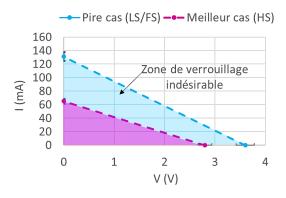

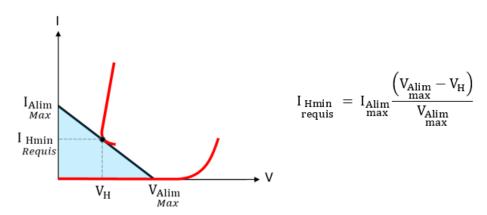

Le thyristor présente une caractéristique I-V à retournement. Une fois amorcé, il présente une tension de maintien bien en dessous de sa tension de déclenchement (figure 1.34). Ce mode de fonctionnement est favorable pour la tenue aux ESDs de la protection car il permet de supporter des courants plus forts comparés aux dispositifs sans retournement [NOL 05]. Ce mode de fonctionnement présente toutefois un inconvénient majeur lié au risque de verrouillage indésirable du dispositif lors d'un fonctionnement normal du circuit (en d'autres termes, la protection reste enclenchée).

Figure 1.34: Caractéristique I-V d'une protection ESD à base d'une structure SCR

#### 5. Qualité de la protection ESD

Dans les sous-sections suivantes, nous allons décrire les différents critères servant à définir la qualité de protection et les outils graphiques d'évaluation correspondants.

#### 5.1. Critères de qualité

La qualité de la protection ESD est définie dans ces travaux selon trois critères : robustesse, efficacité et transparence (la rapidité étant considérée comme un critère d'efficacité dans ces travaux) [AME 02].

#### **5.1.1.** Robustesse

Pour un modèle de décharge donné, la robustesse ESD est définie par la tension de précharge correspondant au stress maximal que peut supporter la protection sans défaillir. Elle dépend du critère de défaillance choisi et du type de stress ESD appliqué. Pour améliorer la robustesse du composant vis-à-vis des décharges ESD, il convient de tenir compte de son dessin et de sa technologie. Cependant, toute amélioration dans ce sens ne va pas sans dégrader d'autres performances comme l'efficacité, la transparence ou encore la miniaturisation. Ainsi une protection avec un fonctionnement vertical est plus favorable à la dissipation d'énergie qu'une structure latérale. De plus, la robustesse est souvent proportionnelle à la taille de la structure. En d'autres termes, si la densité de courant maximale supportée par une structure est de 10 mA/µm, alors une largeur de puce de 200 µm serait nécessaire pour tenir un courant de 2 A, soit une robustesse de 3 kV HBM. Toutefois, cette approche ne va pas toujours dans le sens de la miniaturisation des produits de protection, où les dimensions sont de plus en plus réduites.

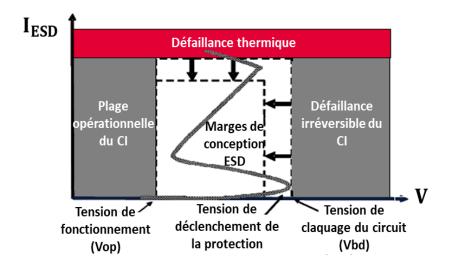

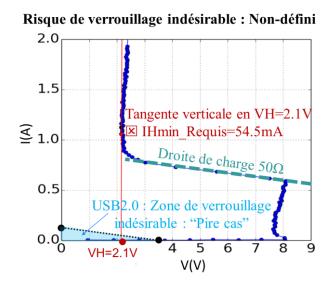

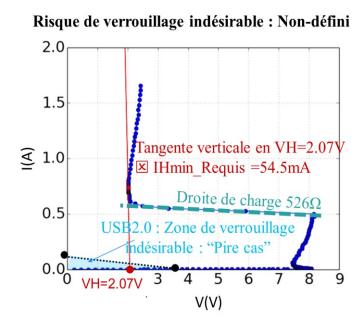

#### 5.1.2. Efficacité

L'efficacité de la protection définit sa faculté à écrêter les surtensions à ses bornes et les maintenir à des niveaux de tension suffisamment bas et sans danger pour le circuit à protéger. Pour garantir ce critère, la caractéristique I-V de la protection doit être placée dans une fenêtre de conception, dont les marges sont délimitées par les tensions d'alimentation et de destruction du circuit. Les tensions de déclenchement et de maintien de la caractéristique I-V doivent se trouver entre ces deux limites pour prévenir, d'une part la dégradation du circuit et d'autre part le déclenchement intempestif ou le verrouillage indésirable de la protection (à noter que ces deux critères pourraient également être considérés comme des critères de transparence de la protection vis-à-vis de

l'application). La résistance à l'état passant doit également être minimisée pour réduire les niveaux de tensions écrêtées et prévenir tout risque de dégradation à plus forts niveaux de courant.

Pour juger de l'efficacité de la protection, il faut également tenir compte de sa rapidité de déclenchement. Ainsi, lorsqu'une perturbation ESD se produit, la protection doit se déclencher quasi-instantanément pour évacuer le courant de décharge et limiter les surtensions aux bornes du circuit. Ce critère prend toute son importance lorsqu'il s'agit d'évacuer des courants de décharge de type HMM par exemple, où le pic de courant est très important avec un temps de montée très court, pouvant entraîner une dégradation du circuit.

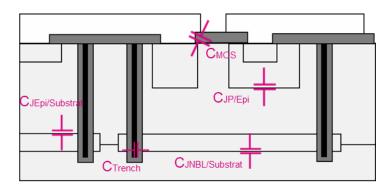

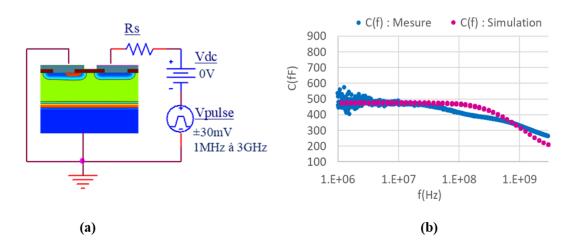

#### 5.1.3. Transparence

La transparence de la protection définit son aptitude à ne pas interférer avec le fonctionnement normal du circuit lorsqu'elle se trouve à l'état bloqué. En effet, le comportement de la protection n'est pas celui d'un interrupteur parfait. Lorsqu'elle ne conduit pas, la protection présente une matrice d'éléments parasites résistifs, inductifs et capacitifs, qui entraînent des perturbations dans le système, en particulier à hautes fréquences (au-delà du gigahertz). Certains de ces aspects parasites sont décrits ci-dessous :

Courant de fuite : c'est le courant qui traverse la protection à l'état « Off ». Il est donné en fonction de la tension d'alimentation de l'application. Ce courant doit être minimisé afin de limiter la consommation de la protection et éviter certaines dégradations comme les pertes en autonomie de batterie dans les systèmes mobiles.

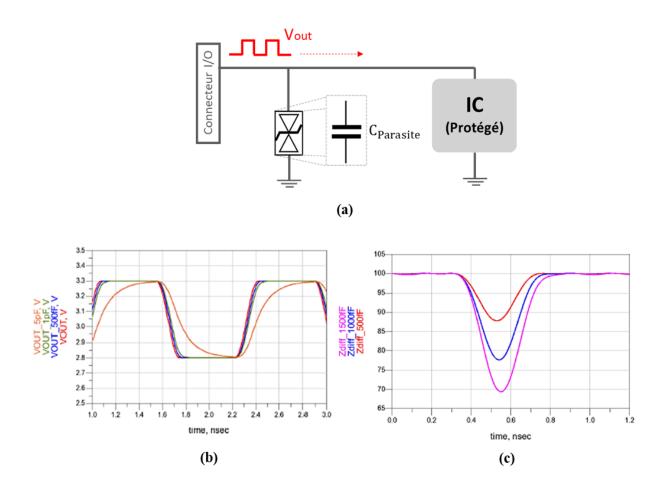

Capacité parasite: lorsqu'elle ne conduit pas, la protection présente une capacité parasite entre la ligne et la masse du circuit applicatif (figure 1.35-a). Dans certaines conditions, cette capacité peut altérer le fonctionnement normal du circuit et modifier l'allure générale des signaux transmis (retard, atténuation, distorsion). A hautes fréquences, la capacité parasite de la protection agit comme un court-circuit et une partie du signal transmis est dérivé vers la masse [LIM 13]. Cela entraîne une perte de puissance et une atténuation du signal qui se traduit par une réduction de la bande passante dans le circuit. Il est donc primordial dans le choix du dispositif de protection que sa perte d'insertion soit acceptable pour la bande passante de l'application choisie. Sa capacité parasite doit être suffisamment faible aussi pour ne pas affecter les fronts de montée des signaux transmis (figure 1.35-b) et éviter une désadaptation d'impédance à l'entrée du circuit (figure 1.35-c) [LIM 13] [MER 13].

Figure 1.35: Schéma applicatif d'une protection ESD assimilée à une capacité parasite en l'absence de décharge ESD (a). Simulation pour une ligne d'une paire différentielle d'un port HDMI (b), et Simulation avec lignes différentielles adaptées 100 Ω (c) [Adaptée de [MER 13]]

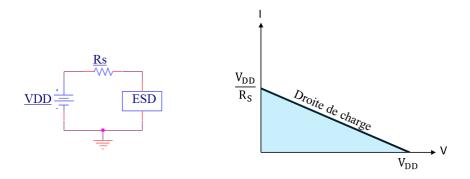

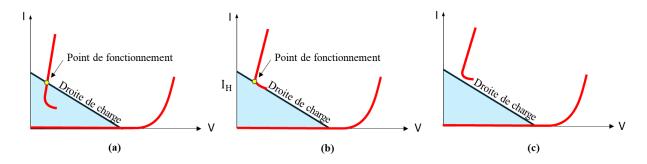

#### 5.2. Outils graphiques d'évaluation

Le choix d'une stratégie de protection repose sur un cahier des charges propre aux spécificités de chaque application. Pour garantir la qualité de la protection, les concepteurs ont souvent recours à un outil graphique appelé « fenêtre de conception ». Cette fenêtre délimite un intervalle de courant-tension, dans lequel la caractéristique I-V de la protection peut évoluer sans perturber ou dégrader le circuit à protéger (figure 1.36).

Figure 1.36: Fenêtre de conception des protections ESD [Adaptée de [IND 09]]

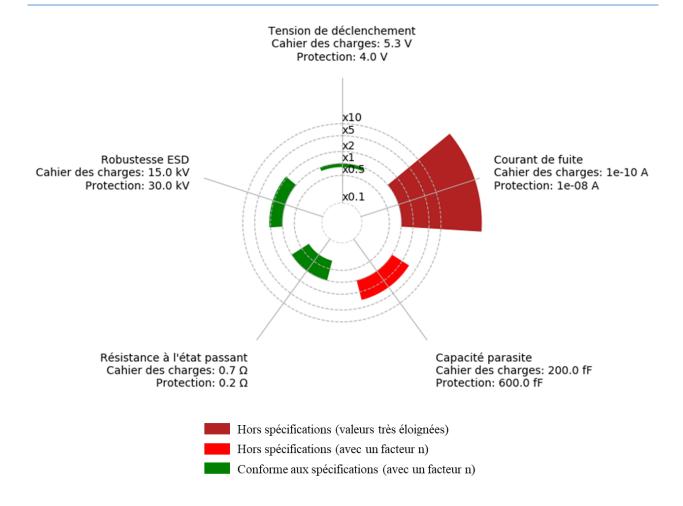

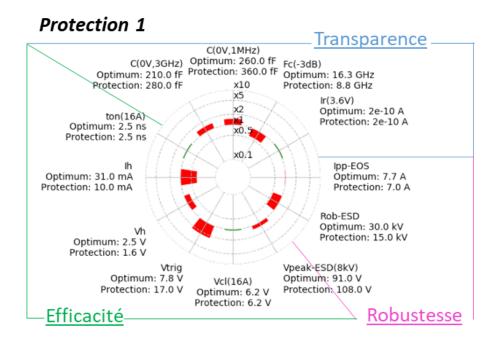

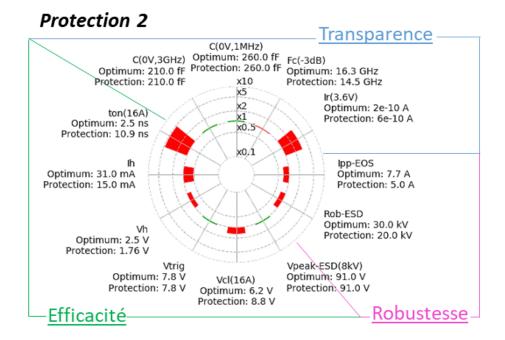

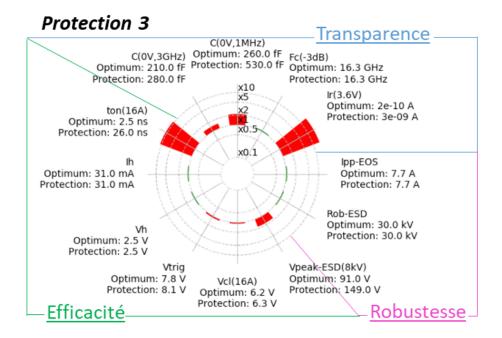

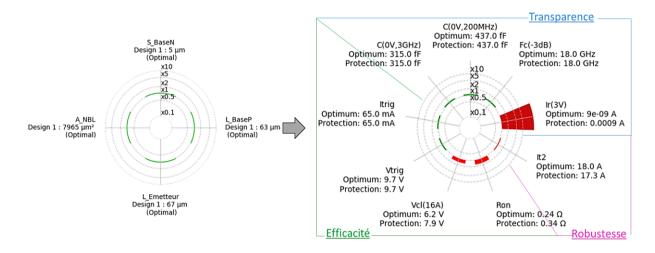

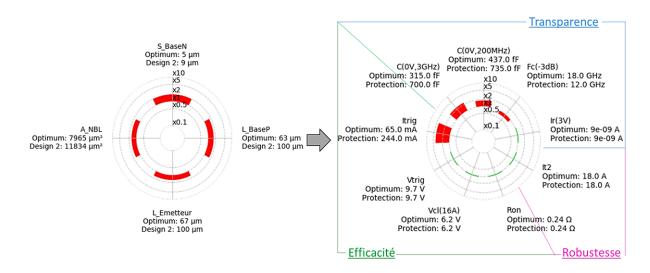

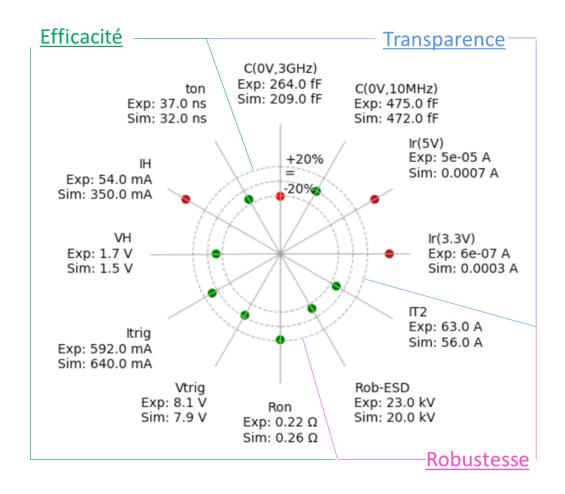

Dans une fenêtre de conception, figurent la caractéristique électrique de la protection, les plages de fonctionnement et de destruction du circuit, ainsi que le niveau de robustesse ESD souhaité. Les paramètres électriques évalués dans ce graphique sont la résistance à l'état passant et les couples courant-tension relatifs aux différents points de déclenchement, de destruction et de maintien pour les structures à retournement. Ces paramètres, bien que représentatifs des performances de la protection, ne donnent qu'une vue parcellaire de sa qualité. En effet, plusieurs autres paramètres liés à la transparence et l'efficacité ne figurent pas dans ce type de graphique (temps de déclenchement, capacité parasite, courant de fuite, etc.). Or ces différents paramètres de la protection sont de plus en plus critiques, en particulier pour les applications qui demandent à la fois une faible consommation, une fréquence de fonctionnement élevée et un encombrement réduit. Dans le cadre de ces travaux, un nouvel outil graphique appelé « radar des performances » a été mis en place, afin de compléter la description donnée par la fenêtre de conception et obtenir une vue globale et complète de la qualité de protection ESD. Un exemple de ce type de graphique est donné dans la figure 1.37. Outre la description de la qualité de protection, cet outil est également déployé pour comparer les performances électriques de plusieurs dispositifs de protections.

Figure 1.37: Représentation type « radar » des performances électriques de la protection par rapport aux exigences du cahier des charges

#### 6. Conclusion

Les décharges électrostatiques peuvent induire des défauts prématurés et irréversibles dans les circuits électroniques. Dans ce chapitre, nous avons présenté les principaux mécanismes à l'origine des décharges ESD, ainsi que les moyens mis en place pour s'en prémunir. Ces solutions vont de l'aménagement de zones EPA à l'amélioration de la robustesse des composants. Dans ce contexte, des protocoles de tests ont été développés pour évaluer la vulnérabilité des circuits face aux décharges ESD. Ces tests dits de « qualification » se divisent en deux catégories, ceux appliqués aux composants, comme l'HBM et le CDM et ceux appliqués aux systèmes, comme l'IEC61000-4-2. Comme il s'agit de tests destructifs, ils ne permettent pas d'étudier les mécanismes menant à la défaillance du circuit. Pour contourner cette limitation, des tests complémentaires comme le TLP

sont réalisés pour obtenir la caractéristique I-V du composant et en extraire les paramètres électriques nécessaires à son optimisation.

Dans la suite de ce chapitre, nous avons exploré les différentes stratégies de protection. Celles-ci peuvent être internes au circuit intégré ou externes à ce dernier, on parle alors de protections système. Le mode d'écrêtage unidirectionnel ou bidirectionnel des dispositifs de protection est dicté par le mode de fonctionnement de l'application ciblée (signaux unipolaires ou alternatifs). Dans l'ensemble, les applications imposent un certain nombre d'exigences vis-à-vis des dispositifs de protection, que cela soit en termes de coût, d'encombrement ou de performance. Dans ces travaux, la qualité de protection est définie selon trois critères, l'efficacité, la robustesse et la transparence. Nous avons choisi de réunir ces trois critères dans un radar de performance, qui donne une vue d'ensemble des paramètres électriques du dispositif étudié. Les notions présentées dans ce chapitre serviront de base pour l'étude de cas présentée dans le chapitre suivant, qui porte sur la qualité de protection d'une structure à retournement de type DTSCR.

### Chapitre 2

# Qualité de protection du dispositif DTSCR

Dans l'étude de la qualité de la protection ESD, le choix s'est porté sur une solution à retournement de type *Diode Triggered Silicon Controlled Rectifier* (DTSCR). Une description de son mode de fonctionnement et de ses caractéristiques électriques est réalisée dans la première partie de ce chapitre. L'étude se focalise ensuite sur la pertinence des méthodes de test pour certains des paramètres clés du dispositif. La qualité de la protection et ses axes d'amélioration sont ensuite comparés, au moyen d'une étude comparative, sur une sélection de produits à retournement.

#### 1. Descriptif du dispositif de protection DTSCR

Dans la famille des protections à retournement, le DTSCR est souvent utilisé pour immuniser les circuits haute fréquence contre les décharges électrostatiques [MER 03]. En effet, à l'état bloqué, le DTSCR se caractérise par une faible capacité parasite. Celle-ci limite l'interférence de la protection avec le circuit à protéger, lorsque ce dernier est en fonctionnement normal (en l'absence de perturbations ESD). A l'état passant, le DTSCR se replie et affiche une résistance série et une tension de maintien réduites. Cela a pour effet de diminuer la puissance dissipée dans le dispositif et le rend plus robuste aux décharges électrostatiques [WON 05]. Dans ce qui suit, nous décrivons la structure du DTSCR et son principe de fonctionnement

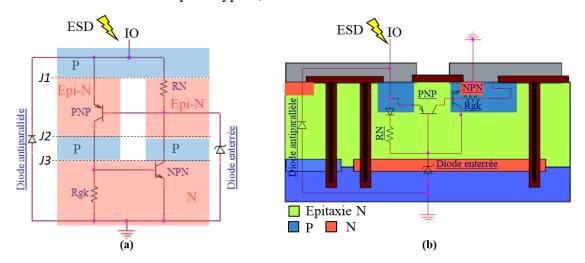

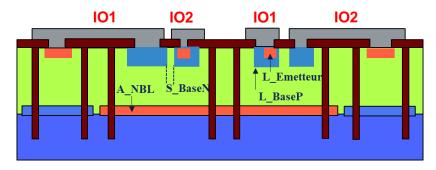

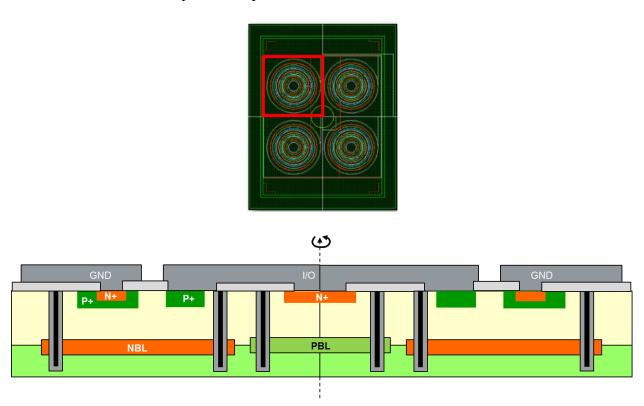

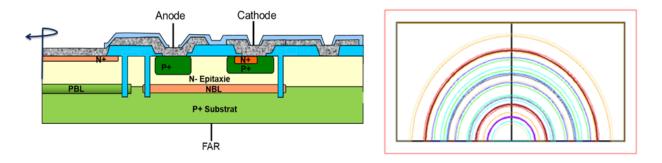

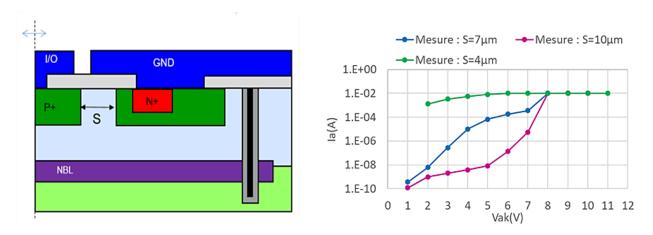

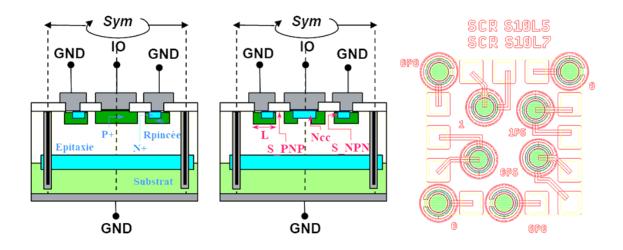

#### 1.1.Structure

La figure 2.1-a donne une vue schématique du dispositif de protection étudié. Il s'agit d'une protection unidirectionnelle, composée d'une structure DTSCR pour le fonctionnement en direct et d'une diode antiparallèle pour le fonctionnement en inverse. La structure DTSCR est formée par un thyristor et un circuit auxiliaire de déclenchement. Ce circuit est composé d'une diode Zener en série avec la base du transistor PNP. Une fois en avalanche, la diode injecte un courant de gâchette qui commande le déclenchement du thyristor complet.

La figure 2.1-b donne une vue en coupe de la structure DTSCR. Celle-ci est composée d'un empilement de quatre couches alternées et réalisé sur un substrat fortement dopé de type P. Cet empilement est décrit selon les trois composantes suivantes :

- Le transistor NPN : composé d'un émetteur de type N fortement dopé et diffusé dans le caisson de base P. Ce dernier est implanté dans la couche d'épitaxie N- qui forme la région collectrice.

- Le transistor PNP : son émetteur est formé par le caisson P et partage sa jonction basecollecteur avec le transistor NPN.

- La diode Zener verticale est formée par une couche enterrée fortement dopée de type N et un substrat fortement dopé de type P, afin de réduire sa tension d'avalanche.

Figure 2.1: Vue en coupe (a) et schématique (b) du dispositif de protection DTSCR

#### 1.2. Principe de fonctionnement

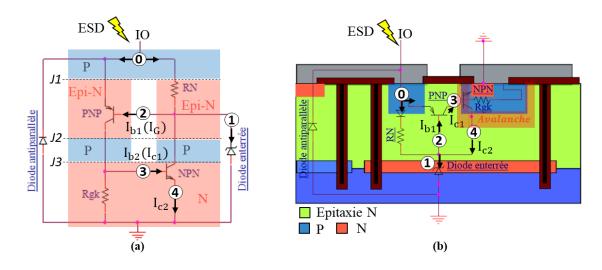

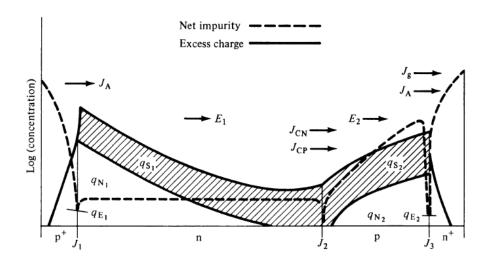

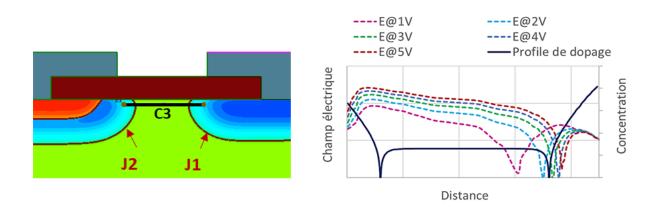

#### 1.2.1. Fonctionnement en direct

Lorsqu'une impulsion ESD positive est appliquée au niveau de l'anode du DTSCR (figure 2.2), les jonctions JI et J3 sont polarisées en direct, tandis que la jonction J2 est polarisée en inverse. Dans ce cas, la zone de charge d'espace s'étend principalement dans la couche d'épitaxie et seule la jonction J2 du transistor NPN tient la tension aux bornes du DTSCR. En polarisation inverse, lorsque la diode enterrée se met en avalanche, un courant est injecté dans la base du transistor PNP. Ce dernier se met à conduire et son courant collecteur vient polariser la base du transistor NPN, qui finit par s'amorcer. Son courant collecteur s'ajoute alors au courant de gâchette pour polariser la base du transistor PNP et accroître ainsi son courant collecteur.

Figure 2.2: Principe de fonctionnement du DTSCR

Lorsque la contribution réciproque aux courants de polarisation des deux transistors est suffisante pour maintenir ce dernier à l'état passant (auto-entretien), le champ électrique à ses bornes diminue et la tension minimale à ses bornes est égale à une tension de maintien. Cette tension correspond à la somme des potentiels des deux jonctions (*J1*, *J3*) polarisées en direct. Le DTSCR forme alors un chemin de décharge de faible impédance pour évacuer l'ESD, ce qui limite la tension aux bornes de la protection et préserve ainsi la partie fonctionnelle du circuit à protéger. La structure DTSCR repasse à l'état bloqué lorsque le courant de décharge qui la traverse devient inférieur à son courant de maintien.

#### 1.2.2. Fonctionnement en inverse

Lorsqu'une impulsion ESD négative est appliquée au niveau de l'anode du DTSCR, les jonctions J1 et J3 sont polarisées en inverse, tandis que la jonction J2 est polarisée en direct. L'injection d'un courant de gâchette ne permet donc pas d'amorcer le thyristor et la décharge est évacuée par la diode antiparallèle, qui dans ce cas est polarisée en direct ( $\sim 1$  V).

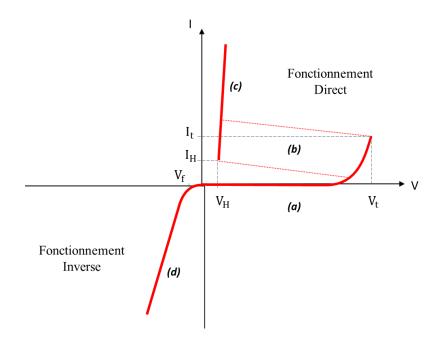

#### 1.3. Caractéristique Courant-Tension

La caractéristique courant-tension du dispositif de protection est illustrée dans la figure 2.3. Elle est donnée sur deux quadrants, en fonctionnement direct et en fonctionnement inverse.

Figure 2.3: Caractéristique courant-tension du dispositif de protection

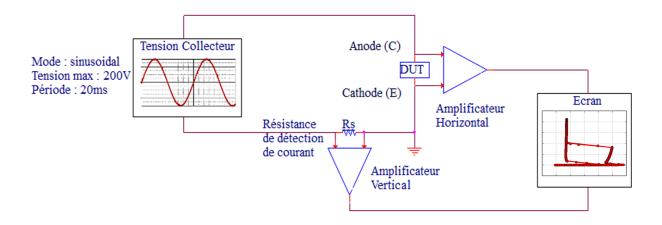

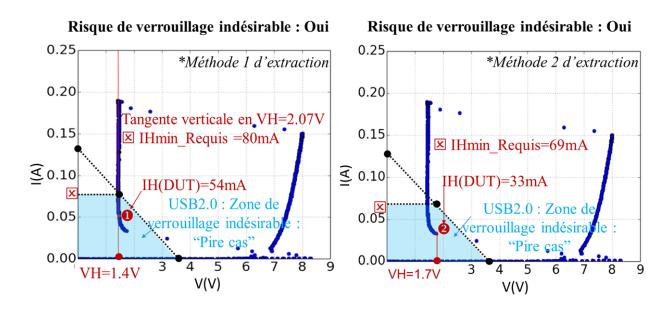

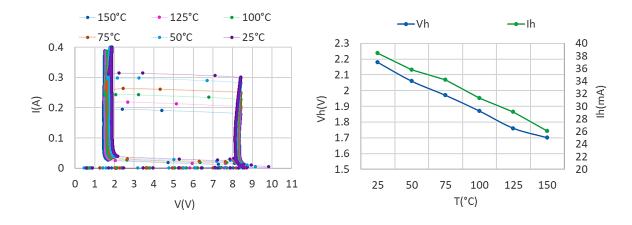

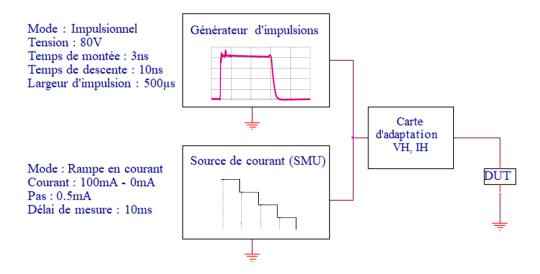

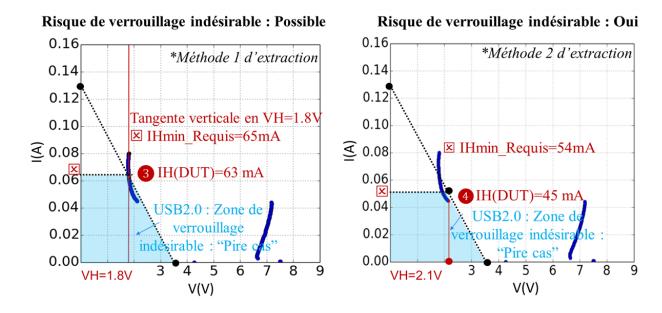

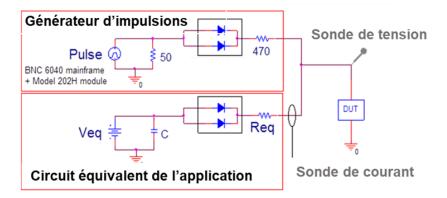

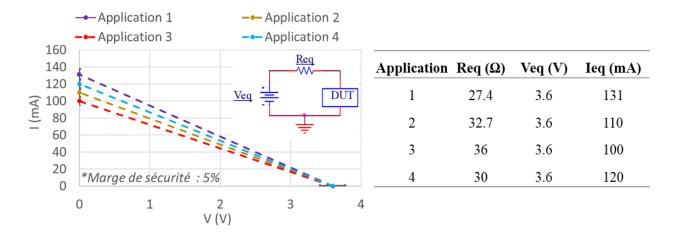

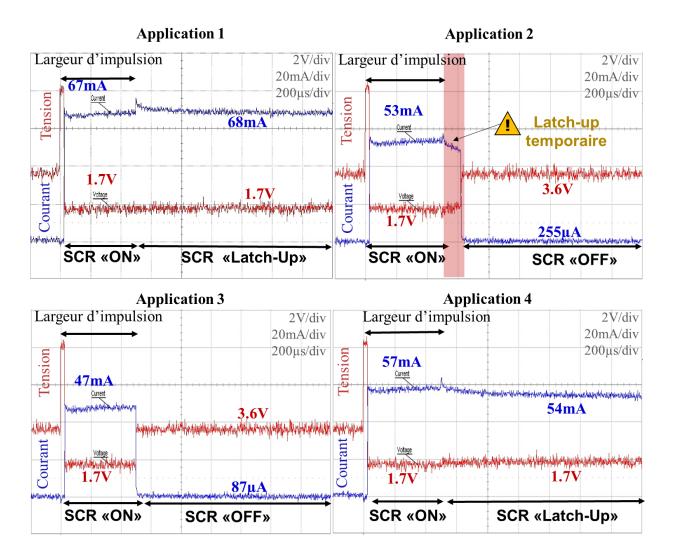

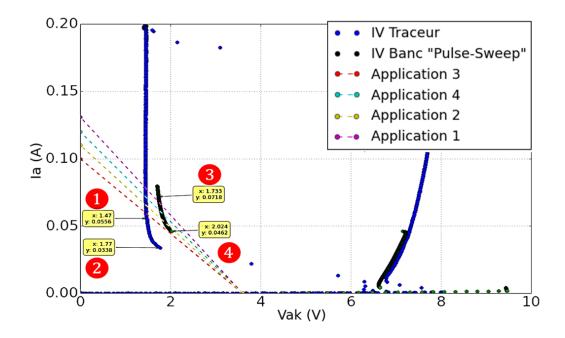

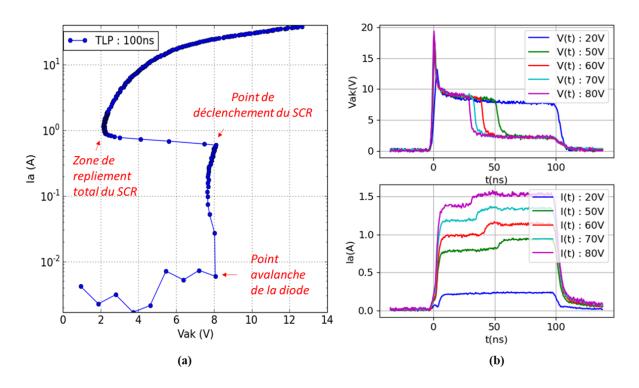

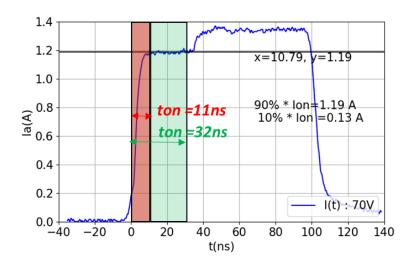

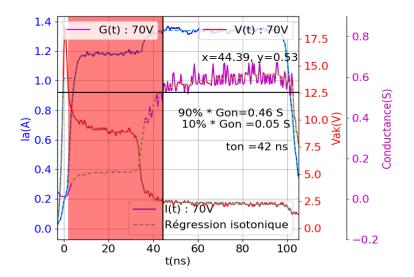

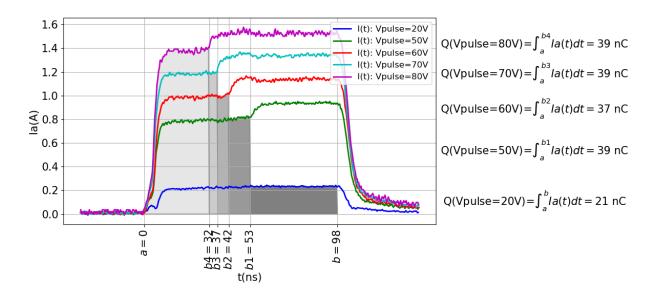

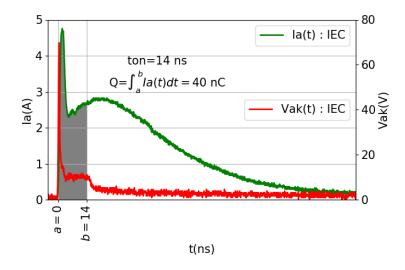

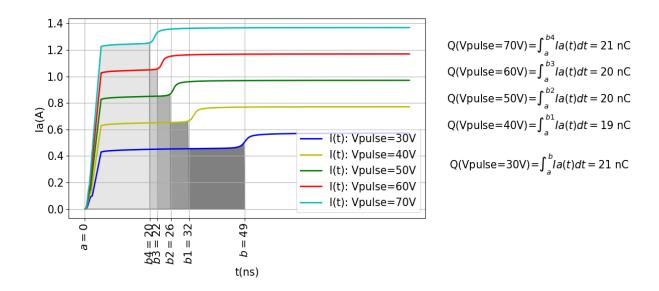

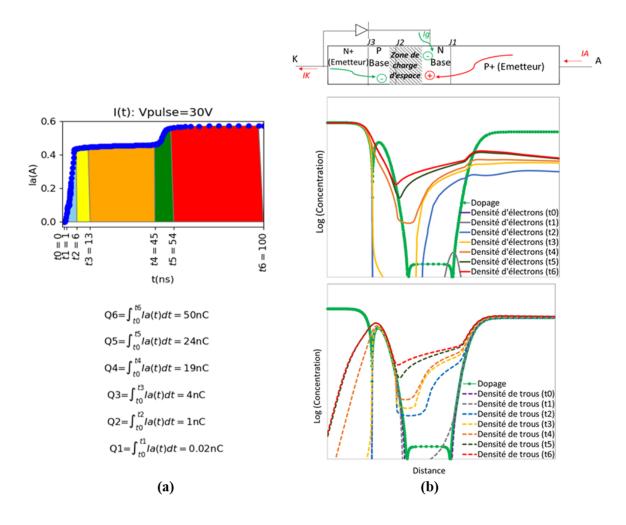

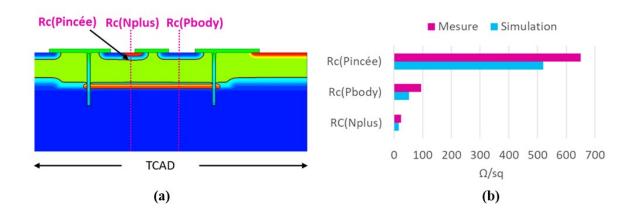

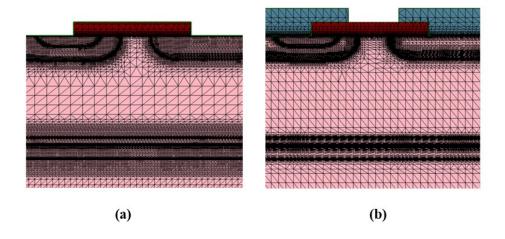

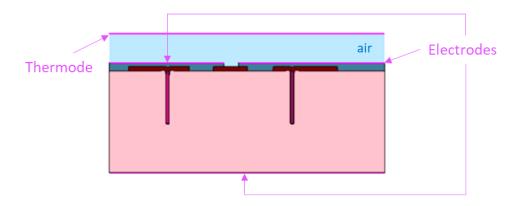

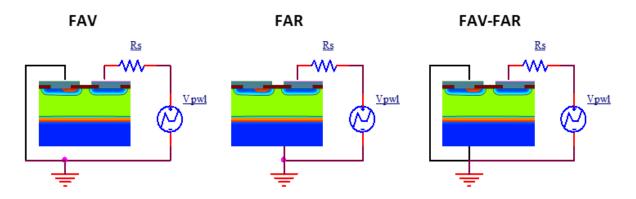

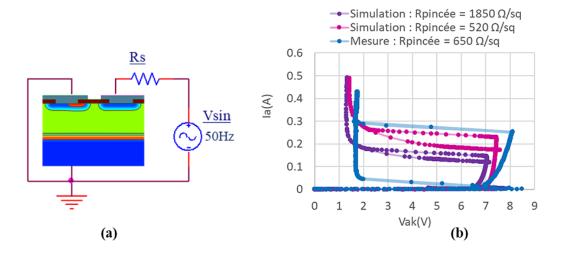

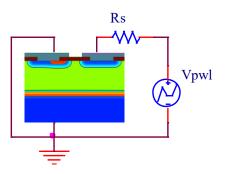

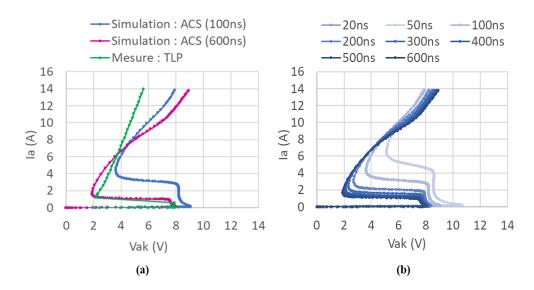

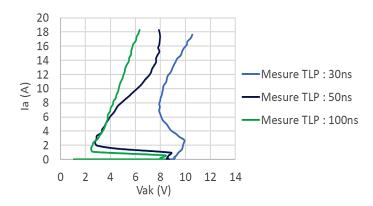

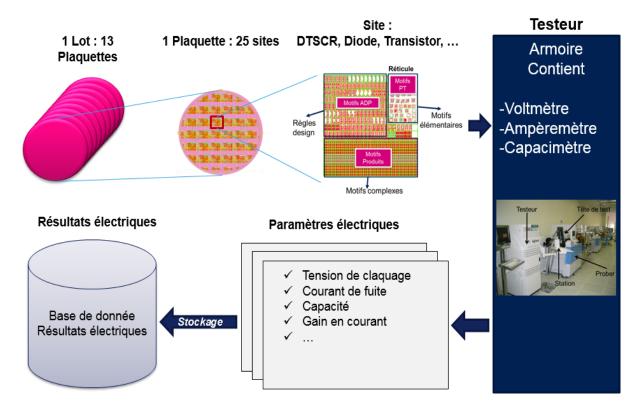

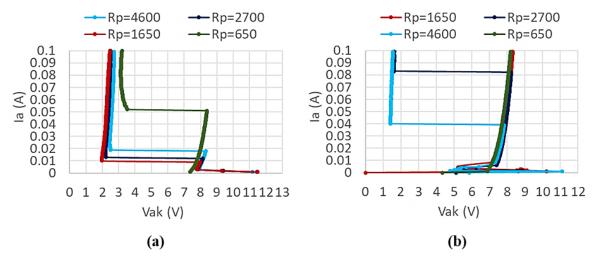

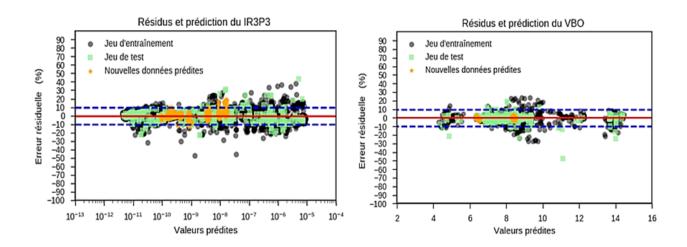

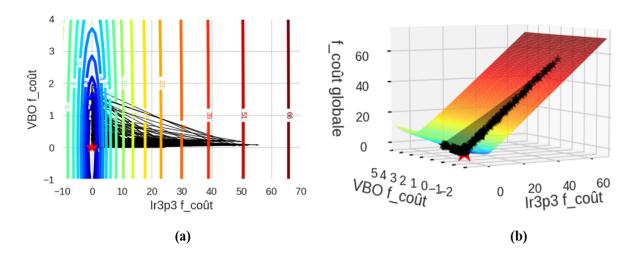

La région (a) de la caractéristique I-V correspond à l'état bloqué du DTSCR en fonctionnement direct. La « sensibilité du thyristor » définit le point de déclenchement de la structure noté (Vt, It). La courbe I-V présente ensuite une résistance négative de type « S », avec un état instable et un temps de commutation lié au temps d'installation des charges (région (b)). L'amplitude de repliement entre le point de déclenchement et le point de maintien (VH, IH) dépend du gain en courant des deux transistors qui composent le thyristor. A l'état passant (région (c)), le thyristor peut être approximativement comparé à une diode PIN [ARN 92].