# Development of an innovative 77 GHz radar receiver architecture and demonstration in 28 nm FDSOI CMOS

Alexandre Flete

#### ▶ To cite this version:

Alexandre Flete. Development of an innovative 77 GHz radar receiver architecture and demonstration in 28 nm FDSOI CMOS. Micro and nanotechnologies/Microelectronics. INPT, 2022. English. NNT: 2022 TOU 30128. tel-03813771 v 1

# HAL Id: tel-03813771 https://laas.hal.science/tel-03813771v1

Submitted on 12 Oct 2022 (v1), last revised 13 Oct 2022 (v2)

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### En vue de l'obtention du

# DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE

Délivré par :

Université Toulouse 3 Paul Sabatier (UT3 Paul Sabatier)

# Présentée et soutenue par : Alexandre Flete

le 31 Mai 2022

Titre:

Développement d'une architecture innovante de récepteur radar à 77 GHz et démonstration en CMOS 28 nm FDSOI

#### École doctorale et discipline ou spécialité :

ED GEET : Électromagnétisme et Systèmes Haute Fréquence

Unité de recherche :

LAAS-CNRS

Directeur/trice(s) de Thèse:

Christophe Viallon, Thierry Parra et Philippe Cathelin

#### Jury:

Mr Jean Gaubert, Président du jury et examinateur Mme Nathalie Deltimple, Rapporteur M Sylvain Bourdel, Rapporteur M Christophe Viallon, Directeur de thèse M Thierry Parra, Co-directeur de thèse M Philippe Cathelin, Co-directeur de thèse

# A DISSERTATION

# In order to obtain the title of DOCTOR OF THE UNIVERSITY OF TOULOUSE

Issued by Université Toulouse 3 - Paul Sabatier

# Defended by Alexandre FLETE

On 31 May 2022

Design of an innovative 77 GHz radar receiver architecture in 28-nm FDSOI CMOS

PhD School: **GEETS - Génie Electrique Electronique, Télécommunications et Santé : du système au nanosystème**

Department: Electromagnétisme et Systèmes Haute Fréquence

Research Laboratory:

LAAS - Laboratoire d'Analyse et d'Architecture des Systèmes

Supervised by

Christophe VIALLON, Thierry PARRA and Phillippe CATHELIN

The jury members

Mrs. Nathalie DELTIMPLE, Referee

Mr. Sylvain BOURDEL, Referee

Mr. Christophe VIALLON, PhD Supervisor

Mr. Thierry PARRA, PhD Co-supervisor

Mr. Philippe CATHELIN, PhD Co-supervisor from the socio-economic world

Mr. Jean GAUBERT. President

# Résumé:

Grâce à sa capacité à détecter des cibles éloignées malgré une mauvaise visibilité, le radar automobile à 77 GHz joue un rôle important dans l'aide à la conduite. L'utilisation des fréquences millimétriques offre une bonne résolution et une importante capacité d'intégration des circuits. C'est aussi un défi car il faut satisfaire un cahier des charges exigeant sur le bruit et la linéarité du récepteur.

Les technologies SiGe BiCMOS ont été les premières utilisées pour la conception de récepteurs radar à 77 GHz. De bons résultats ont été obtenus en se basant sur des architectures utilisant des mélangeurs actifs. Cependant l'utilisation des technologies BiCMOS se traduisait par une consommation élevée, une faible capacité d'intégration et des couts de production importants. Récemment, l'intégration des procédés CMOS menant à l'augmentation des fréquences de transition rend ces technologies plus attractives pour les applications nécessitant un faible coût et la cointégration de plusieurs fonctions au sein d'une même puce.

La littérature sur les récepteurs radars en technologie CMOS à 77 GHz montre que les architectures inspirées par les technologies BiCMOS ne sont pas pertinentes pour cette application. Le but de cette thèse est de montrer que l'utilisation de techniques propres aux technologie CMOS comme l'échantillonnage et l'utilisation de portes logiques permet d'obtenir de très bonnes performances.

Dans ce travail, deux nouvelles architectures de récepteur radar basées sur le principe d'échantillonnage sont proposées. La première architecture est basée sur un mélangeur passif échantillonné qui permet d'obtenir un très bon compromis bruit/linéarité. La seconde exploite les propriétés des mélangeurs sous-échantillonnés afin utiliser une fréquence d'OL trois fois inferieure à la fréquence RF offrant ainsi de très intéressantes simplifications au niveau de la chaine de distribution du signal d'OL du récepteur.

Le contexte de cette étude est expliqué dans le 1<sup>er</sup> chapitre qui présente les exigences de conception liées à l'application radar et fourni une analyse de l'état de l'art des récepteurs à 77 GHZ. Le chapitre suivant décrit le principe de fonctionnement et l'implémentation d'un mélangeur échantillonné à 77 GHz en technologie CMOS 28-nm FDSOI. Une topologie de mélangeur sous-échantillonné utilisant une fréquence d'OL de 26 GHz pour convertir des signaux RF autour de 77 GHz est ensuite détaillée dans le chapitre 3. Le chapitre 4 conclut cette étude en détaillant l'intégration des mélangeurs étudiés dans les chapitres précédents avec un amplificateur faible bruit dans différents récepteurs radars. Ces architectures de récepteurs basées sur l'échantillonnage sont ensuite comparées entre elles et avec l'état de l'art montrant ainsi leurs avantages et inconvénients. Les résultats de cette comparaison confirment l'intérêt des techniques d'échantillonnage pour la conversion de fréquence dans le cadre de l'application radar.

# **Summary:**

With its ability to detect distant targets under harsh visibility conditions, the 77 GHz automotive radar plays a key role in driving safety. Using mm-wave frequencies allow a good range resolution, a better circuit integration and a wide modulation bandwidth. This is also a challenge for circuit designers who must fulfill stringent requirements especially on the receiver front-end.

First 77 GHz radar receivers were manufactured with SiGe BiCMOS processes benefiting from the high transition frequency and high breakdown voltage of Hetero-junction Bipolar Transistors (HBT). Good results have been achieved with active-mixer-based architectures, but these technologies suffer from high power consumptions, limited integration capacity and large production cost.

More recently, the scaling down of CMOS processes (coming together with the increase of the transition frequency of the transistors) makes CMOS a good candidate for 77 GHz circuit design, especially when cost target requires single chip solutions.

The literature related to CMOS radar receivers highlights that receivers based on BiCMOS architectures generally show poor performances. The aim of this work is to demonstrate that using CMOS specific technics such as sampling and the use of high-speed digital gates should enhance the performance of the receivers.

In this work, two innovative radar receiver architectures based on the sampling principle are proposed. The first one shows that this principle can be extended to millimeter wave frequencies to benefit from a very good noise/linearity trade-off. While the second one uses this principle to converts a 77 GHz RF signal by using a 26 GHz LO frequency thus simplifying the LO distribution chain of the receiver.

The background of this study is introduced in the chapter 1 presenting the design trade-off related to the 77 GHz radar receiver and provides a review of the existing solutions. The following chapter describes the sampling mixer principle and the implementation of a 77 GHz sampling mixer in 28-nm FDSOI CMOS technology. Then, a sub-sampling mixer topology allowing to convert an RF signal around 77 GHz using a 26 GHz LO frequency is detailed in the chapter 3. The chapter 4 draws the conclusion of this study by showing the implementation of the two proposed sampling-based mixers with a low noise amplifier in 77 GHz front ends. These receiver architectures are compared with the state of the art highlighting the strengths and weaknesses of the proposed solutions. The results of this study demonstrates that using sampling for down conversion can be convenient to address millimeter-wave frequency applications.

# **Table of Contents**

| Table of              | Contents                                                        | 7  |

|-----------------------|-----------------------------------------------------------------|----|

| Acknow                | ledgments                                                       | 11 |

| General               | introduction                                                    | 13 |

| Chapter               | 1 The 77 GHz radar for automotive applications                  | 15 |

| 1.1                   | Introduction                                                    | 15 |

| 1.2                   | The radar among the driving assistance sensors                  | 16 |

| 1.3                   | Basics of the automotive radar                                  | 17 |

| 1.4                   | The FMCW modulation                                             | 18 |

| 1.5                   | Frequency band allocation                                       | 19 |

| 1.6                   | Automotive radar receiver architecture                          | 21 |

| 1.7                   | Requirements on the receiver design                             | 21 |

| 1.8                   | Evolution in automotive radar                                   | 23 |

| 1.9                   | 28-nm FD-SOI CMOS technology description                        | 24 |

| 1.9.                  | 1 FD-SOI CMOS transistor                                        | 24 |

| 1.9.                  | 2 Metal stack                                                   | 26 |

| 1.9.                  | 3 Passive components                                            | 27 |

| 1.10                  | 77 GHz radar receiver architectures                             | 27 |

| 1.10                  | 0.1 Radar receivers based on active mixers                      | 27 |

| 1.10                  | 0.2 Radar receivers based on passive mixers                     | 30 |

| 1.10                  | 0.3 Radar receivers based on sub-harmonic mixers                | 34 |

| 1.11                  | Conclusion                                                      | 35 |

| Chapter<br>technology |                                                                 |    |

| 2.1                   | Introduction                                                    | 37 |

| 2.2                   | Conventional CMOS passive mixers                                | 37 |

| 2.2.                  | 1 Operating principle                                           | 38 |

| 2.2.                  | 2 Passive mixer conversion gain                                 | 39 |

| 2.2.                  | 3 Noise in passive mixer                                        | 39 |

| 2.2.                  | 4 Passive mixer linearity                                       | 40 |

| 2.2.                  | 5 Conventional CMOS passive mixer for millimeter-wave receivers | 40 |

|                       |                                                                 |    |

| 2.3 | San    | npling passive mixer principle                                       | 40 |

|-----|--------|----------------------------------------------------------------------|----|

| 2   | .3.1   | Using sampling for down-conversion                                   | 41 |

| 2   | .3.2   | Sampling passive mixer operating principle                           | 42 |

| 2   | .3.3   | Sampling mixer conversion gain                                       | 42 |

| 2   | .3.4   | Noise in sampling mixer                                              | 43 |

| 2   | .3.5   | Sampling mixer linearity                                             | 45 |

| 2   | .3.6   | Previous works on high frequency sampling passive mixers             | 46 |

| 2.4 | Lov    | v duty cycle LO signal and frequency limitations                     | 46 |

| 2   | .4.1   | High frequency low duty cycle LO signal                              | 46 |

| 2   | .4.2   | CMOS low duty cycle signal generation at millimeter-wave frequencies | 47 |

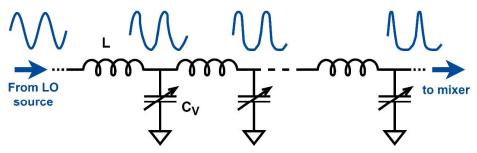

| 2.5 | Noı    | n-Linear Transmission Lines for millimeter-wave pulse shaping        | 48 |

| 2.6 | A n    | ew 77 GHz pulse shaper architecture                                  | 49 |

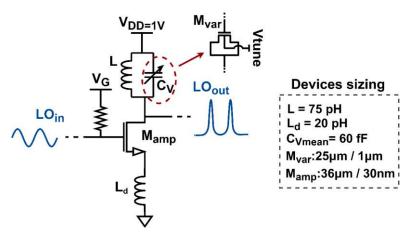

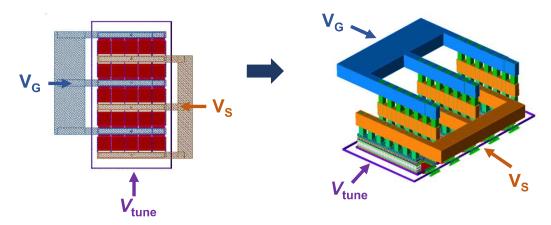

| 2.7 | Pul    | se shaper implementation                                             | 50 |

| 2   | .7.1   | NMOS Varactor implementation                                         | 50 |

| 2   | .7.2   | Stability                                                            | 51 |

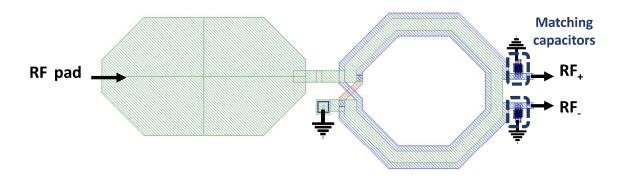

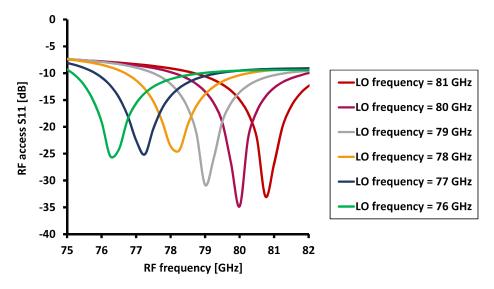

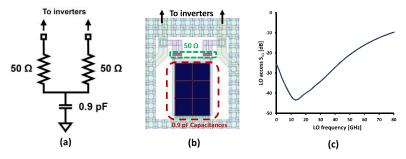

| 2   | .7.3   | LO input matching                                                    | 52 |

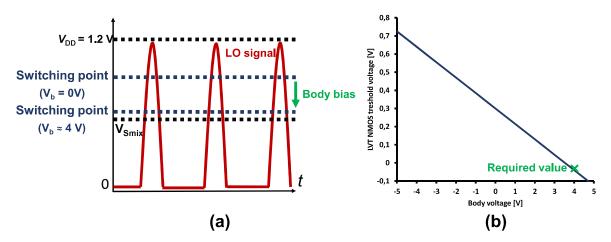

| 2.8 | Ger    | nerated LO pulsed waveform                                           | 53 |

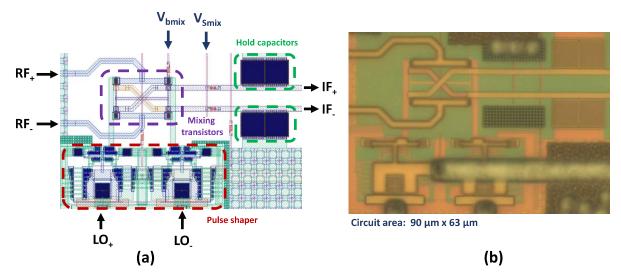

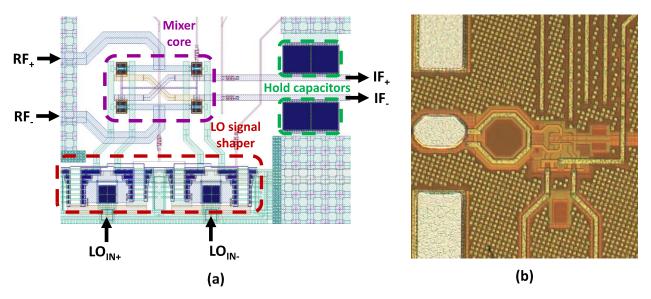

| 2   | .8.1   | Layout description                                                   | 54 |

| 2.9 | San    | npling mixer core implementation                                     | 56 |

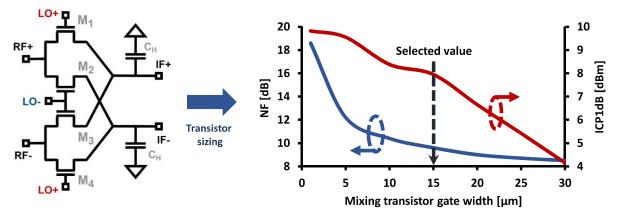

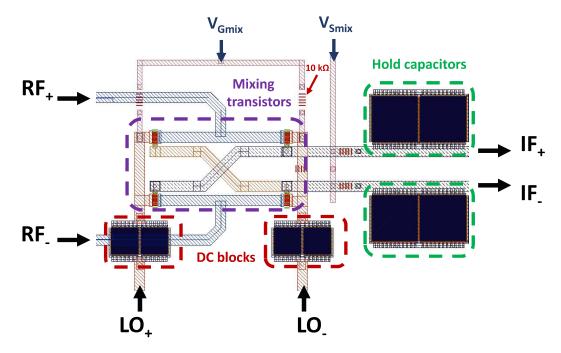

| 2   | .9.1   | Mixing transistor and hold capacitor sizing                          | 56 |

| 2   | .9.2   | RF input matching                                                    | 58 |

| 2.1 | 0 Sta  | ndalone mixer simulated performances                                 | 59 |

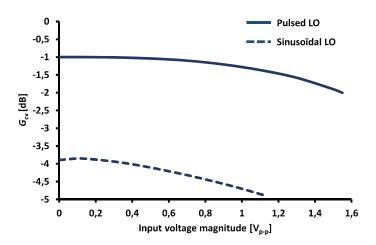

| 2   | .10.1  | Gain and linearity                                                   | 59 |

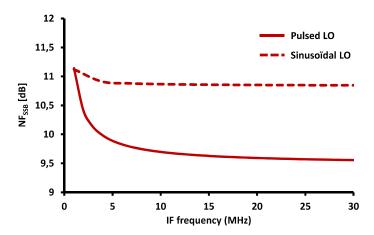

| 2   | .10.2  | Noise                                                                | 60 |

| 2.1 | 1 IF ( | Operational amplifier followers                                      | 61 |

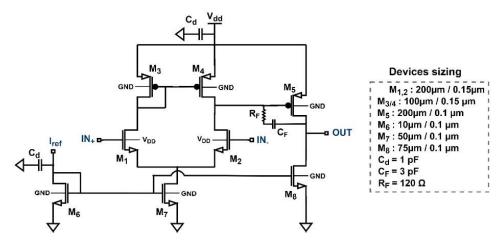

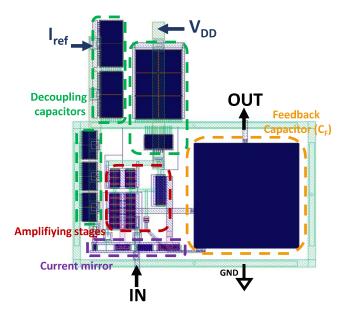

| 2   | .11.1  | Operational amplifier design                                         | 62 |

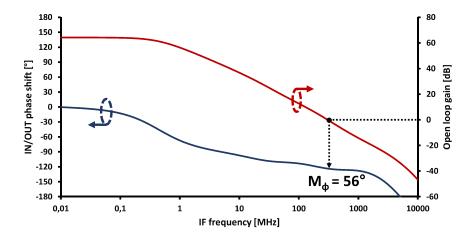

| 2   | .11.2  | Open loop analysis                                                   | 63 |

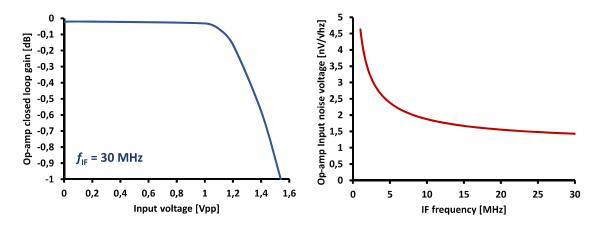

| 2   | .11.3  | Closed loop performances                                             | 64 |

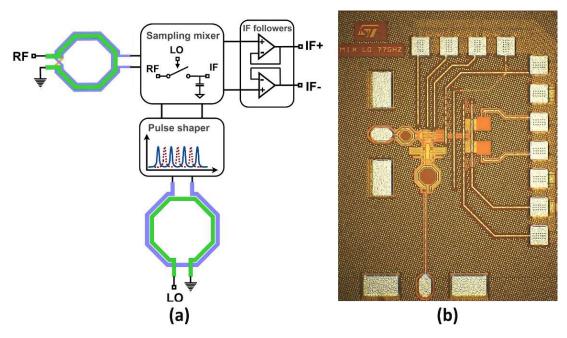

| 2.1 | 2 77 ( | GHz sampling mixer test chip                                         | 64 |

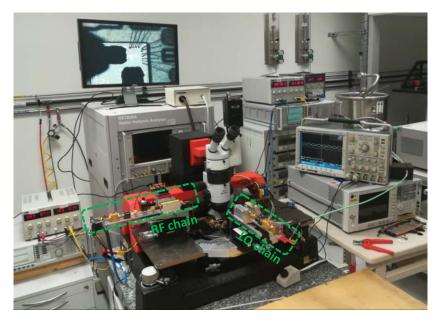

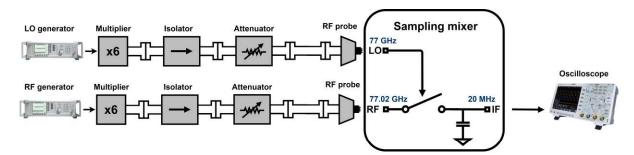

| 2.1 | 3 Mil  | limeter-wave measurement setup                                       | 65 |

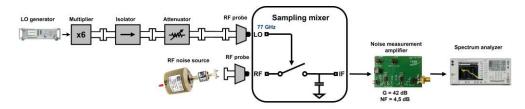

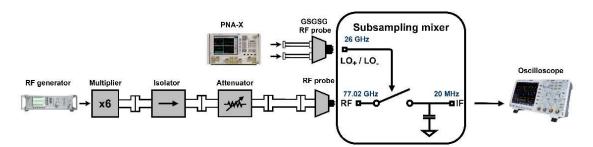

| 2   | .13.1  | Measurement bench description                                        | 65 |

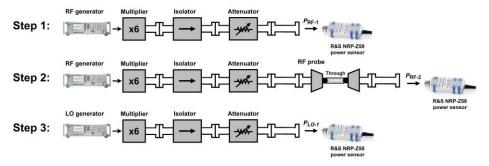

| 2   | .13.2  | Gain and linearity measurement setup                                 | 66 |

| 2   | .13.3  | Noise measurement setup                                              | 68 |

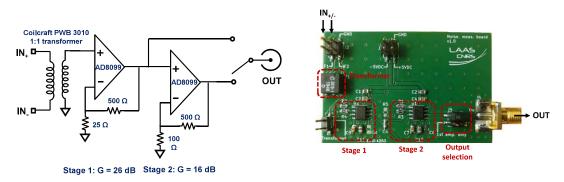

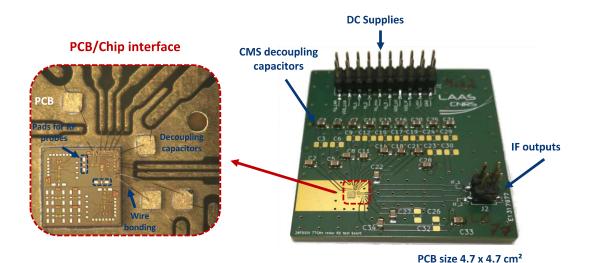

| 2.13.4    | PCB test board and chip mounting                             | 69  |

|-----------|--------------------------------------------------------------|-----|

| 2.14 77   | 7 GHz sampling mixer measurement results                     | 70  |

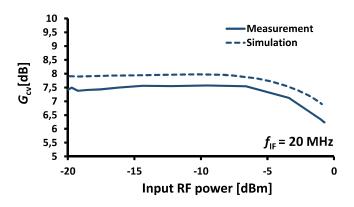

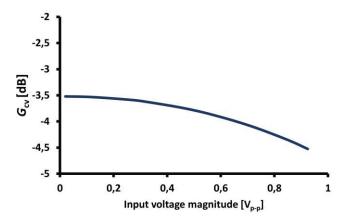

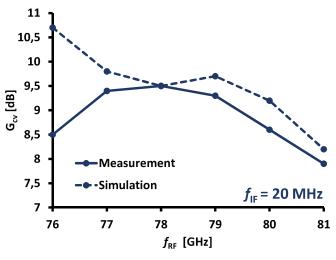

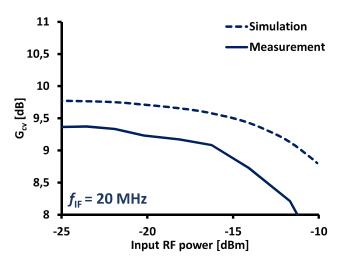

| 2.14.     | 1 Conversion gain and linearity                              | 70  |

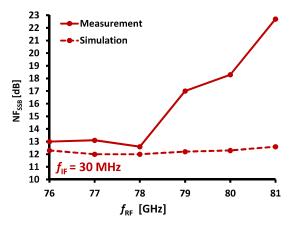

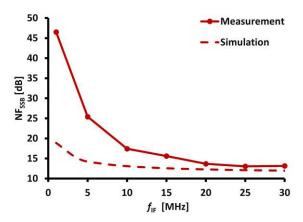

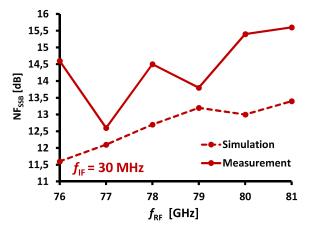

| 2.14.2    | Noise figure                                                 | 71  |

| 2.15 Pe   | erformance summary and conclusion                            | 73  |

| Chapter 3 | 1 1 5                                                        |     |

|           | nology                                                       |     |

|           | xisting topologies of millimeter-wave sub-harmonic mixers    |     |

| 3.2.1     | Active Gilbert cell-based sub-harmonic mixers                |     |

| 3.2.1     |                                                              |     |

| 3.2.3     |                                                              |     |

| 0         | ub-sampling mixer operating principle                        |     |

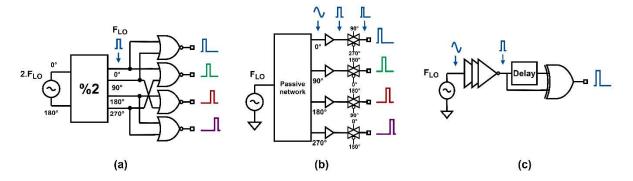

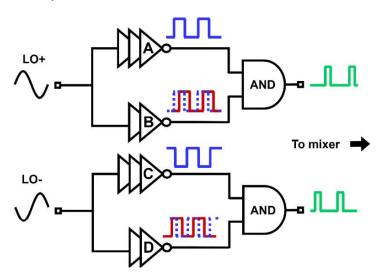

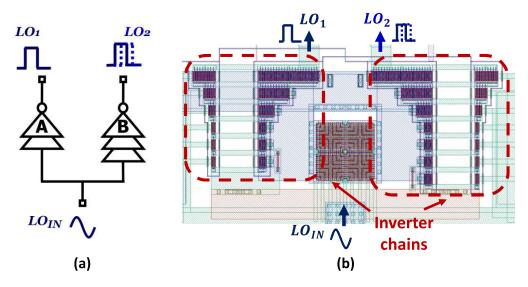

|           | 6 GHz LO pulse shaper based on logic gates                   |     |

| 3.4.1     | Pulse shaper architecture                                    |     |

| 3.4.2     |                                                              |     |

| 3.4.3     | Generated LO waveforms                                       |     |

|           | ub-sampling mixer core implementation                        |     |

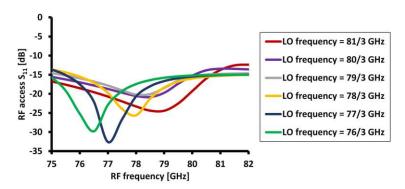

| 3.5.2     | RF and LO input matching                                     |     |

| 3.5.3     | -                                                            |     |

| 3.5.4     | -                                                            |     |

|           | ub-sampling mixer topology with co-integrated AND gates      |     |

| 3.6.1     | Overcoming the frequency limitation of the LO pulse shaper   |     |

| 3.6.2     |                                                              |     |

| 3.6.3     | -                                                            |     |

| 3.6.4     | Standalone mixer simulated performances                      |     |

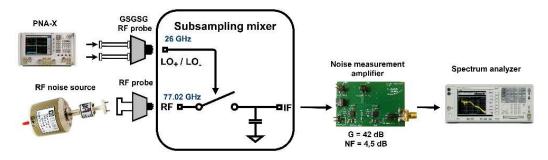

| 3.7 M     | Im-wave measurement setup                                    |     |

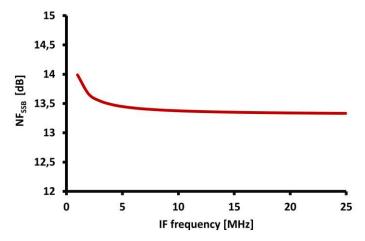

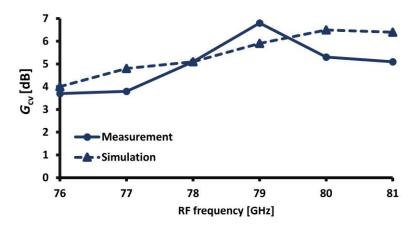

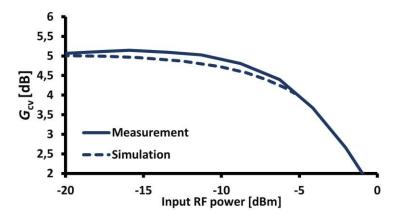

| 3.8 M     | leasurement results of the 77 GHz sub-sampling mixers        | 96  |

| 3.8.1     | Conversion gain and linearity                                | 96  |

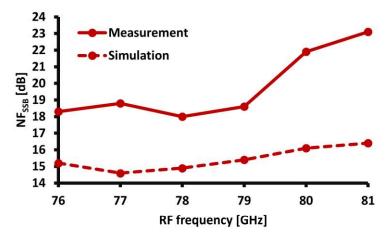

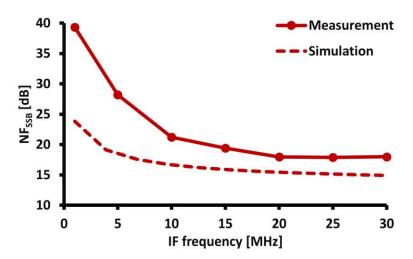

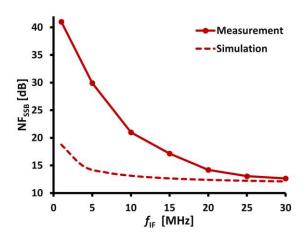

| 3.8.2     | Noise figure                                                 | 98  |

| 3.8.3     | Performance summary and conclusion                           | 101 |

| 3.8.4     | Discrepancies between simulated and measured NF for sub-samp |     |

|           |                                                              | 102 |

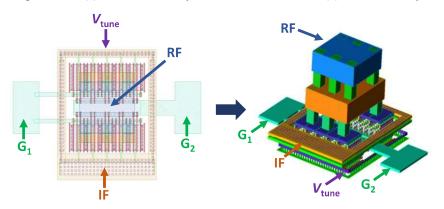

| Chapter technology | 1 0                                                             |     |

|--------------------|-----------------------------------------------------------------|-----|

| 4.1                | Design of a 77 GHz automotive radar receiver                    | 105 |

| 4.1.               | .1 Introduction                                                 | 105 |

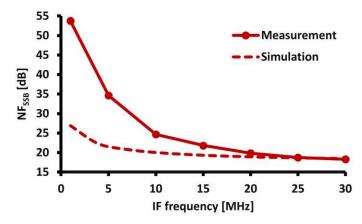

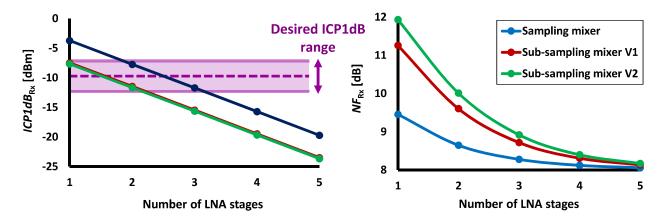

| 4.1.               | .2 Noise and linearity of a RF receiver                         | 105 |

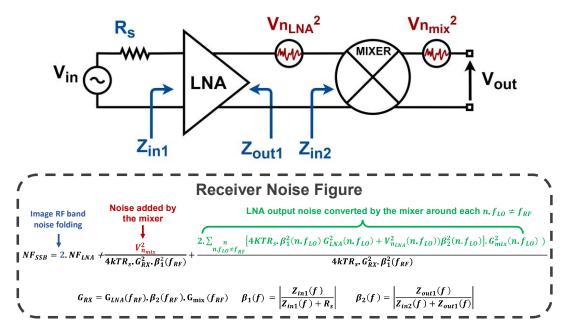

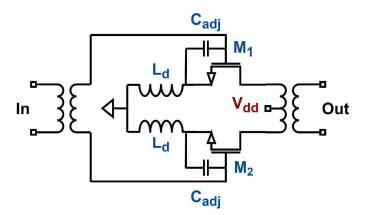

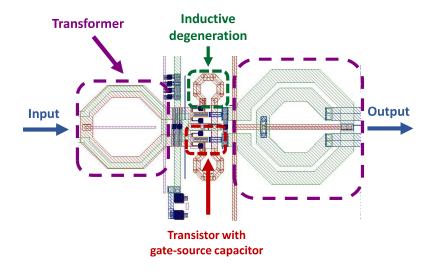

| 4.1.               | .3 Description of the 77 GHz LNA                                | 107 |

| 4.1.               | .4 Choice of the number of LNA stages                           | 109 |

| 4.2                | 77 GHz receiver based on a sampling mixer                       | 111 |

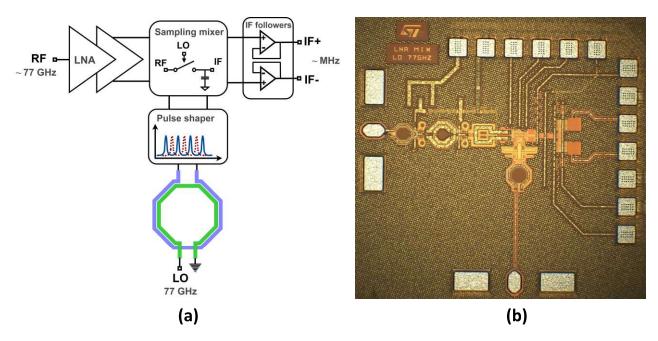

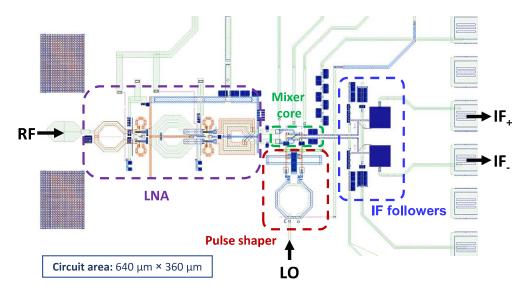

| 4.2.               | .1 Receiver architecture                                        | 111 |

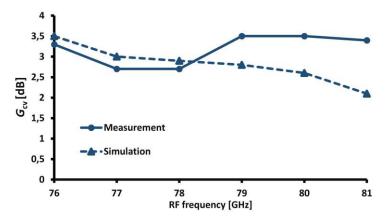

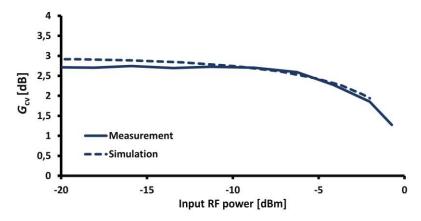

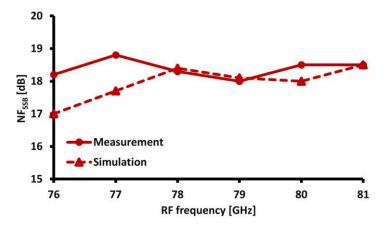

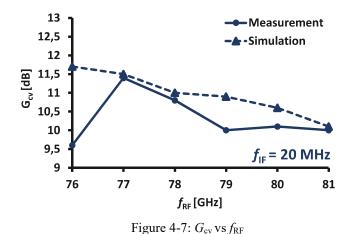

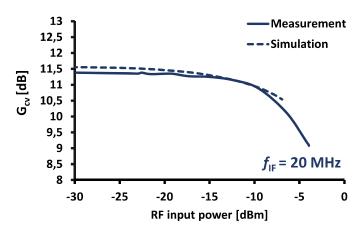

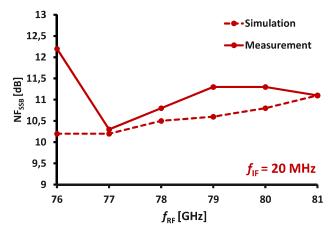

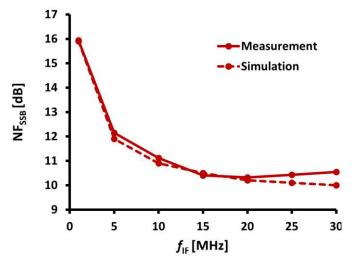

| 4.2.               | .2 Receiver measurement results                                 | 112 |

| 4.3                | 77 GHz receivers based on sub-sampling mixers                   | 115 |

| 4.3.               | .1 Receiver architecture                                        | 115 |

| 4.3.               | .2 Measurement results of the receivers                         | 116 |

| 4.4                | Comparison between the proposed sampling-based receivers and th |     |

| 4.5                | Conclusion                                                      | 126 |

| General            | l conclusions                                                   | 127 |

| Publicat           | tions                                                           | 131 |

| Annex:             | Sampling mixer thermal noise calculation                        | 133 |

| REFER              | ENCES                                                           | 137 |

# Acknowledgments

The work presented in this PhD thesis comes from a CIFRE partnership between STMicroelectronics and the LAAS-CNRS.

First of all, I would like to thank my advisors Christophe Viallon, Thierry Parra and Philippe Cathelin, for making these 3 years a very nice experience. I really appreciated their amazing support and their huge involvement. By showing a lot of interest and proposing very interesting ideas they made me really enjoy this project and learn a lot.

I also thank all my friends and colleagues from the MOST team of the LAAS and the RF design team of ST Crolles for all the good moments spent with them. Also a big thank for all those who helped me in my work by providing advices or helping me in the assembly and test of my circuits.

Finally I would like to thank the jury, Nathalie Deltimple, Sylvain Bourdel and Jean Gaubert, for showing interest for this research work and for taking the time to review this thesis.

# **General introduction**

From the first generation of vehicles, including a few comfort driving assistance options, to semi-automated driving features like automatic emergency braking or lane keep assistance, the driving assistance products have been continuously improved in the past few decades. Nowadays, the brand-new vehicles include ultrasonic sensors, camera, Radar and Lidar to ensure object detection all around the car under any conditions, paving the way for a full autonomous driving. To detect potential threat, the automotive radar emits a high-frequency electromagnetic wave which is reflected on the surrounding objects. Then, the radar sensor receives and analyses the reflected signals to calculate the speed, range and direction of the obstacles. With its ability to detect distant targets under harsh visibility conditions, the 77 GHz automotive radar plays a key role in driving safety.

Millimeter-wave frequencies enable a better circuit integration and good radar resolution on the target speed and range. This is also a challenge for circuit designers who must deal with stringent requirements especially on the receiver front-end. The main challenge is the trade-off between noise and linearity. An automotive radar must cope with multiple signal reflections that desensitize the receiver if its linearity is not high enough. At the same time, a too high noise level limits the receiver distant targets detection. These requirements are not easily compatible because a high-gain low noise amplifier will improve noise performances but will degrade linearity, as the mixer that follows will be saturated earlier. Consequently, the mixer design is important to find a good trade-off between noise and linearity.

First 77 GHz radar receivers were manufactured with SiGe BiCMOS processes benefiting from the high transition frequency and high breakdown voltage of Hetero-junction Bipolar Transistors. Good results have been achieved with active-mixer-based architectures, but these technologies suffer from high power consumptions, limited integration capacity and large production cost. More recently, the scaling down of CMOS processes makes CMOS a good candidate for 77 GHz circuit design, especially when cost target requires single chip solutions. The literature related to CMOS radar receivers highlights that receivers based on BiCMOS architectures show poor performances. The aim of this work is to demonstrate that

performances of 77 GHz CMOS receivers can be enhanced using CMOS specific technics, such as sampling and the use of high-speed digital gates. In this work, two innovative radar receiver architectures based on the sampling mixer principle are proposed. The first one shows that this principle can be extended to millimeter-wave frequencies to benefit from a very good noise/linearity trade-off. The second architecture uses this principle to convert a 77 GHz RF signal by using a 26 GHz LO frequency thus simplifying the LO distribution chain of the receiver.

The background of this study is presented in the chapter 1. First, the automotive radar application is introduced by explaining the 77 GHz radar operating principle and design specificities. Then the 28-nm FD-SOI CMOS technology used for the integrated RF circuit design in this work is presented. Finally, the different existing CMOS radar receiver design solutions will be presented and discussed to highlight the more appropriate architecture for the integration of a 77 GHz radar receiver in a 28-nm FD-SOI CMOS technology. The chapter 2 describes the sampling mixer principle and the implementation of a 77 GHz sampling mixer based on a new 77 GHz LO pulse shaper. The measurement setup and associated measured performances are reported at the end of this chapter and validate the interest of this new mixer topology. Then, a sub-sampling mixer topology allowing to down-convert an RF signal around 77 GHz using a 26 GHz LO frequency is detailed in the chapter 3. Measured performances confirm the good capabilities of the sub-sampling principle. The chapter 4 draws the conclusion of this study by showing the implementation of the proposed sampling-based mixers with a low noise amplifier in 77 GHz front-ends. These receiver architectures are compared with the state of the art highlighting the strengths and weaknesses of the proposed solutions. All the results of this study demonstrate that using sampling down-conversion can be the good choice to address millimeter-wave frequency applications.

# Chapter 1 The 77 GHz radar for automotive applications

### 1.1 Introduction

The acronym RADAR stands for "RAdio Detection And Ranging". In a radar sensor, an electromagnetic wave is generated and emitted by an antenna. Then, this signal is reflected by the surrounding objects and received by the radar sensor. Analysing the properties of the reflected signals allow to detect surrounding objects and calculate their speed, range and direction.

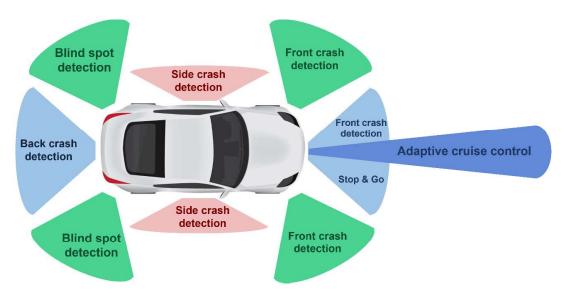

In the past few decades, the growing concern about driving safety is challenging the automotive industry with the need of very efficient driving assistance products. Therefore, Automotive manufacturers started to include radar sensors into their vehicles. The first generation of cars integrating radar sensors only benefited from a few comfort options as adaptive cruise control and parking assist [1, p. 17]. From the first cars including these features, the driving assistance has been continuously evolving to reach different level of automation. Nowadays, new cars benefit from a lot of new features as for example self-parking, blind spot detection or emergency braking [2],[3]. This partial driving automation paves the way for a full autonomous driving in the coming years. To reach this level of automation, a full coverage detection around the car is required [3] as described in Figure 1-1. To cover every angle around the car more radar sensors will be required in the next car generations. Furthermore, as each kind of sensor has its strengths and weaknesses, the automotive radar must be combined with other driving safety sensors to be able to prevent crashes under any conditions.

Figure 1-1: Detection coverage in the next generation of cars.

# 1.2 The radar among the driving assistance sensors

The object detection for driving safety generally relies on four different detection principles: Ultrasound, radar, camera and lidar [4]. The advantages and drawback of each kind of sensor ([3], [5]) are summarized in the Table 1-1.

|            | Ultrasound                                                     | Camera                                                                      | Radar                                                            | LiDAR                                                    |

|------------|----------------------------------------------------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------|

| Strengths  | Range detection                                                | Object recognition                                                          | <ul><li>Range/speed detection</li><li>Weather immunity</li></ul> | <ul><li>Range/speed detection</li><li>Accuracy</li></ul> |

| Weaknesses | <ul><li>Limited range</li><li>No speed<br/>detection</li></ul> | <ul><li>Limited range/</li><li>no speed detection</li><li>Weather</li></ul> | Ghosts target                                                    | • Weather                                                |

| Cost       | Low                                                            | low                                                                         | moderate                                                         | High                                                     |

Table 1-1:Comparison of automotive detection sensors.

Ultrasonic sensors are the best solution for close objects detection as they are well mastered and low cost, but they are too sensitive to weather and have a too limited range to address other applications. Nowadays, the use of camera for automotive application is widespread as they

are low cost, easy to implement and can recognize colours and objects. Nevertheless, cameras are very sensitive to weather and cannot efficiently assess the speed and range of a target. With its ability to detect the range, speed and direction of a distant target under any weather condition, the radar sensor plays a key role in driving safety. The weaknesses of radar sensors are the potential wrong detection caused by ghost targets [6] and cost which remains significantly higher than ultrasound sensors or cameras. Finally, Lidar sensors based on the laser detection are also able to detect the range, speed and direction of a target and have the best accuracy among automotive sensors. Lidar sensors are not currently widespread because of production cost. To reach the next level of driving automation, a combination of these detection principles will be used. With its substantial benefits, the radar sensors will play a key role in driving safety in the upcoming years.

#### 1.3 Basics of the automotive radar

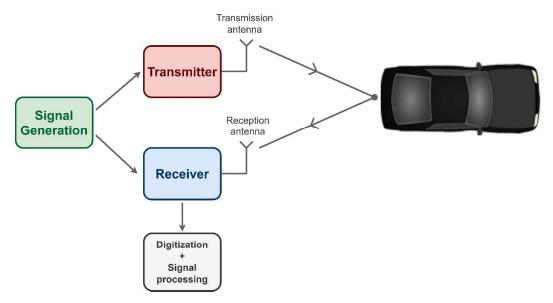

To assess the distance to surrounding objects, the radar sensor must be able to generate and transmit a high frequency signal, and then must be able to receive the reflected signal and to perform its analysis. The Figure 1-2 is a simplified block diagram of an automotive radar transceiver showing the required functions.

Figure 1-2: Simplified block diagram of an automotive radar transceiver.

A radar transceiver includes an oscillator to generate a high-frequency signal which is amplified by the transmitter and emitted by an antenna. Then the reflected signal is received by the reception antenna. The receiver down-converts the frequency of the received signal from millimeter-wave frequencies to a few MHz to be able to digitize this signal. The signal generated by the oscillator is also used in the receiver to perform the frequency translation. Finally, the received signal is converted into a digital information by the Analog-to-Digital Converter (ADC). The signal processing on the digital side allows the extraction of all the information required for the driving assistance.

The radar emitter also modulates the emitted signal. As a result, a radar sensor can emit different kinds of signal. The simplest signal waveforms used for radar detections are the pulsed and the continuous waveforms. The first one allows to easily calculate the target range by analysing the time of flight while the second one is suited to detect the target speed by analysing the doppler frequency shift. However, range detection using a continuous wave and speed detection using a pulsed waveform are difficult [1, p. 10 to 15]. To be able to compute the target speed and range at the same time, more elaborate modulations are needed.

## 1.4 The FMCW modulation

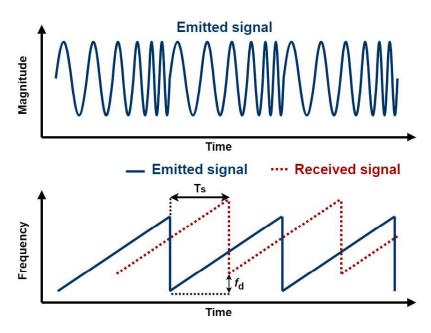

The most popular frequency modulation in automotive radars is the Frequency Modulated Continuous Wave (FMCW). This modulation based on a sine wave with a linear frequency variation versus time is described in Figure 1-3. Different patterns of frequency variation versus time can be used for FMCW, but the saw-tooth shape depicted in Figure 1-3 is the more used for automotive application [7], [8]. This figure shows the time-domain transient waveform of the modulated carrier as well as the frequency shift over time. The FMCW modulation is very simple compared to the modulation used in communication systems and allows to easily compute the target speed and range at the same time. Figure 1-3 (b) shows the frequency variation versus time for both emitted and received modulated signals.

Figure 1-3: Magnitude and frequency variations over time of sawtooth shaped FMCW signal

The comparison of the two signals gives access to the time between the emitted and received modulation patterns  $T_s$  and to the Doppler frequency shift  $f_d$ . The information on  $T_s$  allows to compute the target distance while the  $f_d$  gives access to the target speed [1, p. 14]. When several receivers are implemented in a radar module, comparing the phase shift between the signal received by each receiver allows to compute the direction of the target [9].

Considering a FMCW modulation with a linear frequency variation between  $f_1$  and  $f_2$ , the modulation bandwidth (B) is  $f_1 - f_2$  and the modulated carrier ( $f_c$ ) is ( $f_1 - f_2$ )/2. In a FMCW modulation the range resolution is proportional to 1/B while the speed resolution is proportional to  $1/f_c$  [1, p. 14],[7], [8]. As a result, a high frequency carrier associated to a wide modulation bandwidth is required to provide an accurate radar detection.

# 1.5 Frequency band allocation

As previously stated, the FMCW modulation principle requires a high modulation carrier frequency and a large bandwidth to benefit from a high accuracy. Furthermore, the radar transceivers must emit in unlicensed frequency bands to avoid interferences with communication devices. The organizations in charge of the frequency allocation in Europe and USA respectively the European Telecommunications Standards Institute (ETSI) and the

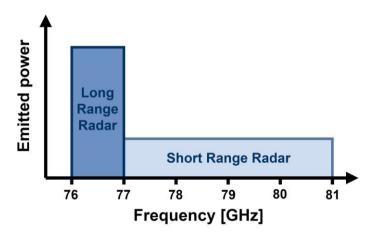

Federal Communications Commission (FCC), have dedicated a specific band for automotive radar application. This frequency band is located between 76 GHz and 81 GHz [10]. As efficient and cost-effective integrated circuits design was difficult to achieve at such high frequencies until recently, the FCC and ETSI had allocated temporary frequency bands around 24 GHz to let enough time to manufacturers to get proper 77 GHz radar transceivers. Nowadays, the development of 77 GHz radar products is well mastered and the 24 GHz frequency band will not be available after the first quarter of 2022. The definitive spectrum allocated to automotive radars is depicted in Figure 1-4.

Figure 1-4: Allocated frequency spectrum for automotive radar.

The 76-81 GHz automotive radar frequency band is divided in two parts with different specifications. The first one between 76 GHz and 77 GHz is dedicated to the long-range radar which is in front of the car for adaptive cruise control. In this frequency band an important emitted power is allowed to be able to reach distant targets thus providing a high detection range (up to 250m) [1, p. 18]. The band between 77 GHz and 81 GHz is dedicated to the short-range radar which does not need high power to cover a short range (<30m) but requires a large bandwidth to reach a fine range resolution.

As a conclusion, the unlicensed band around 77 GHz allocated to automotive radar application appears as an ideal choice providing a fine accuracy detection thanks to an high frequency carrier and a large modulation bandwidth. Nevertheless, using a such high frequency is also a challenge for circuit designers who must face stringent requirements especially on the receiver front-end (LNA+mixer). The next sections will describe the 77 GHz radar receiver architecture and the associated design constraints.

### 1.6 Automotive radar receiver architecture

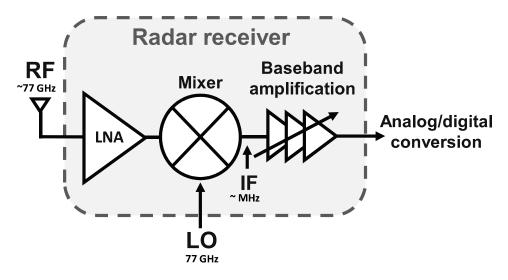

As previously stated, the role of the radar receiver is to convert an RF frequency received by the antenna around 77 GHz to a low enough Intermediate Frequency (IF) (a few MHz) to enable the signal digitization by an ADC. The different functions needed in a conventional radar receiver architecture serving this purpose are described in the Figure 1-5.

Figure 1-5: Conventional Radar receiver architecture.

The first stage of a radar receiver is generally a Low Noise Amplifier (LNA) which amplifies the weak received signal without degrading too much the Signal to Noise Ratio (SNR). Then the mixer down-converts the received RF signal around 77 GHz to a few MHz one by using the 77 GHz signal from the Local Oscillator (LO). After the frequency conversion, the signal centered at the IF frequency is amplified by Variable Gain Amplifiers (VGA) to ensure a voltage swing of constant magnitude at the input to the ADC.

# 1.7 Requirements on the receiver design

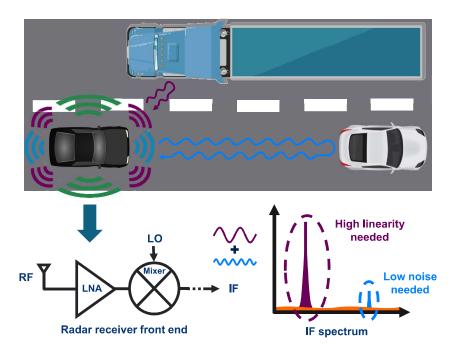

To ensure driving safety, 77 GHz radar receivers must be able to detect distant targets without being too sensitive to multiple signal reflections. Origins of the performance requirements for the radar receiver noise and linearity are illustrated in Figure 1-6.

Figure 1-6: Illustration of performance requirements for automotive radar receivers.

The power reflected by a distant target (the car in Figure 1-6) is generally very weak and can be too close to the receiver noise floor to be properly detected. As a result, a too high Noise Figure (NF) in a radar receiver will limit its ability to detect distant targets.

On the other hand, a signal reflected by a close target or a large vehicle (a truck in Figure 1-6) is resulting in an important power level at the receiver input. If the receiver is not linear enough, harmonics due to the distortion or intermodulation products with other reflected signals can be generated. Because the differentiation between these parasitic spurious and signals related with distant targets (the car in Figure 1-6), can be difficult, the non-linearity of the receiver can lead to wrong detections.

Thus, the most important metrics in a radar receiver are the NF representing the receiver ability to keep a good SNR and the 1-dB Input Compression Power (ICP1dB) traducing the receiver linearity. Nevertheless, a good NF is not easily compatible with a high ICP1dB. The mixer, with its highly non-linear behavior, is the main limiting stage regarding the receiver linearity. As a result, a high-gain LNA improves noise performances but also degrades linearity, as the mixer is exposed to higher voltage swing for the same power received by the antenna. On the other hand, limiting the LNA gain enhances the linearity, but in agreement

with the Friis theorem, noise contributions of the blocks following the mixer (VGA, Filter, ADC) are increased.

As a conclusion, the balance in gain repartition in the different stages is the key to find the best trade-off between noise and linearity, while preserving cost (area) and power consumption. The analysis of existing CMOS radar receivers coming later in this chapter will give a detailed illustration of this aspect. The mixer linearity, which can force to limit the LNA gain, is essential in the overall chain performance. Consequently, it is the main topic addressed in this manuscript.

#### 1.8 Evolution in automotive radar

First works on 77 GHz automotive radars were reported between 1995 and 2000. At that time, only III-V technologies were efficient enough to address such high frequencies. Consequently, the first reported integrated transceivers for 77 GHz radar applications were manufactured using Ga-As processes [11].

Some years later, the increase in the performances of SiGe processes became good candidates to design millimeter-wave integrated circuits. With lower production costs, silicon processes were more appropriate than III-V processes for consumer applications. First SiGe BiCMOS circuits for automotive radar have been published around 2005 [12]–[14]. Then, these processes were selected to manufacture the first 77 GHz radar products.

As already stated, the first generation of cars integrating 77 GHz radar only included a few radar sensors. More radar sensors and a more advanced signal processing will be required in the upcoming years to cover every angle around the car and enable a semi-automated driving. The analysis performed in [15] shows that CMOS technologies, while offering too poor millimeter-wave performances in the early 2000s, have been continuously scaled down to finally reach high enough transition frequencies ( $f_t$ ) to allow 77 GHz circuits design. With a better circuit integration and lower production costs, CMOS processes seem now far more appropriated than BiCMOS technologies to design the next generation of 77 GHz radar transceivers. CMOS processes will enable the Radar sensor multiplication in a car without

leading to prohibitive costs. It will also make easier the signal processing co-integration with the transceiver.

# 1.9 28-nm FD-SOI CMOS technology description

The 28-nm FD-SOI technology developed by STMicroelectronics has been selected for this work. This process offers Fully Depleted Silicon On Insulator (FD-SOI) CMOS transistors with a 28-nm minimum transistor gate length. With nm-scaled CMOS transistors benefiting from  $f_t$  and  $f_{max}$  higher than 300 GHz this technology is well suited for low power millimeterwave frequencies integrated circuits design [16].

#### 1.9.1 FD-SOI CMOS transistor

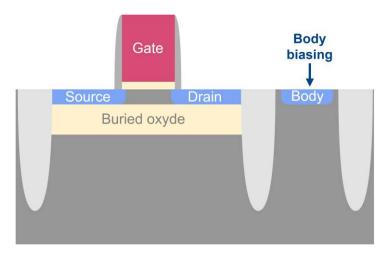

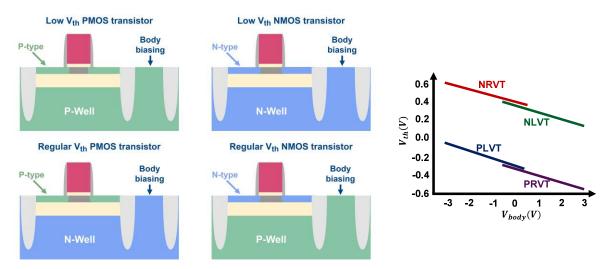

The main specificity of this technology is the FD-SOI CMOS transistor. A cross section of a FD-SOI CMOS transistors is described in Figure 1-7.

Figure 1-7: FD-SOI CMOS transistor cross section.

In FD-SOI technologies, the ultra-thin buried oxide layer (25-nm) present under the CMOS transistor channel offers many benefits. The manufacturing process is simpler than a conventional bulk process as fewer masks are required [16]. The electrical performances are also improved. As the transistor channel is insulated with this buried oxide, current leakages are reduced and the electrostatic channel control becomes easier.

An important feature resulting from the channel insulation by the buried oxide is the body biasing. In a conventional bulk process, there is not much flexibility to set the transistors body voltage. For a PMOS on a bulk substrate,  $V_{\text{body}}$  must remain above Drain and Source voltages, to keep Drain-to-body diode reverse-biased. This is generally achieved by either connecting body to  $V_{\text{DD}}$  or to Source. For the NMOS, unless the transistor is insulated by a triple well, the body is tied to bulk and thus to ground. In FD-SOI technologies, a voltage can be applied under the transistor channel (Figure 1-7) to provide an additional channel control. This way, the body access acts as a second gate at the back of the transistor channel. As a result, applying a voltage to the transistor body allows to change the transistor threshold voltage ( $V_{\text{th}}$ ). The insulation of the conducting channel also makes possible to use N or P type doping below the transistor leading to different nominal  $V_{\text{th}}$  values. This principle is used in the 28FDSOI technology to propose 4 different CMOS transistor "flavours" [16] as described in Figure 1-8.

Figure 1-8: different transistor flavours proposed in 28FDSOI and their Body-bias characteristic.

As described Figure 1-8 using the same type of doping for the conducting channel and under the box offers CMOS transistors with low nominal  $V_{th}$  value (NLVT and PLVT). Moreover, using the opposite doping leads to CMOS transistors with regular  $V_{th}$  nominal value (NRVT and PRVT). These different configurations offer four transistor flavours. For each transistor type, the  $V_{th}$  value can be tuned around the nominal value with the body biasing by setting the voltage applied to the hybrid zone ( $V_{body}$ ). This technology exhibits a quite high body factor (~85 mV/V) enabling a large  $V_{th}$  tuning range. This body biasing capability in FD-SOI technologies provides new design opportunities by controlling the CMOS transistors  $V_{th}$ .

The high-speed CMOS transistors have a thin gate oxide and operate under a nominal  $V_{\rm DD}$  value around 1V. The 28FDSOI process also offer LVT and RVT CMOS transistors with a thick gate oxide able to operate under 1.5 V or 1.8 V nominal  $V_{\rm DD}$  value. Nevertheless, thick gate oxide transistors exhibit lower  $f_{\rm t}$  and  $f_{\rm max}$ .

#### 1.9.2 Metal stack

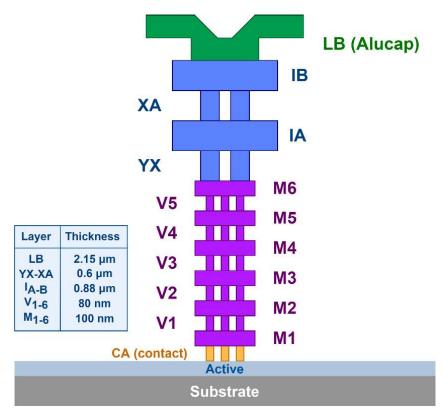

The 28FDSOI technology provides different metal stack configurations. The selected configuration is described in Figure 1-9.

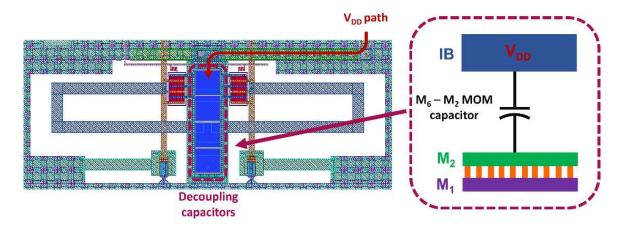

Figure 1-9: 28FDSOI 8 metal levels stack.

The metal stack includes 8 metal layers and an "Alucap" top level. The metal layers  $M_1$  to  $M_6$  are quite thin (100 nm) and are often used for active components routing. Thicker metallization are available from the top metal layers (IA and IB) with the alucap LB. They are used for passive structures such as inductances or transmission lines as they are less resistive than underneath layers. These higher levels are also less sensitive to parasitic coupling to the ground plane or substrate.

## 1.9.3 Passive components

MIM and MOM capacitors are available for RF designs with the 28FDSOI technology. The MIM capacitors are located between the two thick metal layer (IA and IB) and show a capacitance density around 20 fF/ $\mu$ m<sup>2</sup>. The MOM capacitors are implemented from metal layers  $M_1$  to  $M_6$  and offer a capacitance density around 6 fF/ $\mu$ m<sup>2</sup>. As the MIM capacitors option requires additional masks, MOM capacitors with an RF compliant layout should be preferred for low-cost RF design.

The 28FDSOI also provides different kinds of resistors. A P+ doping poly-silicon resistor with a 439  $\Omega$ /square density is preferred for RF design as it lead to the best RF performances.

#### 1.10 77 GHz radar receiver architectures

Many different architectures of millimeter-wave receiver front-ends related to 77 GHz CMOS radar receivers have been published so far in the literature. The main differences between existing solutions come from the mixer topology used to down-convert the 77 GHz RF signal. Since the choice made in the mixer topology have a strong impact on the overall receiver design, the main existing configurations are discussed and compared in this section. The goal is to find the more suitable architecture to design a 77 GHz radar receiver in a 28-nm FD-SOI CMOS technology.

#### 1.10.1 Radar receivers based on active mixers

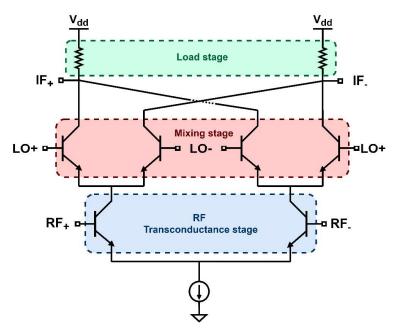

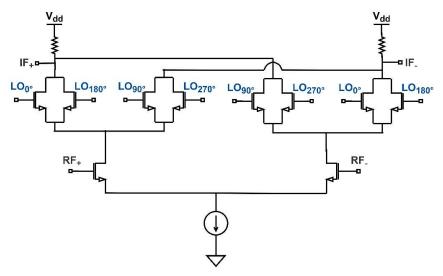

First silicon 77 GHz radar receivers were manufactured with SiGe BiCMOS processes benefiting from the high transition frequency and high breakdown voltage of Hetero-junction Bipolar Transistors (HBT). The more spread 77 GHz BiCMOS receiver architecture is based on the Gilbert Cell [17] described in Figure 1-10.

Figure 1-10: Conventional double-balanced Gilbert cell.

The gilbert cell is an active mixer topology stacking a differential RF transconductance amplifier and a double-balanced mixing stage loaded by resistors thus allowing to design extremely compact mixers. In the Gilbert cell, some conversion gain is provided by the RF transconductance and resistors. Therefore, this kind of mixer does not always require a LNA. The main drawback of the gilbert cell is the linearity which remains limited by two factors. The first contributor to the linearity degradation in Gilbert cells is the RF transconductance stage as the HBT differential pair can handle a very limited input voltage swing (a few  $U_t$ ) without saturating. Furthermore, using three vertical stages (transconductance, mixing cell and loads) results in a low voltage headroom for each stage thus restraining the output voltage swing.

The conventional Gilbert cells is implemented in the first generation of BiCMOS 77 GHz receiver demonstrator as in [18]. In this work, the proposed mixer operates under a 2.5 V supply showing a good trade-off between noise and linearity. Nevertheless, the work in [19]–[21] demonstrates a better linearity by using a folded topology or removing the RF transconductance of the Gilbert cell. This approach seems to be the most suitable for the design of BiCMOS 77 GHz radar receivers and lead to very high performances on the noise/linearity trade-off in [19]–[21].

As architectures based on active mixers translates into high performances with BiCMOS processes, active topologies have been firstly implemented in 77 GHz CMOS receiver test chips. The Table 1-2 summarizes the performances of the existing CMOS radar receivers relying on active mixers ([22]–[26]) and compares them to their BiCMOS counterpart.

Table 1-2: performances of Gilbert-cell-based 77 GHz receiver front-ends in silicon technologies.

| Ref  | Tech             | Topology                                               | Gain<br>[dB]            | ICP1dB<br>[dBm]          | NF <sub>SSB</sub> [dB] | V <sub>DD</sub><br>[V] | P <sub>dc</sub> [mW] |

|------|------------------|--------------------------------------------------------|-------------------------|--------------------------|------------------------|------------------------|----------------------|

| [18] | 130-nm<br>BiCMOS | Gilbert cell                                           | 15                      | -13                      | 13.8                   | 2.5                    | 335                  |

| [19] | 130-nm<br>BiCMOS | Gilbert cell mixing stage only                         | 16                      | -2                       | 11-12                  | 3.3                    | 200                  |

| [21] | 180-nm<br>BiCMOS | Folded Gilbert cell                                    | 21.5                    | -5 10.8                  |                        | 3.3                    | 70                   |

| [22] | 65-nm<br>CMOS    | Gilbert cell                                           | 11.8                    | 11.8 -18* 1              |                        | 1.2                    | 8                    |

| [23] | 28-nm<br>CMOS    | 2-stage LNA<br>+<br>Gilbert cell mixing<br>stage       | 18 (LNA)<br>2 (mixer)   | -30* 12                  |                        | NA                     | 68                   |

| [24] | 65-nm<br>CMOS    | 3-stage LNA<br>+<br>folded Gilbert cell                | 31.6 (Rx)<br>5 (mixer)  | -37 (Rx)<br>-20* (mixer) | 8.8                    | 1                      | 61                   |

| [25] | 65-nm<br>CMOS    | 3-stage LNA<br>+<br>folded Gilbert cell                | 11                      | 11 -15                   |                        | 1                      | 22                   |

| [26] | 65-nm<br>CMOS    | 3-stage LNA (Tunable gain) + Gilbert cell mixing stage | 18/66 (Rx)<br>4 (Mixer) | -7/-31                   | 26/11                  | 1                      | 31                   |

<sup>\*</sup>estimated

Compared to the HBT of the SiGe processes the CMOS transistors have a lower voltage handling capabilities and lower  $g_m$  at high frequencies. Therefore, the comparison between the work in [22]–[26] and 77 GHz BiCMOS Gilbert cells highlights that a satisfying trade-off between noise and linearity cannot be reached with CMOS receivers based on active mixers. As a result, CMOS active mixers do not appear as the right choice for 77 GHz radar receiver.

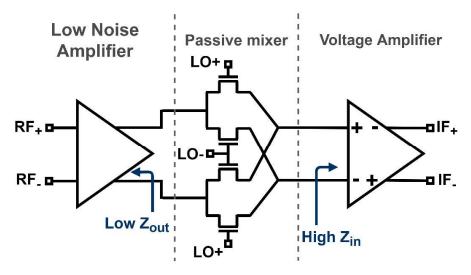

## 1.10.2 Radar receivers based on passive mixers

Even if CMOS transistors are not as efficient as HBT for active mixer topologies, they perform very well as switches. As a result, double-balanced passive mixers using four cold-biased CMOS transistors operating as switches are widespread in CMOS receiver design. Furthermore, CMOS processes scaling down drastically improves the performances of the CMOS switches. As the channel ON-state resistor  $r_{\rm on}$  of the transistor is proportional to the W/L ratio while the gate capacitance is proportional to W×L, decreasing L while keeping the same  $r_{\rm on}$  results in a significantly lower gate capacitance. Reducing the gate capacitance improves the CMOS switches performance by allowing the transistors to quickly switch between ON and OFF states.

Passive mixers are chosen for their good linearity and zero DC power consumption. Since the passive mixers high linearity allows to implement more gain on the LNA while keeping a suitable ICP1dB for the radar application, they appear as a good alternative to active mixers regarding noise performances of the receiver. Furthermore, as no DC current passes through the mixing transistors, passive mixers are also less sensitive to the 1/f noise than active mixers. On the other hand, passive mixers bring significant conversion losses thus requiring a LNA at the receiver input to avoid a receiver NF degradation.

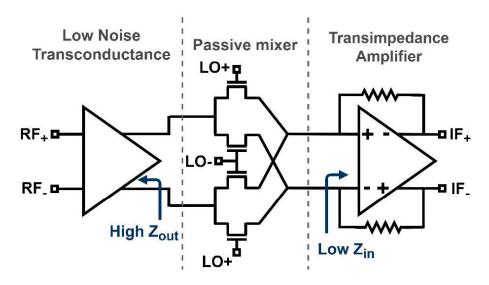

Passive mixers can be used in voltage or current mode depending on LNA and baseband amplifier topologies. Both operating modes are presented here below. When the passive mixer is implemented in a receiver between a low noise RF amplifier and an IF amplifier (IFA) showing respectively a low output impedance and a high input impedance (Voltage amplifier), the mixer operates in voltage mode (Figure 1-11).

Figure 1-11: Receiver architecture based on a voltage mode passive mixer.

When the same passive mixer is implemented between a RF low noise transconductance amplifier (LNTA) and an IF transimpedance amplifier (TIA) the input RF voltage is turned into a current by the first stage, passes through the mixer and is converted back to a voltage by the IF TIA. This operating principle is described in Figure 1-12 and is called current mode. A proper current transfer in the mixer requires a high output impedance for the RF LNTA while the IF TIA must present a low input impedance.

Figure 1-12: Receiver architecture based on a current mode passive mixer.

Both operating modes have strengths and weaknesses. In the voltage mode mixer, the condition for maximizing the voltage transfer and thus the conversion gain is:

$$|Z_{out_{INA}}| + r_{on} \ll Z_{in_{IFA}} \tag{1-1}$$

This requirement is quite easy to fulfil as the IFA input impedance is in the range of tens of  $k\Omega$ . For the current mode mixer, the condition to ensure a good current transfer through the mixer is:

$$|Z_{out_{INTA}}| \gg r_{on} + |Z_{in_{TIA}}| \tag{1-2}$$

This requirement is harder to fulfil because a low  $r_{\rm on}$  requires a large mixing transistor which can be hard to drive. In addition, a low TIA input impedance is hard to reach above a few MHz. Not meeting this requirement would results in extra conversion losses. On the other hand, using current rather than voltage in a millimeter-wave receiver can be very helpful to deal with the low supply voltage of the nm-scaled CMOS process. As using a current mode mixer results in a low voltage swing at the input of the mixer, the RF transconductance is less sensitive to voltage saturation coming with the low voltage supply. The low voltage swing at the input and output of the mixer also keeps the mixing transistor  $V_{\rm DS}$  close to 0 V increasing the mixer linearity.

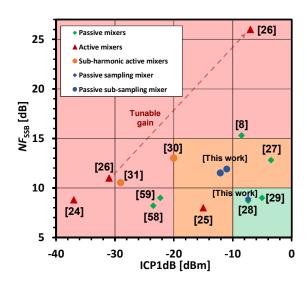

Both operating modes are present in the literature related to 77 GHz radar receivers. Receivers in [27], [28] rely on current mode passive mixers an exhibit excellent trade-offs between noise and linearity. In [27] a 1-stage LNA is used rather than a 2-stage LNA (as done in [28]) leading to a lower front-end gain. The reduced front-end gain is compensated by the higher gain of the IF TIA operating under a high voltage supply (1.8V vs 0.8V for RF blocks) to preserve the overall linearity. This strategy allows to reach a better ICP1dB at the cost of a higher NF. Voltage mode passive mixers are developed in [8] and [29] also showing a high linearity and a good NF. The work in [29] push the strategy used in [27] further by removing the LNA to propose a passive mixer first receiver showing an excellent linearity with a low NF. References [8], [27]–[29] present the best published 77 GHz CMOS radar receivers when considering the trade-off between noise and linearity. The performances of the receiver front-ends presented in this section are summarized in the following table:

| Ref  | Tech            | Topology                                            | Gain<br>[dB] | ICP1dB<br>[dBm] | NF <sub>SSB</sub> [dB] | V <sub>DD</sub> [V]      | P <sub>dc</sub><br>[mW] |

|------|-----------------|-----------------------------------------------------|--------------|-----------------|------------------------|--------------------------|-------------------------|

| [28] | 40-nm<br>CMOS   | LNTA + current mode passive mixer + TIA             | 17           | -7.4            | 8.7                    | 1.8                      | NA                      |

| [8]  | 65-nm<br>CMOS   | LNA + voltage mode passive mixer + IFA              | 26.2         | -8.5            | 15.3                   | 1                        | 78                      |

| [27] | 22-nm<br>FD-SOI | Common gate LNA  + current mode passive mixer + TIA | 16           | -3.5            | 12.8                   | 0.8/1.8<br>(RF/Baseband) | NA                      |

| [29] | 28-nm<br>CMOS   | Voltage mode passive<br>mixer first<br>+ IFA        | 15           | -5              | 9                      | 1.8                      | 100                     |

Table 1-3: performances of passive mixer-based 77 GHz CMOS receiver front-ends.

As passive mixers exhibit conversion losses, they are generally implemented with a LNA and/or an IFA in a whole front-end, whereas the Gilbert cell can be used in a standalone configuration. Therefore, standalone passive mixers are not represented in the publications related to the 77 GHz radar application making their performances hard to assess. Nevertheless, the performances of the 77GHz CMOS receivers reported in Table 1-3 demonstrate that using a passive mixer to design a 77 GHz radar receiver with nm-scaled CMOS processes appears as the right choice. As passive mixers rely on the CMOS transistor switching behaviour, which is the strength of nm-scaled CMOS processes, this approach allows to take the best from those technologies. It can be noticed that using a low front-end gain is the key to get a good linearity. If this gain is not high enough to prevent a too high noise contribution from the baseband VGA, an IF amplifier with a moderate NF can be used to compensate the low front-end gain. As CMOS processes generally offer thick gate oxide CMOS transistors with a higher breakdown voltage than RF transistors at the cost of a lower  $f_t$  the IF amplifier can operate on a higher voltage supply than for RF blocks as in [27]. This way, more gain can be introduced before the VGA without degrading the ICP1dB. This approach combined with the use of passive mixers seems to be the best way to design a high performances CMOS radar receiver.

#### 1.10.3 Radar receivers based on sub-harmonic mixers

All receiver architectures presented in previous sections are using a 77 GHz LO signal to drive the mixer. Implementing a 77 GHz Voltage Controlled Oscillator (VCO) is not the preferred solution for radar systems, because of the difficulties to design the VCO itself. Conventional radar architectures use a 38.5 GHz VCO followed by a frequency doubler and high consumption 77 GHz drivers ([26], [28]). Sometimes higher frequency multiplication factors as a tripler in [27] or a sextupler in [24] are implemented to relax the design complexity of the VCO and LO distribution chain. At the scale of a full radar chip including several receivers, this approach is a bit complex and results in extra power consumption and circuit area, as frequency multipliers rely on active blocks (push-push structures or equivalent) followed by LC tanks. The use of sub-harmonic mixers, using a LO frequency submultiple of the RF frequency ( $f_{\text{LO}} \approx f_{\text{RF}}/n$ , with n a natural integer), opens the way to get rid of multipliers. This solution has already been considered for the first generations of 77 GHz CMOS radar receivers ([30], [31]). The performances of the sub-harmonic receivers in [30], [31] are summarized in the following table:

| Ref  | Tech          | frf/flo<br>[GHz] | Topology                                                | Gain<br>[dB]                 | ICP1dB<br>[dBm]           | NF <sub>SSB</sub> [dB] | V <sub>DD</sub> [V] | P <sub>dc</sub><br>[mW] |

|------|---------------|------------------|---------------------------------------------------------|------------------------------|---------------------------|------------------------|---------------------|-------------------------|

| [30] | 65 nm<br>CMOS | 78 / 39          | 5-stage LNA + ×2 sub-harmonic Gilbert cell mixing stage | 16 (Rx)<br>6.2<br>(Mixer)    | -20 (Rx)<br>-10.2*(mixer) | 13                     | 1.2                 | 28.5                    |

| [31] | 65 nm<br>CMOS | 78 / 39          | 2-stage LNA + ×2 sub-harmonic folded Gilbert cell       | 14.5<br>(Rx)<br>2<br>(Mixer) | -16.2 (Mixer)<br>-28 (Rx) | 10.5                   | 1.5                 | 57                      |

Table 1-4: performances of sub-harmonic mixer-based 77 GHz CMOS receiver.

[30], [31] are the only existing works on 77 GHz CMOS sub-harmonic receivers. They are both based on ×2 CMOS sub-harmonic Gilbert cells which show limited performances compared to conventional solutions. However, the prospect of a simpler LO chain for 77 GHz radar transceiver let this approach appear as promising. Therefore, 77 GHz sub-harmonic receiver architectures will be considered in the chapter 3.

<sup>\*</sup>estimated

# 1.11 Conclusion

The main existing solutions for a 77 GHz radar receiver architecture have been discussed in this section. This discussion highlights that even if receivers based on active Gilbert cells show very good performances with BiCMOS technologies, active mixers are not suited for advanced CMOS technologies. On the other hands, CMOS passive mixers take advantages of the strength of CMOS processes leading to far better performances. Therefore, using passive mixer topologies appears as the best solution to design a 77 GHz radar receiver in 28-nm FD-SOI CMOS technology. The literature related to 77 GHz radar receivers also puts forward that a sub-harmonic mixer-based architecture is a solution to reduce the burden of the LO distribution chain in term of area and consumption. This solution thus proposes a better Noise/Linearity/Consumption/Area trade-off. This promising approach has not demonstrated state of the art performances yet but we strongly believed that, associated to an optimal mixer design, it can be the right choice for radar architectures. The purpose of this thesis is to demonstrate this statement.

# Chapter 2 Design of a 77 GHz sampling passive mixer in 28-nm FD-SOI CMOS technology

#### 2.1 Introduction

The state of the art presented in the previous chapter highlights that high performances are reached with passive mixers that provide high linearity and zero DC consumption [8], [27], [28]. The discussion on the noise/linearity trade-off in radar receivers (chapter 1) also puts forward that, as their high linearity allows to implement more gain on the LNA while keeping a good ICP1dB, they are also a good alternative to active mixers from the noise point of view. As these topologies rely on cold CMOS transistors used as switches, they allow to take the best from the recent nm-scaled CMOS processes. Thus, using passive mixers in a 28FDSOI radar receiver at 77 GHz appears as the best solution. First, this chapter presents the conventional CMOS voltage passive mixers operating principle highlighting their benefits and drawbacks. Then a new 77 GHz sampling mixer topology showing better performances is proposed. The aim of this chapter is to present a new solution enabling the use of sampling mixers at millimeter-wave frequencies. This solution is integrated in a 28FDSOI technology for an experimental validation of reachable performances.

# 2.2 Conventional CMOS passive mixers

As previously stated, CMOS passive mixers are well suited to design highly linear receivers with low power consumption. As, they use cold CMOS transistors, they are also particularly appropriated to nm-scaled CMOS processes, like 28FDSOI, because transistors of these technologies can behave as very good switches. The following section will introduce the operating principle of the conventional CMOS passive mixer and put forward its strengths and weaknesses.

#### 2.2.1 Operating principle

As discussed in the chapter 1, the conventional CMOS passive mixer can operate in current mode [27], [28] or voltage mode [8] depending on the impedance presented by the previous and following stages. This thesis focuses on sampling passive mixers relying a hold capacitor to store a sampled voltage value at the output of a voltage mode mixer. Therefore, the current mode passive mixer operating principle will not be detailed here-after.

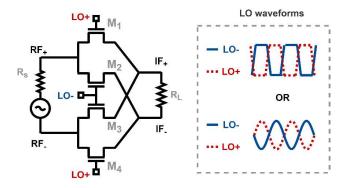

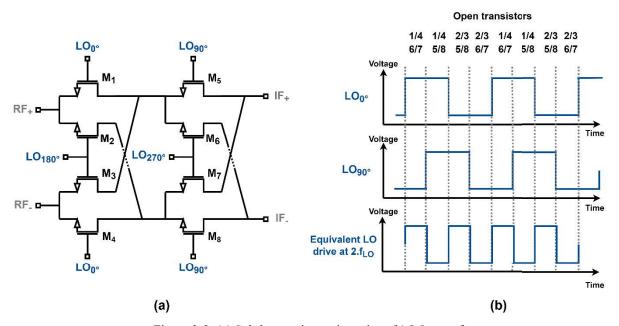

The principle of a conventional double-balanced voltage mode CMOS passive mixer is depicted in Figure 2-1. When compared to its single ended counterpart, it can be noticed that the double-balanced topology provides a good harmonic rejection and translates into a better conversion gain [32], [33, Ch. 6].

Figure 2-1: Conventional voltage double-balanced passive mixer.

As the high load impedance  $R_L$  results into a high mixer input impedance ( $\approx R_L$ ) the voltage transfer from an input voltage source with  $R_S$  far lower than  $Z_{in}$  is maximised. The mixer is acting as a proper voltage conveyor. The conventional voltage passive mixer is usually driven by a sinusoidal local oscillator waveform or a 50% duty cycle square wave [32], as described in Figure 2-1. The shape of the LO signal is depending on frequencies. It can be square when LO frequency is low enough, whereas it can be only sinusoidal at high LO frequency. In these conditions, the mixer output voltage is  $V_{RF}$  (RF+-RF-) in the first half of the LO period and  $-V_{RF}$  in the other half. The result is the conversion of the input signal at RF frequency to the output one at the Intermediate Frequency. The voltage conversion Gain ( $G_{cv}$ ), linearity and noise figure NF of a conventional passive mixer will be discussed in the following sections.

#### 2.2.2 Passive mixer conversion gain

Considering all mixing CMOS transistors  $M_{1,2,3,4}$  as voltage-controlled switches, with a  $r_{on}$  ON-state resistance, the voltage conversion gain of the passive mixer of Figure 2-1 is [32]:

$$G_{Cv} = \frac{2}{\pi} \cdot \frac{R_L}{R_L + r_{on} + R_S} \tag{2-1}$$

The theorical maximum value of this conversion gain  $G_{\rm cv}$  is reached for an ideal voltage matching ( $R_{\rm s}$  far lower than  $Z_{\rm in}$  and  $r_{\rm on}$  far lower than  $R_{\rm L}$ ) and is equal to  $2/\pi$  ( $\approx$  -4 dB).

#### 2.2.3 Noise in passive mixer

The main noise contributor in CMOS passive mixer is the thermal noise in the channel of the mixing transistors. The  $r_{on}$  ON-state resistance produces thermal noise which is converted to the mixer output. For this kind of mixer, the output voltage noise spectral density is [34]:

$$V_{nth}^{2} = 8KTr_{on} \tag{2-2}$$

In (2-2) K is the Boltzmann constant and T the ambient temperature. This result is easily understandable because a conventional CMOS passive mixer is driven by a 50% duty cycle LO waveform, and there is always a conductive path with two series  $r_{\rm on}$  between the input and the output.

The second important noise contribution is inherent to mixer principle. As the mixer converts RF signals from  $f_{LO} \pm f_{IF}$  to  $f_{IF}$ , the noise in both RF frequency bands is added a  $f_{IF}$ .

If we consider that the conversion gain is the same for both bands, the input noise is doubled when only one input frequency band is used.

Taking into account these contributions, the voltage passive mixer Single Side-Band Noise Figure ( $NF_{SSB}$ ) is:

$$NF_{SSB} = \frac{V_{\text{nmix}}^2}{4KTR_s. G_{\text{Cv}}^2 \alpha^2} \quad with \ \alpha = \left| \frac{Z_{in}}{Z_{in} + R_s} \right|$$

(2-3)

$$NF_{SSB} = \frac{8KTr_{on} + 2.(4KTR_s.G_{cv}^2.\alpha^2)}{4KTR_s.G_{cv}^2.\alpha^2} = 2 + \frac{8KTr_{on}}{4KTR_s.G_{cv}^2.\alpha^2}$$

(2-4)

In (2-4),  $G_{cv}$ ,  $Z_{in}$  and  $V_{nmix}$  are respectively the voltage conversion gain, the input impedance and the output noise voltage of the mixer, and  $R_s$  is the series impedance of the input RF source. Expression (2-4) shows that the minimum value of  $NF_{SSB}$  is 3 dB, when the mixer is noiseless. The additional noise resulting from the mixer depends on the  $r_{on}$  resistance and the conversion gain:  $NF_{SSB}$  increases with the  $r_{on}$  and decreased with  $G_{cv}$ .

#### 2.2.4 Passive mixer linearity

The linearity of a passive mixer depends on the switching time of mixing transistors. Fast switching from the OFF-state to the ON-state provides a good linearity [35]. As presented before (Figure 2-1), passive mixer can operate either with square or sinusoidal LO waveforms. The conversion gain stays the same for both situations. However, square LO waveforms with sharp rising and falling edges allow a faster switching, which translate into a better linearity.

#### 2.2.5 Conventional CMOS passive mixer for millimeter-wave receivers

As discussed in chapter 1, with its 0 DC power consumption in the mixer core and high linearity, the conventional CMOS passive mixer is a good candidate to comply with the strong linearity requirement on radar receivers. Nevertheless, the low conversion gain of passive mixer is a main drawback regarding noise performances of the overall receiver. As already stated, the inherent upper limit of a passive mixer conversion gain is -4 dB, when the mixer is driven with a 50% duty cycle LO signal. Since the LNA gain is limited for receiver linearity purpose, the implementation of a passive mixer can lead to a low gain front-end. Finally, as the baseband variable gain amplifier exhibits a quite high input voltage noise [36], this low front-end gain has a strong impact on the NF of the receiver.

This issue is addressed in the next section showing how the conversion gain of the passive mixer can be improved while its good linearity is kept, by using a sampling passive mixer.

# 2.3 Sampling passive mixer principle

Passive mixer topologies based on the sampling principle can be considered to benefit from the advantages of passive mixer while enhancing the value of conversion gain. This section presents the sampling down-conversion principle and its comparison with conventional passive mixer principle detailed earlier.

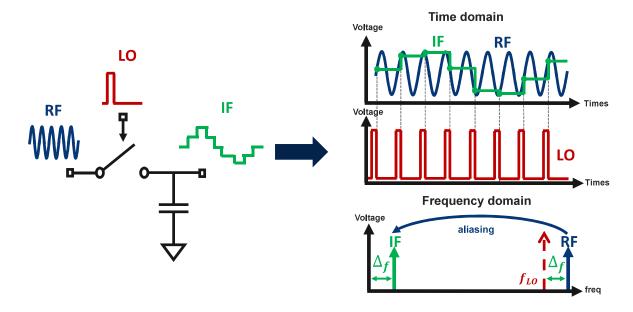

#### 2.3.1 Using sampling for down-conversion

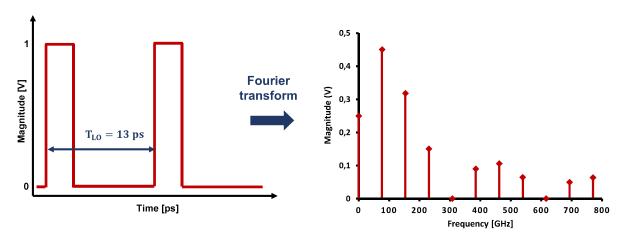

At low frequencies, the use of sampling for frequency down-conversion as in [37] is wide spread. The sample and hold circuit performing the frequency conversion relies on a switch and a capacitor as described in Figure 2-2. The switch is closed for a very short time for sampling the input voltage. Then the hold capacitor stores the sampled value while the switch is open. In an ideal sampling operation, every RF signal close to a sampling frequency harmonic ( $n.f_{LO}$ ) is translated at an  $f_{IF}$  of  $|f_{RF}-n.f_{LO}|$  by the sampling aliasing. This frequency translation is illustrated in Figure 2-2 for n = 1.

Figure 2-2: Sampling down-conversion principle.

The sampling can be interesting for down-conversion, because it allows a theoretically lossless frequency down-conversion with a LO frequency equal to  $f_{RF}/n$  close to the RF frequency (n=1) or close to an harmonic sub-multiple of the RF frequency. In this last situation, the only limitation to the frequency conversion results from the low pass filtering which is induced by the ON-state switch resistance and the hold capacitor.

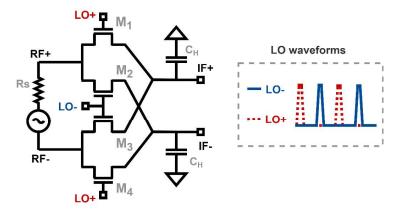

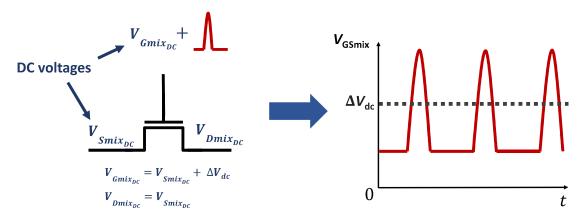

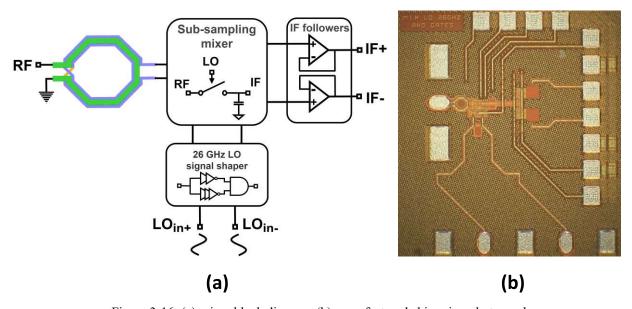

#### 2.3.2 Sampling passive mixer operating principle

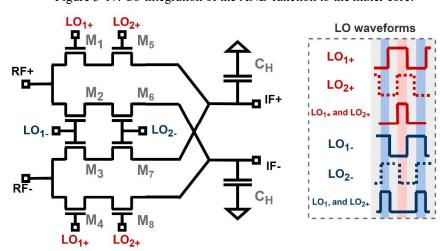

The conventional passive mixer operating principle described earlier can be improved by introducing the sampling operation. This way, the conversion gain is enhanced and a sub-harmonic conversion is possible as well. In order to turn the mixer into a voltage sampler, a low duty cycle square wave must be applied as the LO signal and the IF outputs must be loaded with a capacitance. This principle is developed in a double-balanced configuration in Figure 2-3. As in a sample and hold circuit, transistors are used as switches that are closed for a very short time for sampling the input voltage. The hold capacitors  $C_H$  store the sampled values when all switches are open.

Figure 2-3: Double-balanced sampling mixer.

At IF frequencies, the mixer acts as a low-pass  $C_H/g_c$  network where  $g_c$  is the mean channel conductance of transistors  $M_{1,2,3,4}$  over the LO period. Because of the passive mixer transparency regarding impedances, this network results in a high RF input impedance ([38], [39]) around each odd LO harmonics. A proper voltage conversion is enabled as soon as source impedance  $R_s$  is low enough (<< | $Z_{in}$ |).

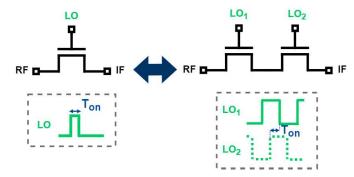

#### 2.3.3 Sampling mixer conversion gain

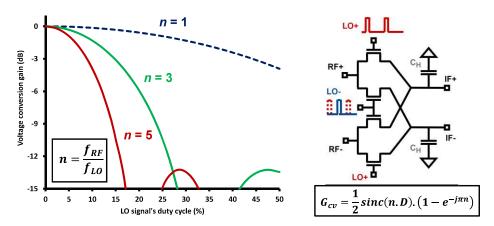

With a proper input voltage source and considering that  $M_{1,2,3,4}$  are conducting for a time  $\tau_{\text{on}}$  equal to  $D.T_{\text{LO}}$ , the voltage conversion gain of a sampling mixer is calculated as:

$$G_{cv} = \frac{1}{2} \operatorname{sinc}\left(\frac{f_{RF}}{f_{LO}}, D\right) \left(1 - e^{-j\pi \frac{f_{RF}}{f_{LO}}}\right) \text{ where } \operatorname{sinc}(x) = \frac{\sin(\pi x)}{\pi x}$$

(2-5)

The gain calculation method is similar as in [40]. According to (2-5),  $G_{cv}$  increases when the duty cycle D gets lower and tends toward 1 as D tends to 0. This formula also illustrates that with double-balanced structure, only RF signals around odd LO harmonics are down converted.

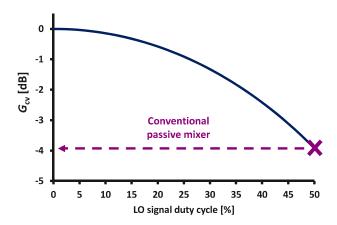

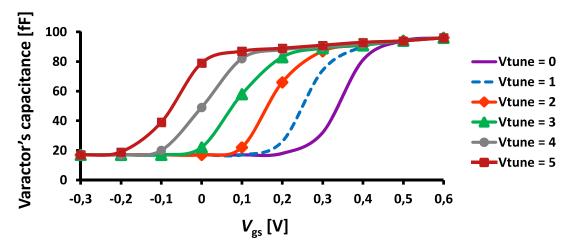

The conversion gain of a fundamental sampling mixer ( $n = f_{RF}/f_{LO} = 1$ ) for different duty cycles is illustrated in Figure 2-4. This figure shows that the  $2/\pi$  conversion gain limitation of a conventional CMOS voltage passive mixer can be broken with a sampling mixer, which conversion gain can ideally reach the value of 1 for very small LO duty cycles.

Figure 2-4: Conversion gain of a fundamental sampling mixer vs the LO signal duty cycle.

#### 2.3.4 Noise in sampling mixer

The conversion gain around each odd LO harmonic coming with the sampling behavior has an impact on the sampling mixer noise. The main noise contributors in sampling mixers are similar as in conventional passive mixers. The input noise aliasing described in [37] and the  $r_{on}$  thermal noise of the mixing transistors converted around  $f_{LO}$  and its harmonics remain the two main noise contributions to the mixer output noise. However, as sampling mixer presents a higher conversion gain than conventional passive mixer, the output voltage noise spectral densities are different. The output voltage noise spectral density due to the input noise conversion around LO harmonics can be calculated as [41]:

$$N_{alias} = 2.\sum_{n} N_{in}(n.f_{LO}).G_{cv}^{2}(n.f_{LO}).\alpha^{2}(n.f_{LO}) \text{ with } \alpha(n.f_{LO}) = \left| \frac{Z_{in}(n.f_{LO})}{Z_{in}(n.f_{LO}) + R_{s}} \right| (2-6)$$

In (2-6)  $N_{in}(n,f_{LO})$  represents the voltage noise spectral density at the mixer input around each LO harmonic. Each LO harmonics output noise contribution is multiplied by 2 because of the image frequency band.

To compute the output voltage noise spectral density added by the mixer, all  $r_{\rm on}$  thermal noise conversions around LO harmonics must be added [42]:

$$N_{th_{out}} = 2. N_R. \sum_{-\infty}^{\infty} G_{cv}^2(n. f_{LO})$$

with  $N_R = 2KTr_{on}$  (2-7)

$N_{\rm R}$  is the two-sided noise spectral density of the mixing transistor  $r_{on}$  resistance. A factor 2 is added in (2-7) as the  $r_{\rm on}$  resistance of each differential path (RF<sub>+</sub> and RF<sub>-</sub>) of the double-balanced mixer must be considered. Including the  $G_{\rm cv}$  expression of (2-5) in the calculation of the sum in (2-7) gives the following one-sided thermal noise spectral density:

$$N_{th_{out}} = \frac{4KTr_{on}}{D} \tag{2-8}$$

The calculation steps leading to this result are similar as in [42] and are given in annex. The equation (2-8) shows that the mixer thermal noise increases when the duty cycle D is decreased. This result is consistent with the increase of the conversion gain around  $f_{LO}$  and its harmonics.

If the mixer added thermal noise and the input noise conversion are only considered, the sampling mixer  $NF_{SSB}$  is:

$$NF_{SSB} = \frac{V_{\text{nmix}}^{2}}{N_{in}(f_{RF}). G_{c_{v}}^{2}(f_{RF}). \alpha(f_{RF})^{2}} \quad \text{with } \alpha(f) = \left| \frac{Z_{in}(f)}{Z_{in}(f) + R_{s}} \right|$$

(2-9)

$$= \frac{N_{th_{out}} + N_{alias}}{N_{in}(f_{RF}). G_{c_v}^2(f_{RF}). \alpha(f_{RF})^2}$$

(2-10)

In (2-9) and (2-10),  $N_{\rm in}(f_{\rm RF}).G_{\rm cv}^2(f_{\rm RF}).\alpha^2(f_{\rm RF})$  is the input RF frequency band converted noise. Except for the wideband applications, the input noise outside the  $f_{\rm RF}$  band is filtered by a narrow band matching network or LNA. Consequently, the input noise conversion for RF bands corresponding to LO harmonics becomes negligible. In this case,  $N_{\rm alias}$  become equal to  $2.N_{\rm in}(f_{\rm RF}).G_{\rm cv}^2(f_{\rm RF}).\alpha^2(f_{\rm RF})$  and the overall NF can be written as:

$$NF_{SSB} = 2 + \frac{\frac{4KTr_{on}}{D}}{N_{in}(f_{RF}). G_{cn}^{2}(f_{RF}). \alpha(f_{RF})^{2}}$$

(2-11)

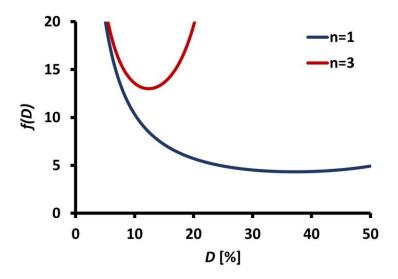

Since the converted thermal noise has a 1/D variation while  $G_{cv}$  has a sinc(n.D) variation (2-5), (2-11) shows that  $NF_{SSB}$  reach his lower value for the minimum of:

$$f(D) = \frac{1}{D.\,sinc^2(n.\,D)}$$

(2-12)

The function in (2-12) is plotted for n ratio of 1 and 3 in the Figure 2-5.

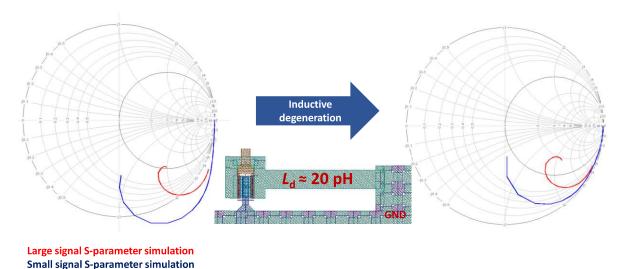

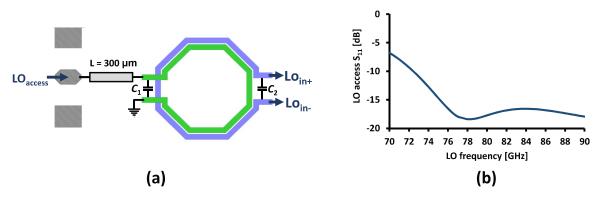

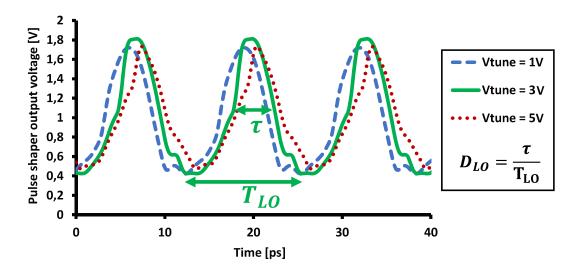

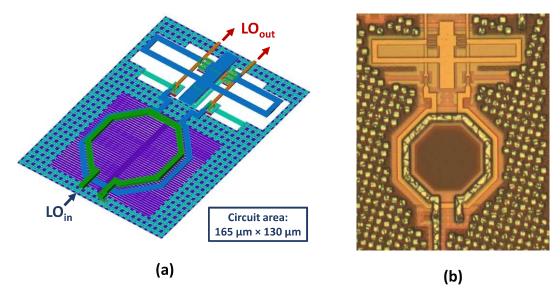

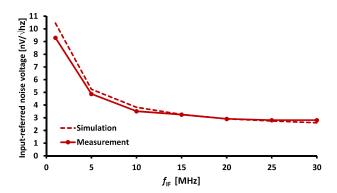

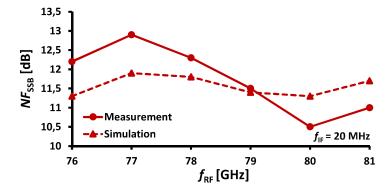

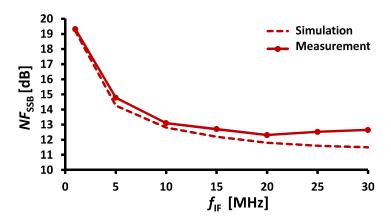

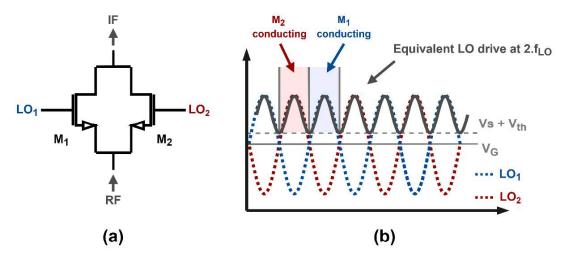

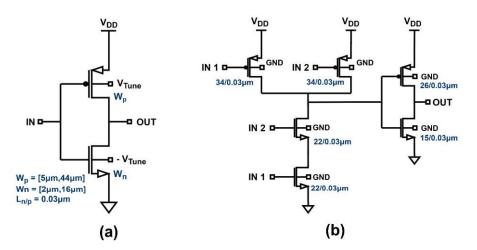

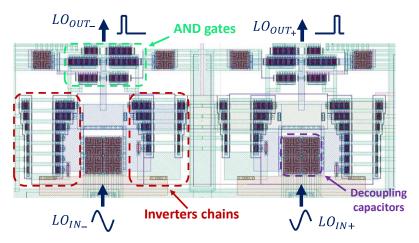

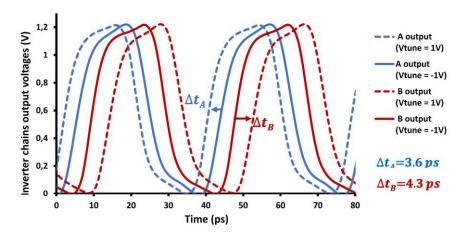

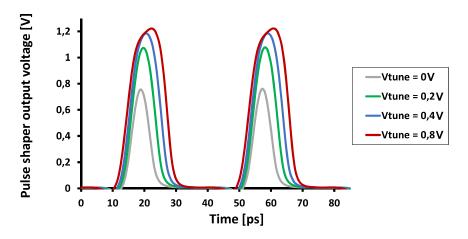

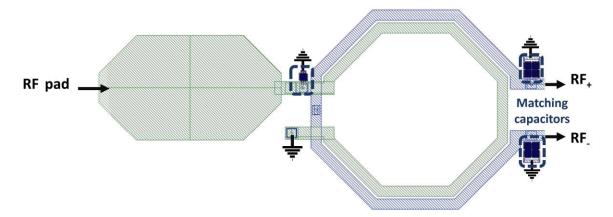

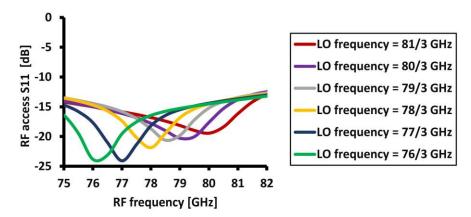

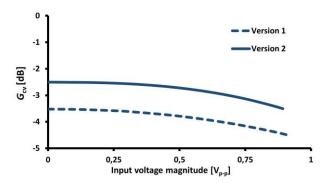

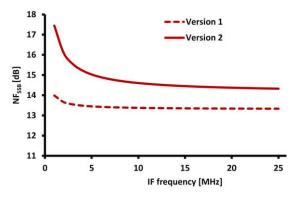

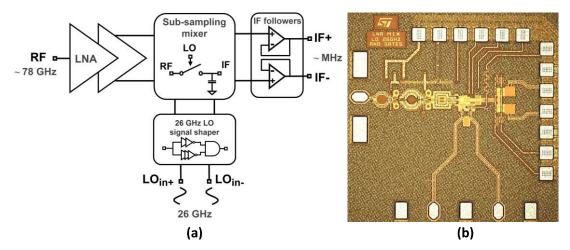

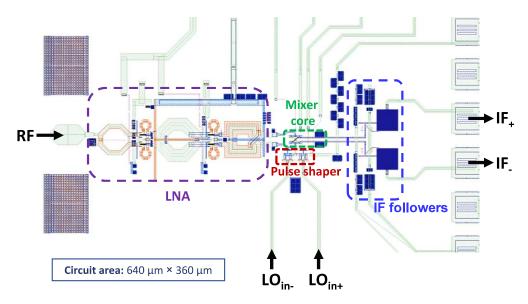

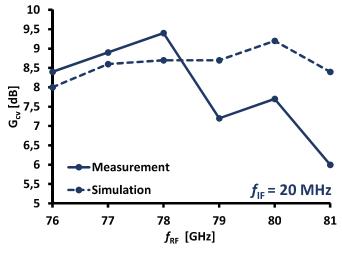

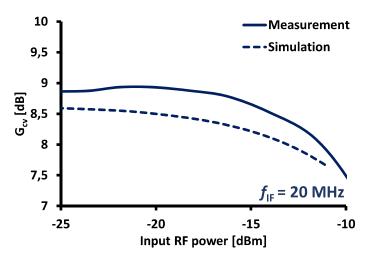

Figure 2-5 :plot of the f(D) function.